## **CODIPHY-** Composing On-Demand Intelligent PHYsical Layers

by

### Aveek Dutta

M.S., University of Colorado Boulder, 2008B.Tech., University of Kalyani, India, 2002

A thesis submitted to the Faculty of the Graduate School of the University of Colorado in partial fulfillment of the requirements for the degree of Doctor of Philosophy Department of Electrical, Computer and Energy Engineering

2013

### This thesis entitled: CODIPHY- Composing On-Demand Intelligent PHYsical Layers written by Aveek Dutta has been approved for the Department of Electrical, Computer and Energy Engineering

Prof. Dirk Grunwald

Prof. Douglas Sicker

Prof. Tim Brown

Prof. Fabio Somenzi

Dr. Joeseph Mitola III

Date \_\_\_\_\_

The final copy of this thesis has been examined by the signatories, and we find that both the content and the form meet acceptable presentation standards of scholarly work in the above mentioned discipline.

#### Dutta, Aveek (Ph.D., Electrical Engineering)

#### CODIPHY- Composing On-Demand Intelligent PHYsical Layers

Thesis directed by Prof. Dirk Grunwald

CODIPHY or Composing On-Demand Intelligent Physical Layers aims to solve two fundamental problems in practical cognitive radio networks: Collaboration between two radio physical layers (PHY) with varying capabilities to agree on a common communication protocol, using an ontology based description of the internal structure of the radio subsystems and secondly, provide a method to compose a functioning radio pipeline from a set of pre-compiled components, using the high-level representation provided by the ontology, to target heterogeneous platforms. CODIPHY isolates the various domains of radio engineering, but still allows sharing of domain knowledge to achieve the common goal of radio adaptation.

CODIPHY goes beyond the concept of "*knobs*" in cognitive radios, to decompose the radio pipeline and then build it back again to implement a different wireless protocol. To automate this process through collaborative learning is the goal of this thesis. Instead of solving the generic problem of collaboration for all waveforms and protocols, we focus on the most common family of waveform used in modern wireless systems and cognitive radio networks, Orthogonal Frequency Division Multiplexing (OFDM), and validate the methodology of CODIPHY by prototype implementations on heterogeneous radio platforms using HDLs and high level programming languages.

CODIPHY is the culmination of experiences gathered from radio prototyping for cognitive radio networks and is greatly influenced by MAC-PHY crosslayer research, where the radio is treated as a mutable entity rather than fixed in function. In this thesis, we present the steps required to realize the concept of CODIPHY, which range from the implementation of cognitive radio prototypes on FPGA to its application in design and evaluation of novel crosslayer protocols. These steps provide valuable insights to the requirements and formulation of CODIPHY. Therefore, CODIPHY is a multi-disciplinary effort that facilitates knowledge sharing among disparate areas of research. Dedication

To Dola and Adri

### Acknowledgements

First of all, I would like to thank my PhD advisor Prof. Dirk Grunwald for his support, advice and guidance throughout my graduate studies.

Would like to thank my research collaborator, Dola Saha for her invaluable contribution in developing and maintaining software drivers for the software defined radio that is one of the foundation pieces of my thesis. Also, like to thank her for collaborating on crosslayer research that has enabled me to propose new architectures for next generation physical layers.

Also, would like to thank all the members of my thesis committee, Prof. Douglas Sicker, Prof. Tim Brown, Prof. Fabio Somenzi and Dr. Joseph Mitola III for their insightful comments that has helped me enrich my research.

Thank you to Prof. Dipankar Raychaudhuri and Ivan Seskar of Rutgers University for their support and cooperation over the years.

And lastly, a big thank you to all of my family members, specially my parents for believing in me and my friends for their support and always standing beside me when required.

## Contents

## Chapter

| 1 | Intro | oduction  |                                         | 1  |

|---|-------|-----------|-----------------------------------------|----|

| 2 | Rela  | ted Wor   | k                                       | 15 |

| 3 | Phys  | sical Lay | ers: Implementation of OFDM transceiver | 24 |

|   | 3.1   | Inside    | the OFDM transceiver                    | 25 |

|   | 3.2   | Radio     | Platform and System Level Components    | 27 |

|   | 3.3   | Ethern    | et Module                               | 28 |

|   | 3.4   | SPI Se    | rial Interface                          | 29 |

|   | 3.5   | Baseba    | nd Module                               | 33 |

|   |       | 3.5.1     | Packet Detection                        | 33 |

|   |       | 3.5.2     | Carrier Frequency Offset Correction     | 39 |

|   |       | 3.5.3     | Long Correlation and Packet Timing      | 41 |

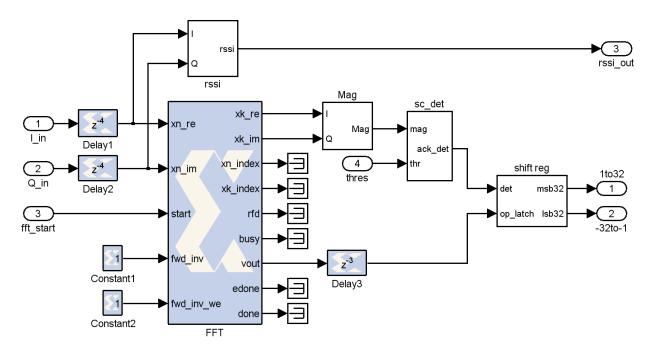

|   |       | 3.5.4     | De-prefix and FFT                       | 42 |

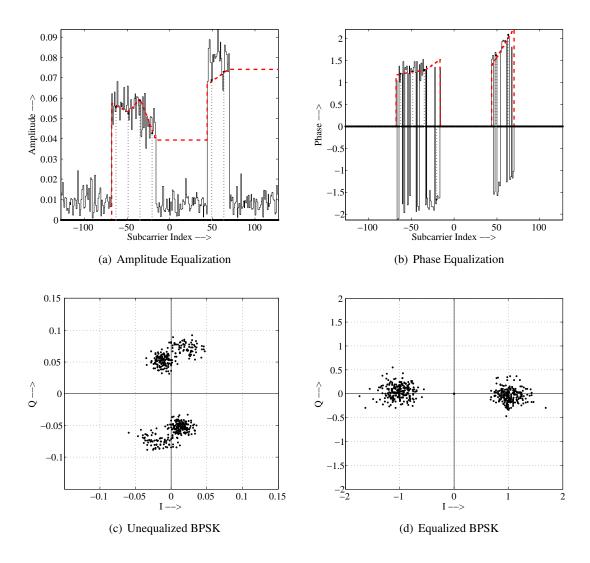

|   |       | 3.5.5     | Equalization                            | 43 |

|   |       | 3.5.6     | Demodulation                            | 48 |

|   |       | 3.5.7     | De-interleaver                          | 51 |

|   |       | 3.5.8     | De-puncture                             | 51 |

|   |       | 3.5.9     | Viterbi Decoder                         | 52 |

|   |       | 3.5.10    | De-scrambler                            | 52 |

|   |       | 3.5.11   | Signal Symbol Decoder                                             | 52 |

|---|-------|----------|-------------------------------------------------------------------|----|

|   | 3.6   | Perform  | nance Evaluation                                                  | 54 |

|   |       | 3.6.1    | Hardware Utilization                                              | 54 |

|   |       | 3.6.2    | Error performance                                                 | 57 |

|   |       | 3.6.3    | Latency                                                           | 57 |

| 4 | Intel | ligent P | hysical Layers: Specification for a SDCR                          | 59 |

|   | 4.1   | SDCR     | : Redefining the Radio PHY                                        | 61 |

|   |       | 4.1.1    | OFDM Transceiver : The Top Level                                  | 62 |

|   |       | 4.1.2    | Transmitter Kernels                                               | 66 |

|   |       | 4.1.3    | Receiver Kernels                                                  | 67 |

|   |       | 4.1.4    | Cognitive Sensing                                                 | 72 |

|   | 4.2   | Implen   | nentation and Results                                             | 73 |

|   |       | 4.2.1    | Implementation                                                    | 73 |

|   |       | 4.2.2    | Results                                                           | 74 |

|   | 4.3   | Efficie  | ncy and Generality                                                | 77 |

|   | 4.4   | Conclu   | sion                                                              | 78 |

| 5 | On-I  | Demand   | Intelligent Physical Layers: Crosslayer protocol design using SDR | 79 |

|   | 5.1   | SMAC     | K: SMart ACKnowledgment [7]                                       | 79 |

|   |       | 5.1.1    | SMACK - Reliable Link Layer Broadcasts                            | 80 |

|   |       | 5.1.2    | Implementing SMACK using SDR                                      | 82 |

|   |       | 5.1.3    | Conclusion                                                        | 85 |

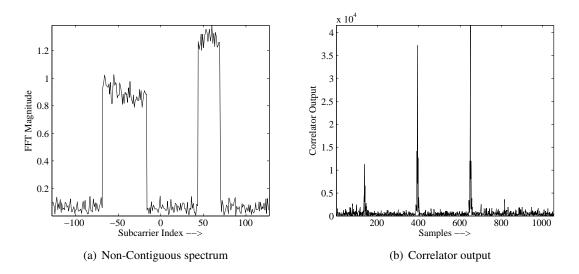

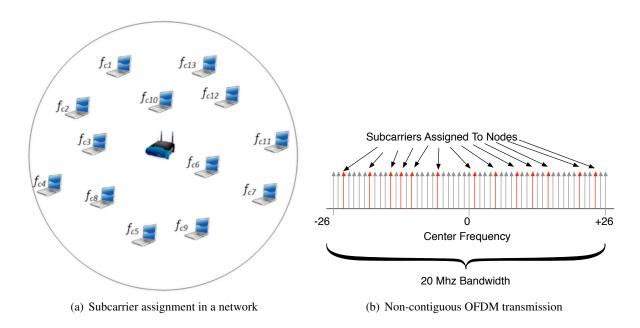

|   | 5.2   | Blind S  | Synchronization of NC-OFDM [61]                                   | 86 |

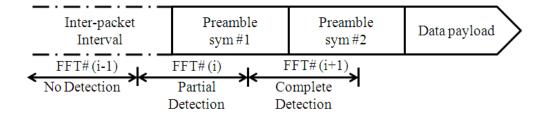

|   |       | 5.2.1    | OFDM Symbol Timing                                                | 90 |

|   |       | 5.2.2    | NC-OFDM Synchronizer                                              | 91 |

|   |       | 5.2.3    | FPGA Implementation                                               | 97 |

|   |       | 5.2.4    | Results and Implementation                                        | 99 |

vii

|   |     | 5.2.5     | Conclusion                                                           | 104 |

|---|-----|-----------|----------------------------------------------------------------------|-----|

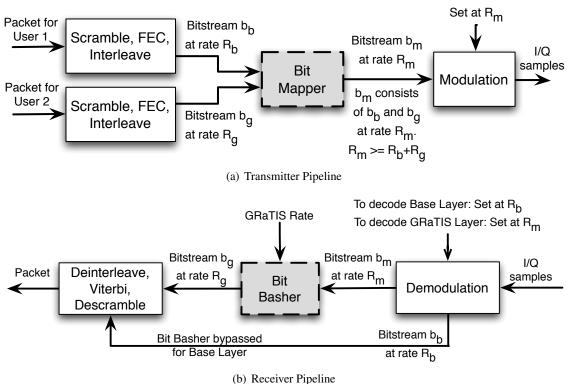

|   | 5.3 | GRaTIS    | S – Free Bits in the Air [100]                                       | 105 |

|   |     | 5.3.1     | GRaTIS: Free Bits                                                    | 107 |

|   |     | 5.3.2     | Hardware Implemention of GRaTIS                                      | 110 |

|   |     | 5.3.3     | Conclusion                                                           | 111 |

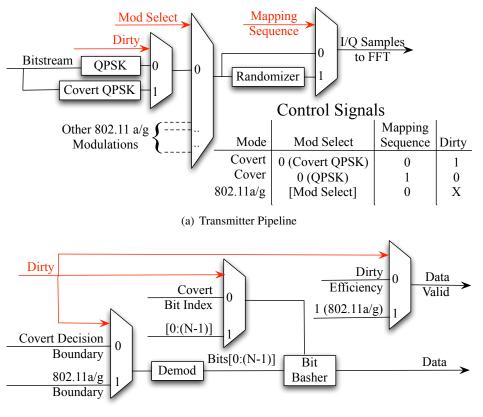

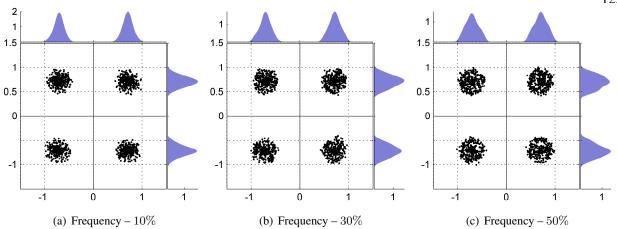

|   | 5.4 | Covert    | Communication through Dirty Constellations [102]                     | 114 |

|   |     | 5.4.1     | Dirty Constellation                                                  | 116 |

|   |     | 5.4.2     | Dirty Constellation on SDR                                           | 120 |

|   |     | 5.4.3     | Conclusion                                                           | 121 |

| 6 | COD | DIPHY : ] | Part 1 - Hierarchical Knowledge Representation System                | 123 |

|   | 6.1 | Knowle    | dge Representation System                                            | 125 |

|   |     | 6.1.1     | Specification level                                                  | 126 |

|   |     | 6.1.2     | Dataflow Level                                                       | 127 |

|   | 6.2 | Ontolog   | gy of the Radio Physical Layer                                       | 129 |

|   |     | 6.2.1     | Taxonomy of the Ontology                                             | 130 |

|   | 6.3 | Dataflo   | w representation of OFDM transceiver                                 | 136 |

|   | 6.4 | Ontolog   | gy for MAC-PHY Wireless crosslayer research                          | 137 |

| 7 | COD | OIPHY : 1 | Part 2 – Hierarchical Inferencing through Queries                    | 142 |

|   | 7.1 | Queryir   | ng at the System Level                                               | 143 |

|   | 7.2 | Queryir   | ng at the Subsystem Level                                            | 143 |

|   | 7.3 | Queryir   | ng at the Specification Level                                        | 144 |

|   | 7.4 | Queryir   | ng the Dataflow                                                      | 144 |

|   | 7.5 | Collabo   | ration using Hierarchical Inferencing for Crosslayer Implementations | 147 |

| 8 | COD | DIPHY : 1 | Part 3 – Composing the Radio PHY                                     | 151 |

|   | 8.1 | Compos    | sing software executable                                             | 152 |

|    | 8.2   | Composing hardware descriptions                                            | 154 |

|----|-------|----------------------------------------------------------------------------|-----|

|    | 8.3   | Code generation for OFDM transceiver                                       | 155 |

|    | 8.4   | Dataflow based PHY adaptation for Crosslayer Implementations               | 157 |

| 9  | Com   | paring CODIPHY With Other Related Techniques                               | 160 |

| 10 | Conc  | clusion                                                                    | 162 |

| Bi | bliog | raphy                                                                      | 164 |

| A  | ppend | lix                                                                        |     |

| A  | Previ | iously Published Content                                                   | 173 |

| B  | Auto  | generated M-Code for synthesizing ProgMod subsystem                        | 174 |

| С  | Auto  | generated C Code for software implemention of the <i>ProgMod</i> subsystem | 194 |

ix

# Tables

## Table

| 3.1 | Radio configuration specifications 30                               |

|-----|---------------------------------------------------------------------|

| 3.2 | Hardware utilization of the complete radio system                   |

| 3.3 | Hardware utilization of the transmitter subsystem                   |

| 3.4 | Hardware utilization of the receiver                                |

| 3.5 | Throughput and SNR requirements for 802.11a/g data rates            |

| 4.1 | Configurations supported by the SDCR 73                             |

| 4.2 | Transceiver hardware utilization in Virtex-IV FPGA                  |

| 5.1 | NC-OFDM parameters                                                  |

| 5.2 | Default setting for simulation parameters                           |

| 5.3 | NC-OFDM correlator utilization in Virtex - IV                       |

| 5.4 | Throughput and SNR requirements for 802.11a/g and CODIPHY rates     |

| 6.1 | Ontology of the transmitter                                         |

| 6.2 | Ontology of the receiver                                            |

| 7.1 | Querying the dataflow of the Packet Detector subsystem              |

| 7.2 | Hierarchical Inferencing using Queries                              |

| 8.1 | Lines of generated C Code from ontology                             |

| 8.2 | Hardware Utilization of the synthesized OFDM transmitter subsystems |

| 83  | Hardware Utilization of the synthesized OFDM receiver subsystems       |   |   |   |   |   |   |   |     |     |   |   |   | 156 |

|-----|------------------------------------------------------------------------|---|---|---|---|---|---|---|-----|-----|---|---|---|-----|

| 0.5 | That a ware e different of the synthesized of Divi receiver subsystems | • | • | • | • | • | • | • | • • | • • | • | • | • | 150 |

# Figures

# Figure

| 1.1  | Spectrogram captured using a vector signal analyzer showing over-the-air transmission of            |    |

|------|-----------------------------------------------------------------------------------------------------|----|

|      | multiple packets using non-contiguous OFDM from a SDCR transmitter. Packets are trans-              |    |

|      | mitted in a way to resemble the University of Colorado at Boulder logo, using non-contiguous        |    |

|      | subsets of subcarriers ranging between $[-27 \text{ and } +27]$ . The maximum possible signal band- |    |

|      | width is $16.875MHz$ .                                                                              | 2  |

| 3.1  | OFDM spectrum with frequency selective fading                                                       | 26 |

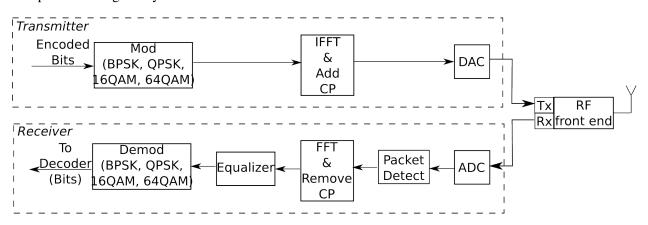

| 3.2  | A generic OFDM transceiver                                                                          | 27 |

| 3.3  | Software define radio platform at University of Colorado Boulder                                    | 28 |

| 3.4  | Top-level schematic for the OFDM prototype                                                          | 29 |

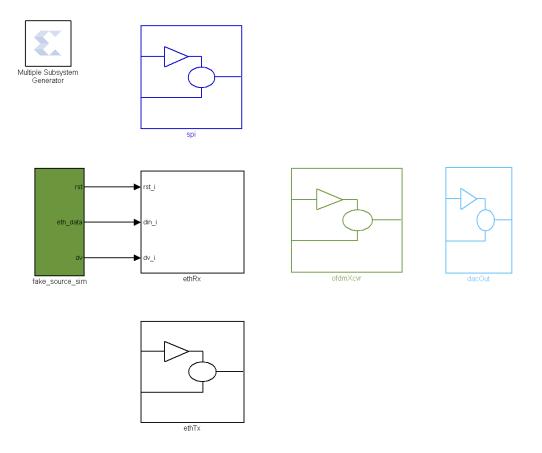

| 3.5  | Ethernet receiver                                                                                   | 31 |

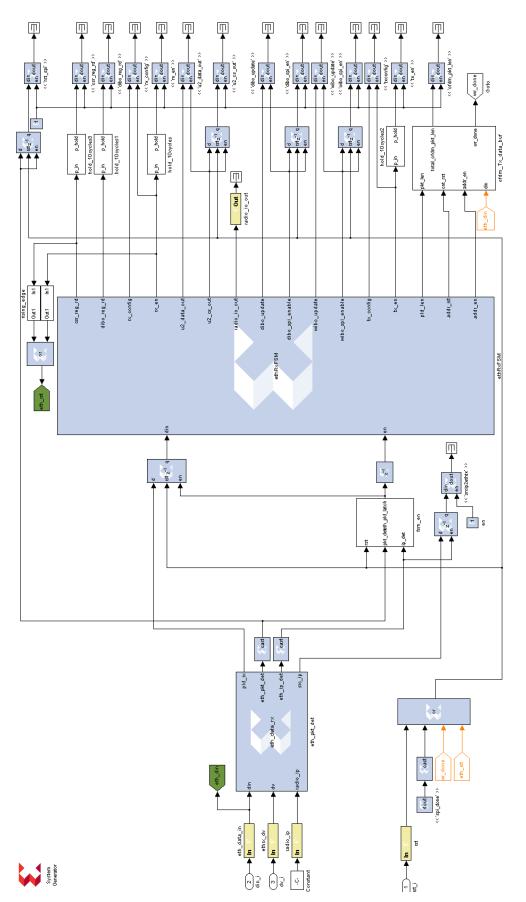

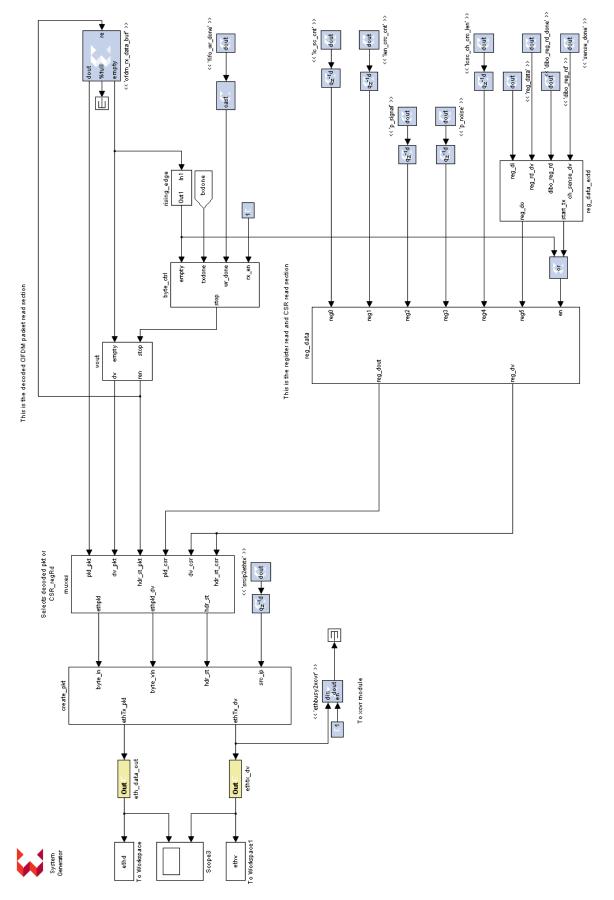

| 3.6  | Ethernet transmitter                                                                                | 32 |

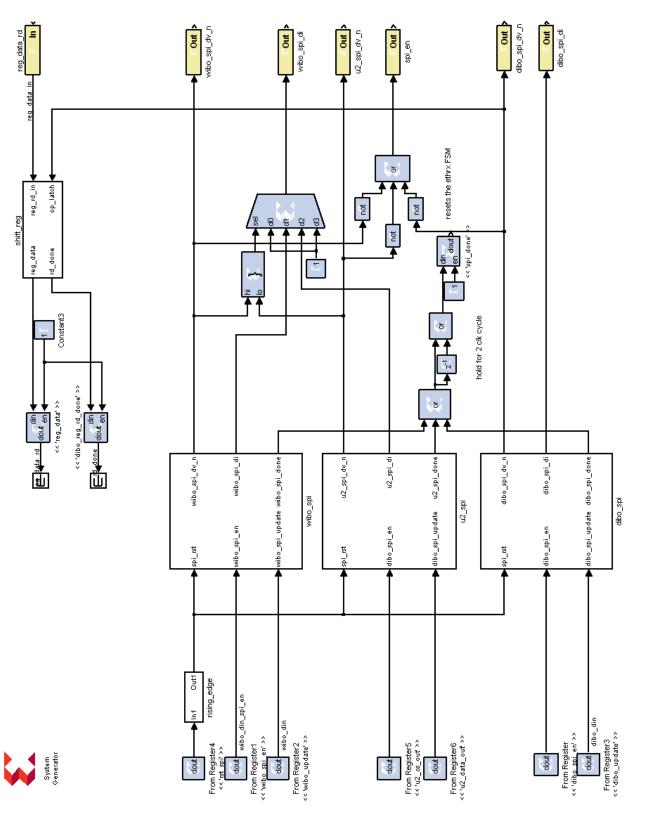

| 3.7  | Serial SPI interface                                                                                | 34 |

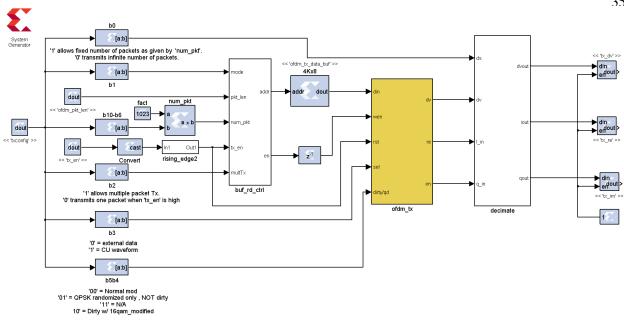

| 3.8  | OFDM transmitter top-level                                                                          | 35 |

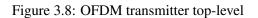

| 3.9  | OFDM transmitter subsystems                                                                         | 35 |

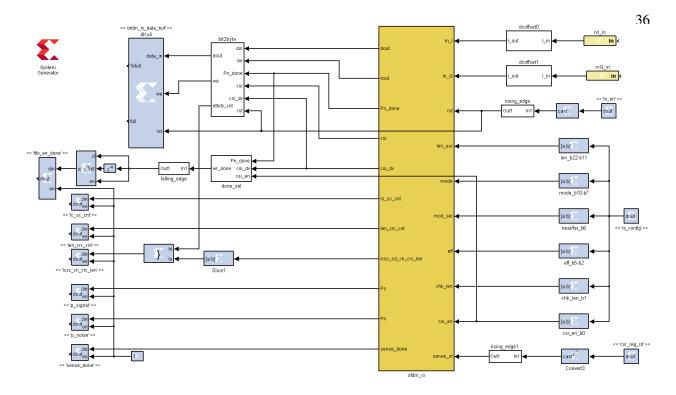

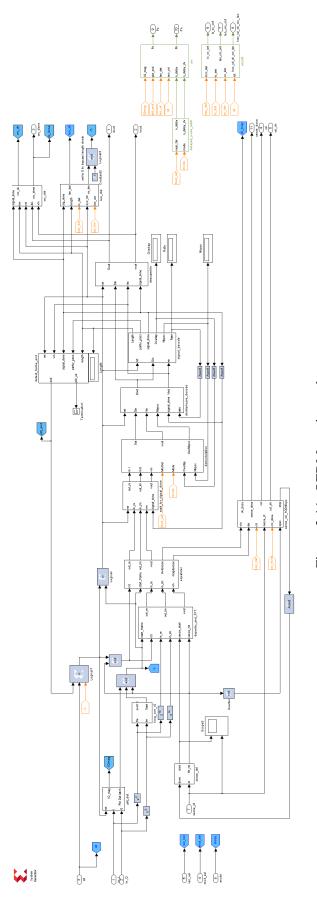

| 3.10 | OFDM receiver top-level                                                                             | 36 |

| 3.11 | OFDM receiver subsystems                                                                            | 37 |

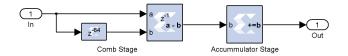

| 3.12 | Single stage CIC filter                                                                             | 38 |

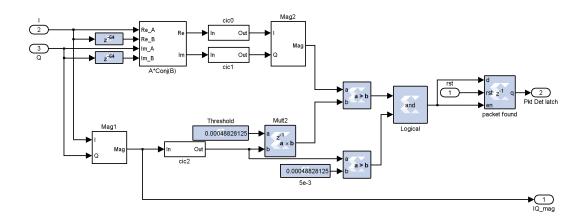

| 3.13 | OFDM packet detector                                                                                | 38 |

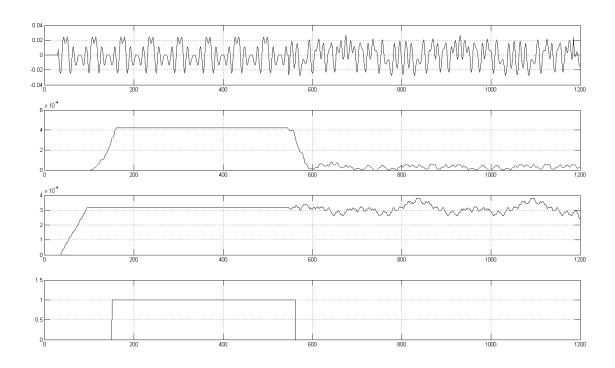

| 3.14 | Packet detector output                                  | 38 |

|------|---------------------------------------------------------|----|

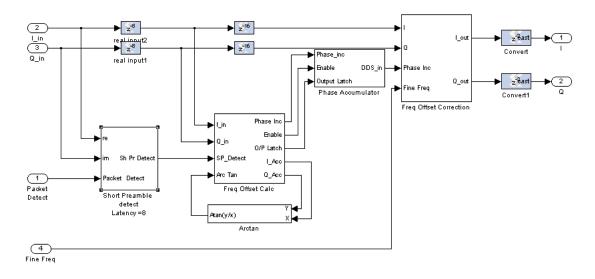

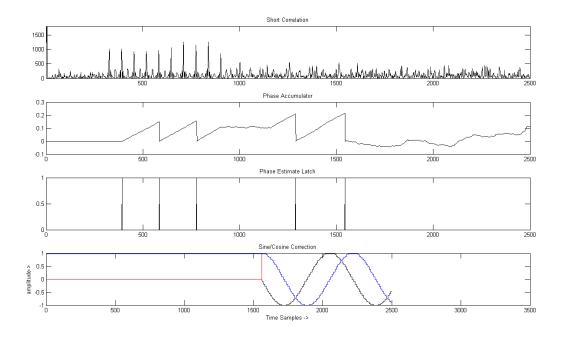

| 3.15 | Carrier frequency offset block                          | 40 |

| 3.16 | Carrier frequency offset correction                     | 40 |

| 3.17 | Long correlation using <i>sign</i> bit                  | 42 |

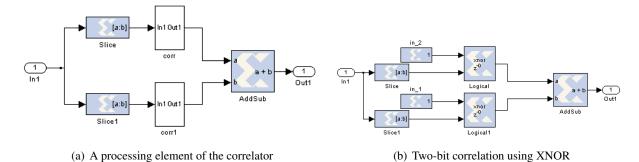

| 3.18 | Long correlator output                                  | 43 |

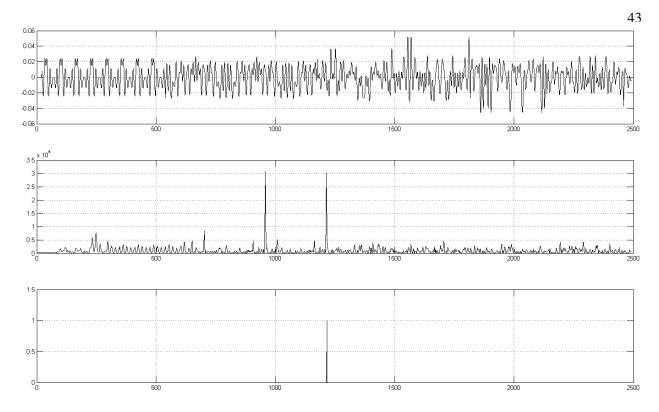

| 3.19 | De-prefix and FFT subsystem                             | 43 |

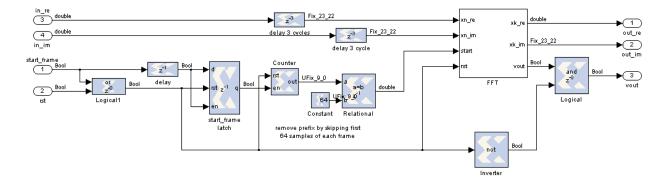

| 3.20 | Pilot arrangement in OFDM                               | 44 |

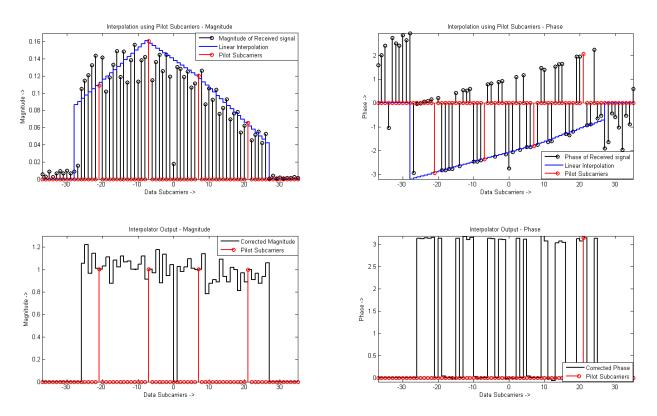

| 3.21 | Linear interpolation equalizer                          | 46 |

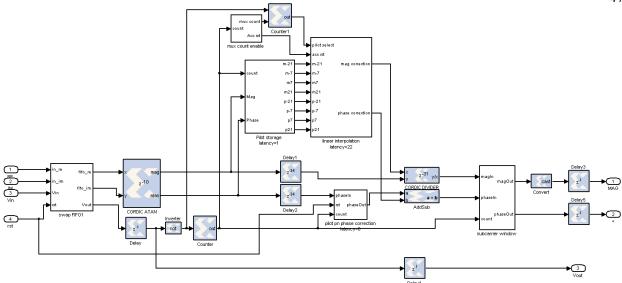

| 3.22 | Interpolator using channel estimates at pilot locations | 47 |

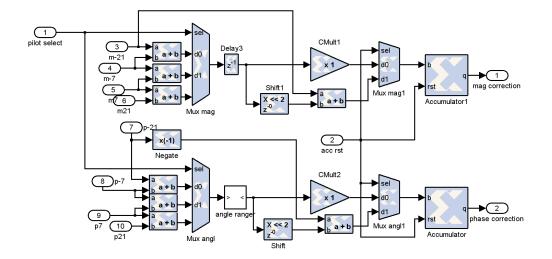

| 3.23 | Linear interpolation for phase and magnitude correction | 48 |

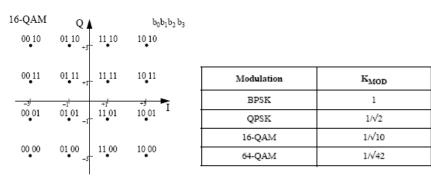

| 3.24 | Decision boundaries                                     | 49 |

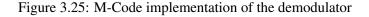

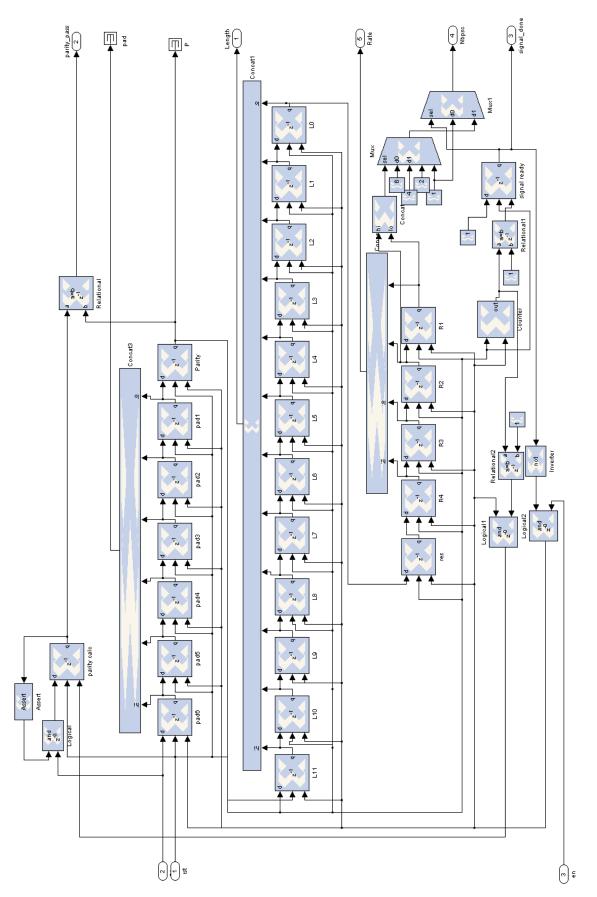

| 3.25 | M-Code implementation of the demodulator                | 50 |

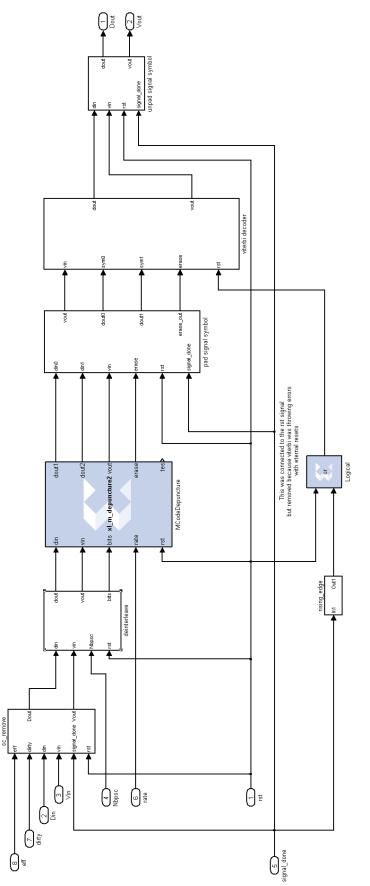

| 3.26 | De-interleaver, De-puncture and Viterbi decoder         | 53 |

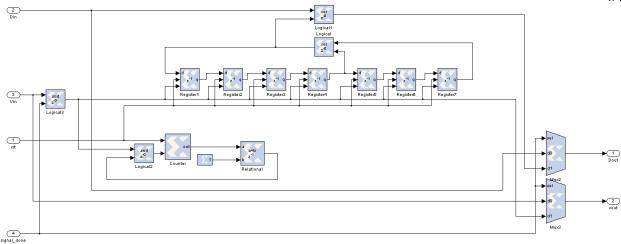

| 3.27 | De-scrambler                                            | 54 |

| 3.28 | Signal symbol decoder                                   | 55 |

| 4.1  | OFDM transceiver subsystems                             | 61 |

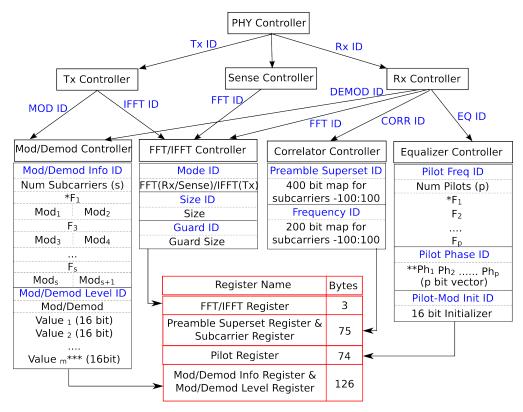

| 4.2  | PHY controller                                          | 63 |

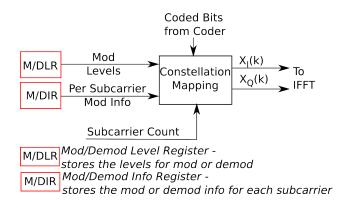

| 4.3  | Programmable modulator subsystem                        | 66 |

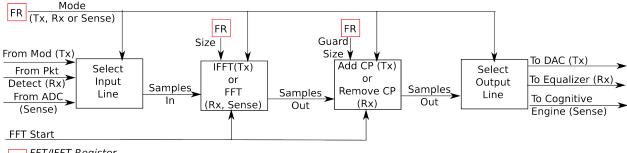

| 4.4  | Programmable FFT or IFFT subsystem                      | 66 |

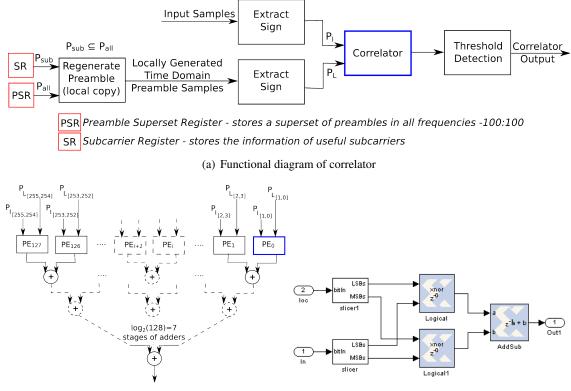

| 4.5  | Programmable correlator                                 | 68 |

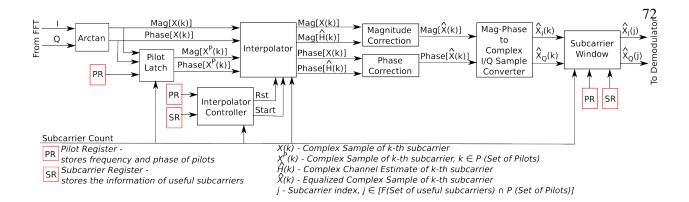

| 4.6  | Programmable equalizer                                  | 71 |

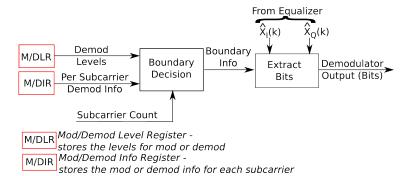

| 4.7  | Programmable demodulator                                | 72 |

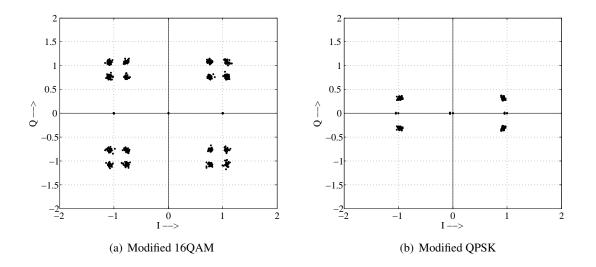

| 4.8  | Programmable constellations using SDCR                  | 74 |

| 4.9  | Programmable correlator input and output                | 75 |

| 4.10 | Equalizer performance                                   | 76 |

| 5.1  | Schematic illustration of ACKs using OFDM               | 80 |

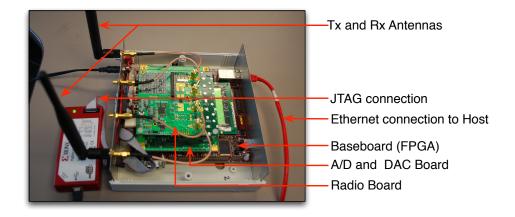

| 5.2  | Nallatech boards with radios and antennas                                                     |

|------|-----------------------------------------------------------------------------------------------|

| 5.3  | Design for the detecting ACK at AP                                                            |

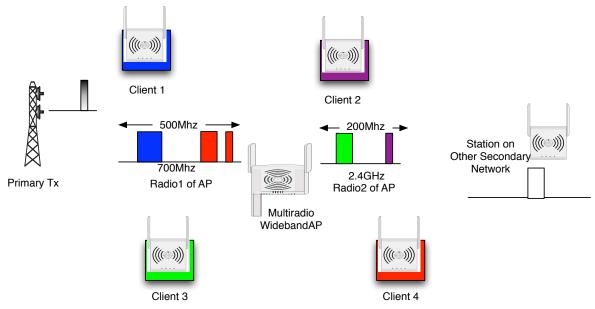

| 5.4  | Spectrum sharing in wideband cognitive radio network: An example scenario. Secondary          |

|      | network, consisting of an AP and four clients, is coexisting in presence of primary and other |

|      | secondary networks. The AP has two radios of different bandwidth, tuned to two different      |

|      | center frequencies, and is communicating over variable width NC-OFDM                          |

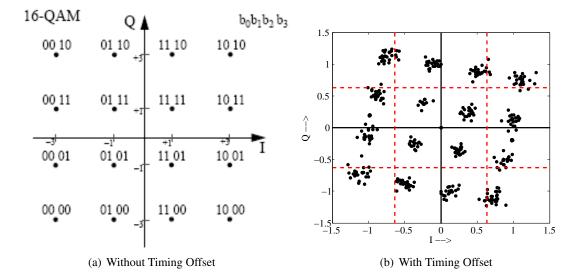

| 5.5  | Effect of symbol timing offset: 16QAM constellation after equalization at SNR = 15.5 with     |

|      | multi-path fading and a timing offset of $(-8)$ samples. The decoding regions are shown by    |

|      | the red dotted lines                                                                          |

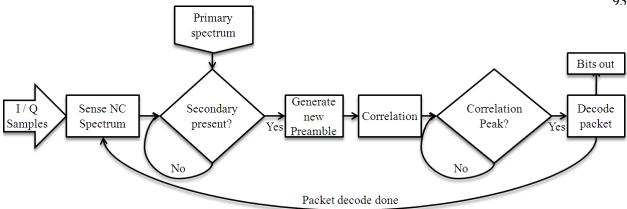

| 5.6  | NC-OFDM synchronization pipeline                                                              |

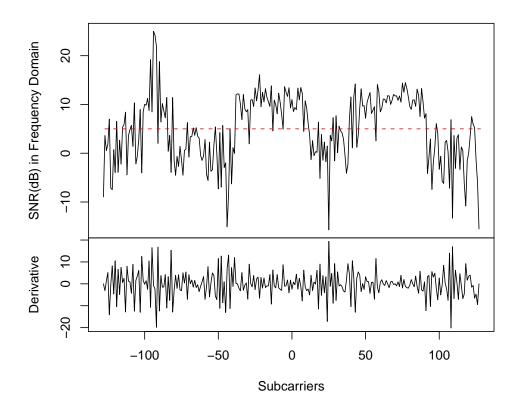

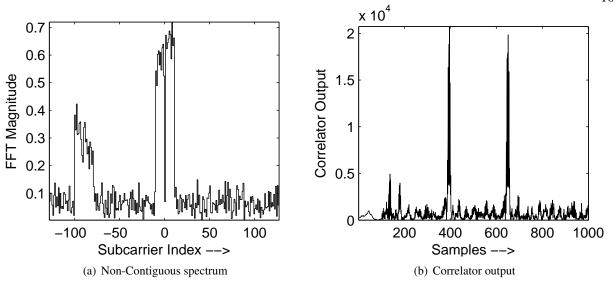

| 5.7  | Spectrum detection                                                                            |

| 5.8  | NC-OFDM Waveform - Primary occupancy is subcarriers $[-95:-91]$ and for secondary it          |

|      | is [-38:11], [40:89]                                                                          |

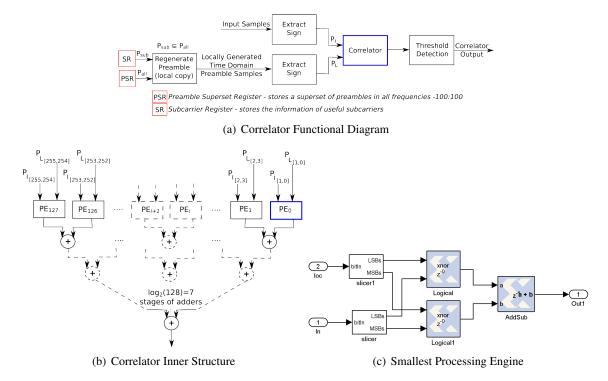

| 5.9  | FPGA implementation of a programmable correlator                                              |

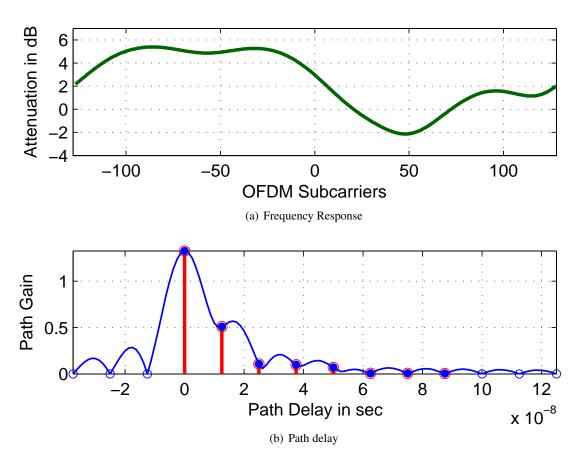

| 5.10 | Multipath channel response                                                                    |

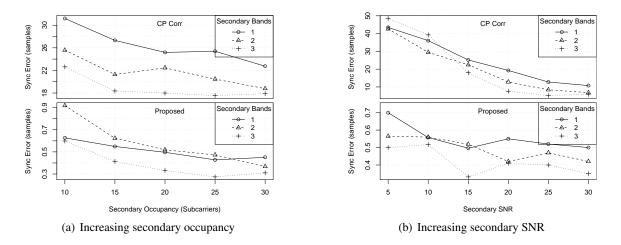

| 5.11 | Comparison with CP-based correlation                                                          |

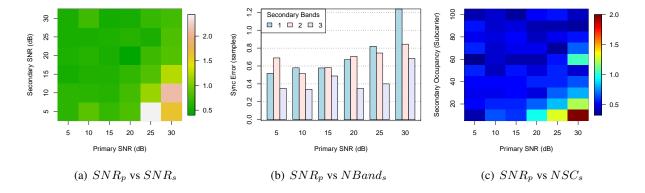

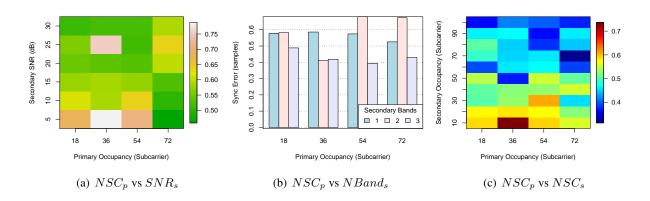

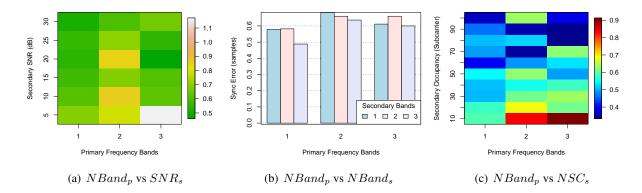

| 5.12 | Average synchronization error (in samples) with increasing primary SNR                        |

| 5.13 | Average synchronization error (in samples) with increasing primary occupancy 102              |

| 5.14 | Average synchronization error (in samples) with increasing primary bands                      |

| 5.15 | Programmable correlator input and output                                                      |

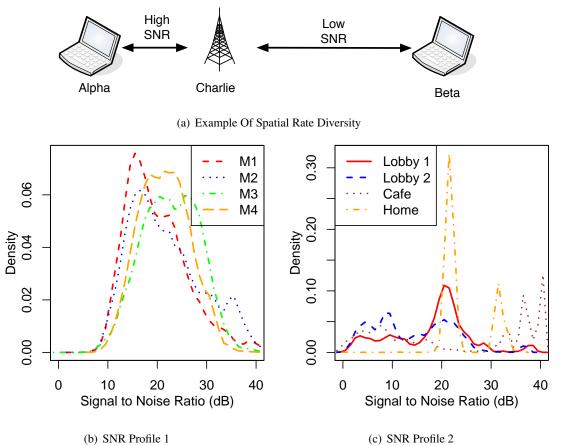

| 5.16 | Variation of SNR due to spatial diversity in 802.11a/g networks. Profile 1: Measured indoors  |

|      | by 4 packet sniffers at SIGCOMM 2008 [101] Profile 2: Measured indoors in common areas        |

|      | around a university cafe and lobbies and also in home networks                                |

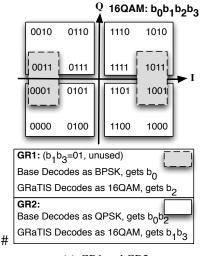

| 5.17 | Encoding and decoding of GRaTIS derived from standard 802.11a/g constellations. Rectan-       |

|      | gular regions show the transmitted cluster and the corresponding decision boundary for the    |

|      | base layer                                                                                    |

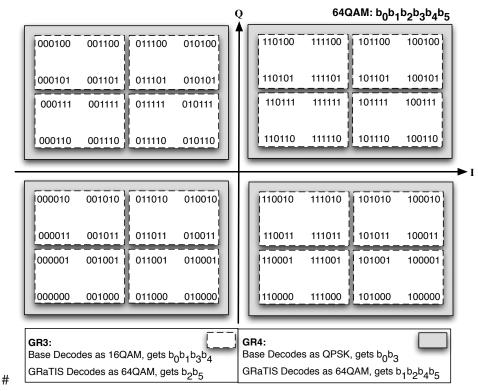

| 5.18 | Transceiver pipeline for GRaTIS - shaded subsystems show additional processes required    |

|------|-------------------------------------------------------------------------------------------|

|      | for GRaTIS                                                                                |

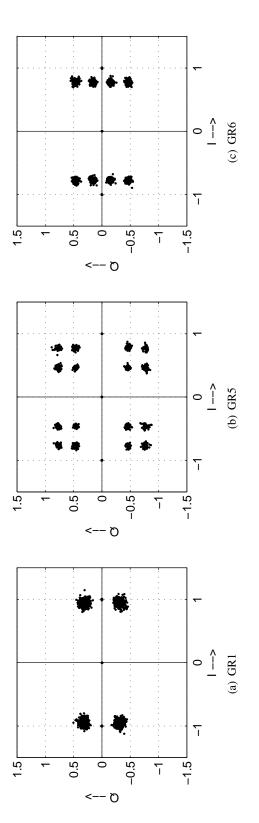

| 5.19 | Various GRaTIS constellations transmitted using the SDR prototype                         |

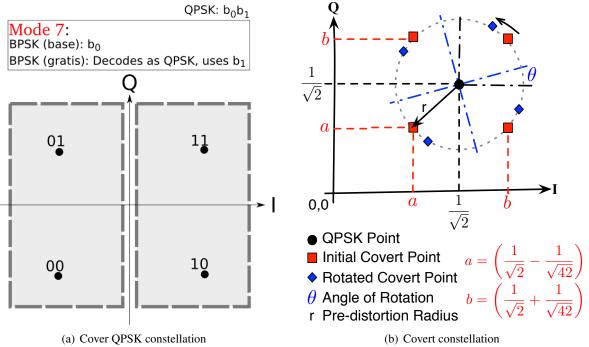

| 5.20 | Encoding Dirty Constellation                                                              |

| 5.21 | Constellation without random pre-distortion of the QPSK points and using existing 16QAM   |

|      | points to map the joint covert constellations                                             |

| 5.22 | SDR prototype using Virtex-V FPGA                                                         |

| 5.23 | Mod/Demodulator for Dirty Constellation                                                   |

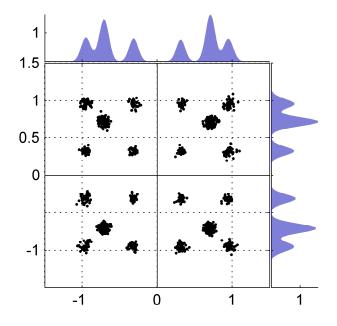

| 5.24 | Examples of over-the-air transmission of Dirty Constellations with varying embedding fre- |

|      | quency using the SDR prototype                                                            |

| 6.1  | CODIPHY: A system level view                                                              |

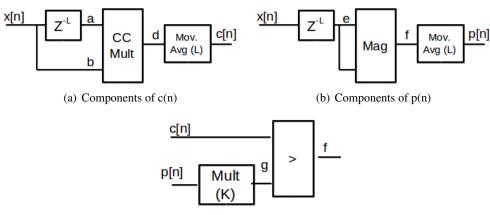

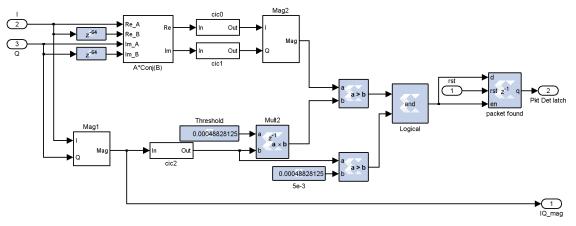

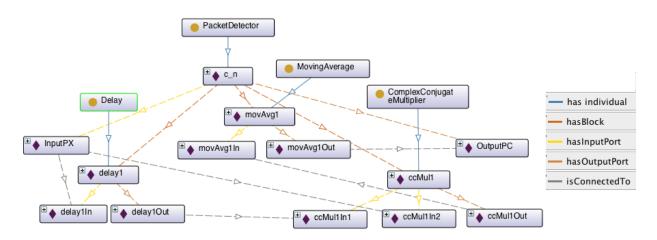

| 6.2  | Components derived from packet detection unit                                             |

| 6.3  | Packet Detector using CIC filters                                                         |

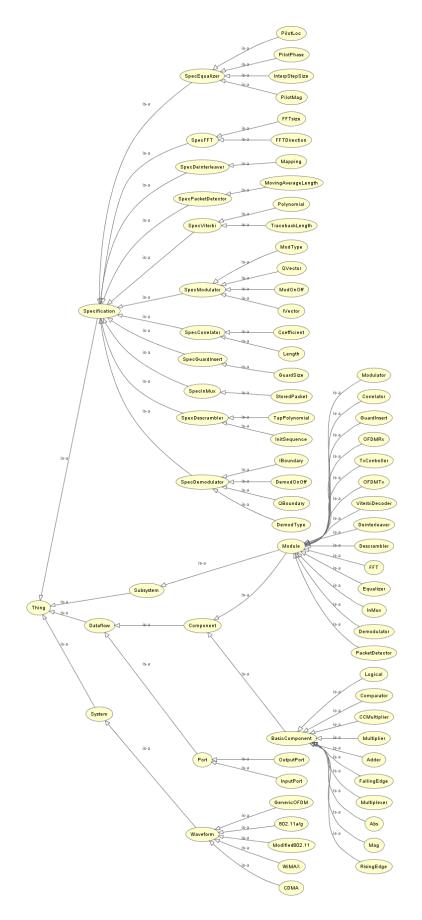

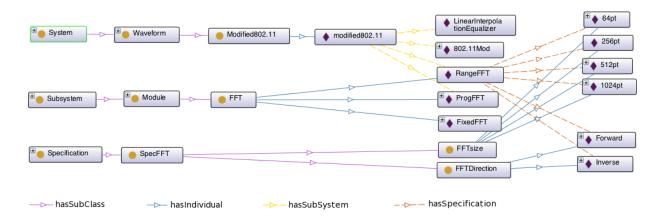

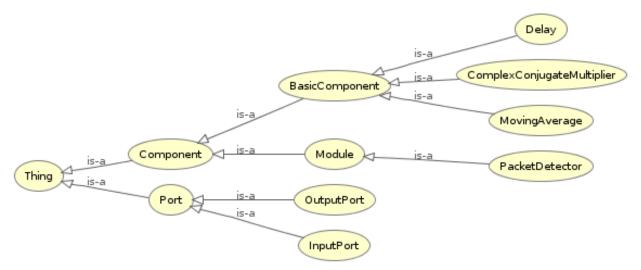

| 6.4  | Classes in the OFDM PHY ontology                                                          |

| 6.5  | Relationship between different level of the Knowledge representation system using object  |

|      | properties                                                                                |

| 6.6  | Classes in the Packet Detector ontology                                                   |

| 6.7  | Dataflow of the Packet Detector subsystem                                                 |

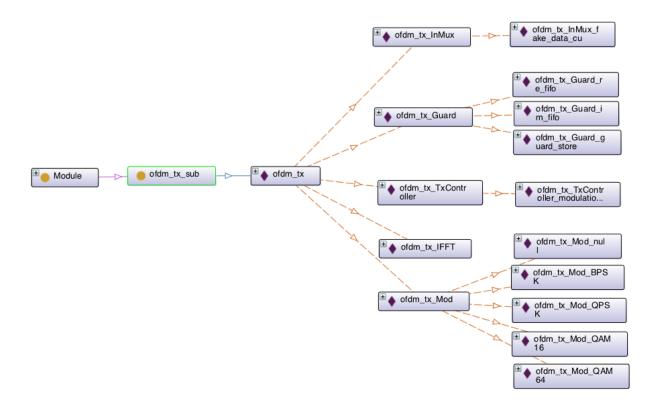

| 6.8  | Dataflow Hierarchy of OFDM Transmitter                                                    |

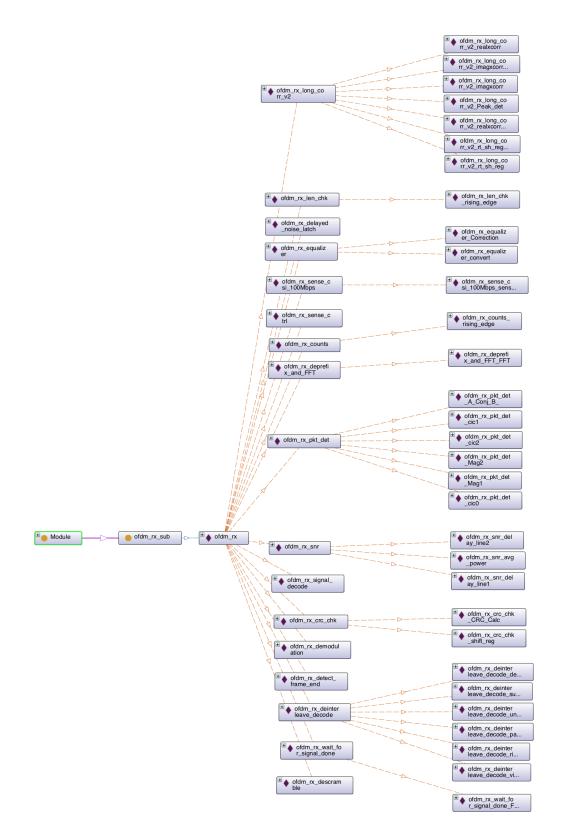

| 6.9  | Dataflow Hierarchy of OFDM Receiver                                                       |

| 6.10 | Example MAC-PHY Crosslayer Protocol in wireless networks                                  |

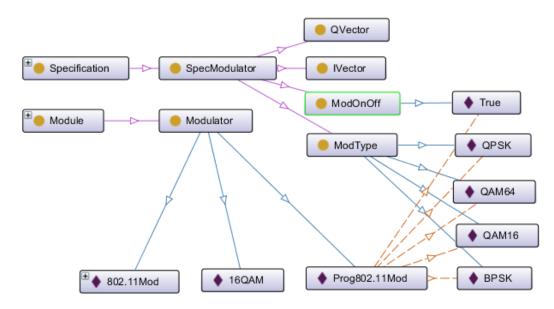

| 6.11 | Partial Ontology of the SMACK protocol. The Modulator is included in the knowledge base   |

|      | at the Subsystem and the Specification levels                                             |

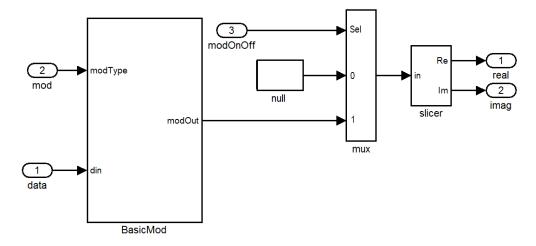

| 7.1  | Block Diagram of the modulator for SMACK                                                  |

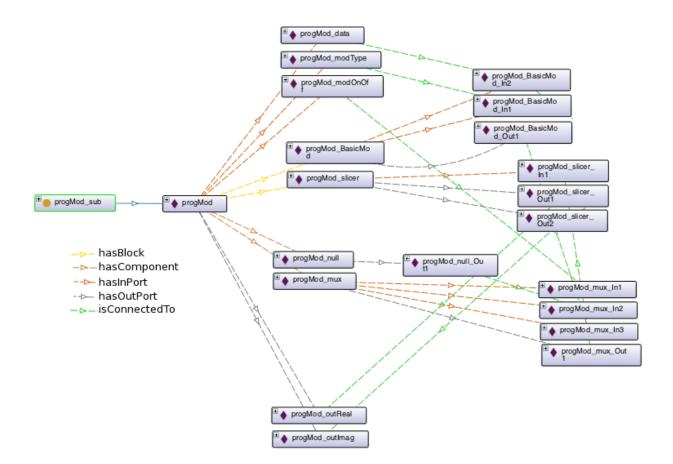

| 7.2  | Dataflow ontology of the modulator for SMACK                                              |

| 8.1 | Generated C Code for Packet Detector subsystem                                        |

|-----|---------------------------------------------------------------------------------------|

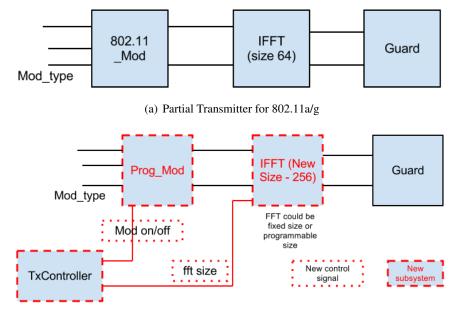

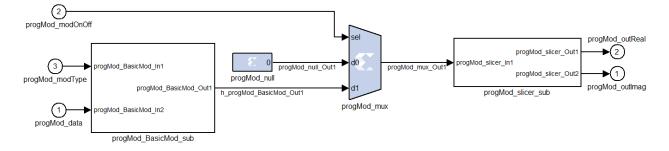

| 8.2 | <i>ProgMod</i> subsystem synthesized from ontology in figure 6.11                     |

| 8.3 | Performance comparison of HW and SW implementations for the <i>ProgMod</i> module 159 |

### Chapter 1

### Introduction

Radio Physical (PHY) layer is the interface to the transmission medium and is responsible for reliable communication link. The main components of the PHY layer are the radio front-end, the baseband processor and the interface to the higher layers along with a control framework. The baseband processor is responsible for the core signal processing tasks required to decode a packet. Modern high speed applications require high throughput PHY layers that contain complex Digital Signal Processing (DSP) functions to ensure reliability. The complexity of these DSP subsystems largely depend on the type of waveform supported by a particular PHY.

For a long time, the radio PHY has been shielded from the networking research community, primarily because those are typically built as fixed-function ASICs with very little insight into the internal operations of the underlying processing elements. The Atheros chipset based wireless network cards along with the MadWiFi driver [1] was one of the earliest examples of exposing PHY specific features to be controlled using software drivers. This new feature spawned an entire body of crosslayer research, which focused on optimizing the Medium Access Control (MAC) layer and the PHY layer jointly to improve network functions. This was certainly a new frontier in wireless research. Researchers now have access to certain low-level features like Received Signal Strength Indicator (RSSI), transmit power, data-rate algorithms, etc. [2, 3]. However, it was quickly realized that these functionalities were not enough and the need for a more flexible solution for research was established. GNURadio [4] was the first of its kind that allowed researchers to perform PHY layer processing using software that runs on general purpose processors. This platform further opened up the PHY layer to the researchers. Being a flexible software based processing,

GNURadio offered unforeseen gains in network protocols, at least from experiments and testbeds. Since all the signal processing is performed in software, it is much slower compared to the PHY time budgets for common wireless protocols. Therefore, it is not meant to be a replacement of commercial products, but offered a lucrative alternative for research and experimentation.

In order to pursue PHY layer enabled research, a highly programmable PHY that is fast enough to meet protocol time budgets is required. Therefore, an experimental prototype is a primary requirement for the research community that can provide more practical experimental testbeds with realistic results. The need for flexible PHY is further intensified with the advent of Cognitive Radios.

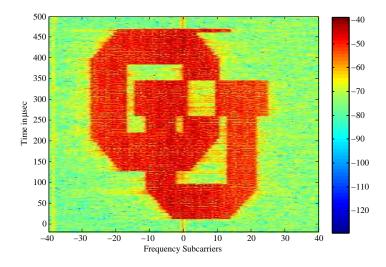

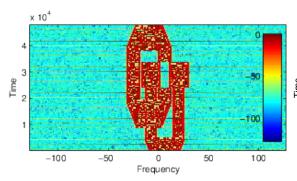

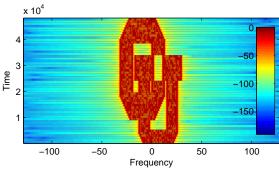

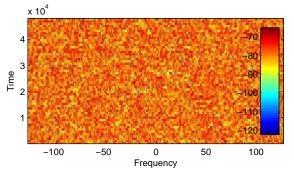

Figure 1.1: Spectrogram captured using a vector signal analyzer showing over-the-air transmission of multiple packets using non-contiguous OFDM from a SDCR transmitter. Packets are transmitted in a way to resemble the University of Colorado at Boulder logo, using non-contiguous subsets of subcarriers ranging between [-27 and +27]. The maximum possible signal bandwidth is 16.875MHz.

Cognitive Radio (CR) is an emerging wireless networking technology that is generally characterized as "adapting to an environment" in order to improve network performance. Equally important, most cognitive radios are envisioned to use Dynamic Spectrum Access (DSA) to make use of fractured available spectrum. The use of multiple disjoint spectral bands greatly complicate the tasks the radio encounters — for example, now correlators, used to determine if a signal is in transmission, must look up across multiple bands. Figure 1.1 shows an example of a cognitive radio transmission over multiple sub-bands of varying width. Transmissions like this require unprecedented fine-grained programming at the radio PHY. This further expands the design space of radios that leads to the paradigm of Software Defined Cognitive Radios or SDCR. There are many ways to control and configure such an interface. A common method, which we explored for non-contiguous waveform [5], specifies an interface with different parameters that control specific aspects of the waveform. Systems such as Software Communication Architecture (SCA) provide mechanisms to communicate the waveform configuration of one radio system to another. Thus, it is evident that next generation radio PHY requires many "tuning knobs" to control the various facets of the waveform. Systems based on tuning knobs can implement many different radio waveforms, but they are fundamentally limited and cannot radically change the PHY layer, even on hardware platforms where that is technically possible. Recent research [6, 7, 8] has shown that the performance of modern wireless protocols can be greatly improved by jointly optimizing the MAC and the PHY layer or by changing the way the PHY layer is used. These cross-layer and flexible PHY techniques require adaptation of the PHY, to the changing requirements of the protocol. These new concepts in wireless networking is further facilitated by new waveform technologies like the Orthogonal Frequency Division Multiplexing (OFDM), which in turn influence the design and architecture of the flexible PHY layer.

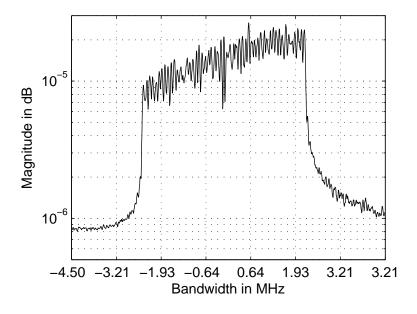

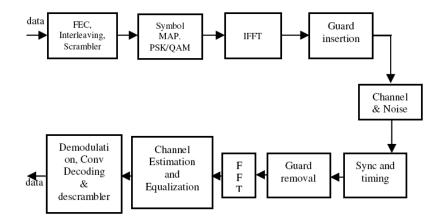

OFDM [9] is a special type of Multi-Carrier Modulation (MCM), where the serial data is divided into multiple parallel bit streams and are modulated using closely spaced non-interfering frequencies called subcarriers. In OFDM, an Inverse Fast Fourier Transform (IFFT) is used to convert the data carrying subcarriers to a time domain signal, which is upconverted to the desired carrier frequency. An inverse operation at the receiver using Fast Fourier Transform (FFT) reveal the frequency domain information. Apart from the simple waveform generation and reconstruction, OFDM provides significant advantages over single carrier transmissions like: immunity to multipath distortion, scalability and spectral separation, making it a superior choice for large family of wireless protocols [10]. In cognitive radio networking, each radio is expected to sense the environment for available spectrum and adapt quickly to it without interfering with the incumbent for that carrier frequency. The secondary system should be able to avoid the primary transmission while communicating within its own network in a *spectrum hole*. This kind of networks require sensing capability, and fast adaptation to new frequency band for both transmission and reception. We believe that OFDM is likely to be chosen as the communication substrate in CR networks due to its inherent capability of transmission and reception in variable bandwidth and in multiple chunks of subcarriers called subchannels. Any subcarrier set can be suppressed to form a Non-Contiguous OFDM (NC-OFDM) waveform, which can be utilized to transmit in a spectrum hole, avoiding the primary user. The use of FFT for OFDM also helps in sensing the spectrum, while other adaptation capabilities, like changing the number of subcarriers and subchannels makes OFDM the most appealing medium for communication in CR networks. Since most of the current wireless protocols, like 802.11a/g, 802.16, LTE, DVB, all use OFDM at the physical layer, we believe that OFDM is a likely choice for cognitive radio application as well. This motivates our research in new architectures for OFDM based radio PHY that will allow innovation in future deployments of CR networks.

In this thesis, we present various steps required to evolve an OFDM based prototype radio into a powerful and flexible research platform for next generation wireless networking research and also provide a methodology to synthesize such complex PHY layers on heterogeneous targets. The thesis also addresses the common design challenge of sharing domain specific knowledge among individuals of varied expertise and applies this concept of knowledge sharing in the broader context of CR networking. Architecting intelligent PHYs require multi-disciplinary knowledge. Whether it is the signal processing subsystems, like synchronization, equalization, etc. or the interfaces to the MAC layer, front-end and the control plane, the PHY should be viewed as a "system of systems". We discuss some of the system level challenges involved in architecting a flexible radio PHY and motivate the contributions of this thesis.

**Reconfiguring the PHY:** Co-existence of multiple standards along with the need for faster time to market, have led hardware manufacturers to lean towards reconfigurable hardware instead of ASICs. However, reconfigurability usually comes at the cost of higher power consumption (FPGAs) or slower processing (CPUs). These practical problems have led manufacturers to resort to either a custom made ASIC or a programmable processor based architecture often involving multicore processors and DSPs, or a heterogeneous architecture involving fast processors and reconfigurable gate arrays. In order to improve efficiency, wireless protocols have severe time constraints built into them. Therefore, while reconfiguring the radio is essential, meeting stringent time constraints, as required by the protocol, is of utmost importance. Also, with advances in silicon technology, the radio design should be able to adapt and optimize across multiple dimensions of speed, reconfigurability, power, etc. Thus, having a method to describe the radio functions independent of the underlying hardware platform is beneficial for casting the final radio hardware into different substrates.

Reconfiguration is also one of the top priorities for experimental prototypes and on-demand reconfiguration is particularly visible in cognitive radio networks. Reconfiguration can be performed at two stages. Basic reconfiguration specifies the operational parameters of the computation kernels, much like input arguments of a function, in programming parlance. This governs the way a particular kernel processes its inputs. Often, the targeted set of protocols have certain common baseband function but with different parameters. For example, the FFT engine for 802.11a/g requires a 64-pt FFT whereas that of 802.16e (WiMax) requires a variable FFT size of 128, 512, 1024 and 2048, supporting different data rates. Similarly, in a cognitive network there is co-existence of heterogeneous devices with different transmission capabilities and the PHY need to adapt its resources to support multiple wireless technologies. The second level of reconfiguration is at a kernel level. Either by replacing specific kernels in the radio pipeline to process a different type of waveform or by re-designing the structure of those kernels at real time from a high level specification. Reconfiguring the radio pipeline is a bigger challenge. While having common baseband kernels make it easier to reuse among various protocols, control over the dataflow between the kernels is also required. A tightly synchronized network-on-chip may provide some run-time reconfiguration of the data flow path but does not provide the full flexibility of software processing. Efficient partitioning the design into software and hardware components while maintaining sufficient flexibility is desired. These decisions should be based on some high level design constraints and not on individual designer's choice.

Another challenge in development of radio PHY is its constant evolution. While every generation of radio design provides support for new and emerging waveforms it also has to adapt with changing silicon technology and board layouts and organization. Migrating from one generation of radio to another has been a constant challenge in the radio design community. It would be beneficial to define a toolflow that would ensure migration - typically code regeneration, allow new constraints on the design, allow for new design partitioning and interconnection of new add-on cards. Often development of each of these individual ele-

ments occur in parallel and with little synchrony among disjoint research effort. The key design approach is "*abstraction*" of various layers involved in designing the PHY. Therefore, the architecture of the radio must allow the seamless interconnection of all the components without having hard synchronization logic between the various DSP subsystems of the PHY. In other words the processing pipeline should be insensitive to latency of individual subsystems. This provide flexibility in replacing, adjusting and re-designing the kernels as well as the system level components.

System level design: Any physical radio device cannot perform without its control layer. In wireless network protocols this layer is termed as the MAC layer. The MAC not only controls the flow of wireless packets it is also responsible for controlling and programming the radio to support cognitive behavior. To handle the complexity and ever-changing need for new cognitive support, the radio is controlled by a separate layer called the Radio Link Control (RLC) layer or the Hardware Abstraction Layer (HAL). The primary goal of the RLC is to program the radio, modify and adapt the radio based on the inputs from the MAC layer. From an architectural perspective, one has to determine the interface of the RLC to the MAC as well as to the PHY. Intuitively, having the MAC and RLC close to the hardware makes it faster to respond to a change in the radio environment, but it provides less flexibility in term of adding new features and waveforms to the radio. Software MACs are more flexible and easy to implement and the latency will be governed by the underline protocols for cognitive radio communication. In either case, a programmable gateway interface between the DSP kernels, peripheral cards (RF and ADC/DACs, clocks, etc) and the RLC while maintaining interoperability with a variety of heterogeneous MAC layers is a key design aspect that researchers need to consider.

Any practical radio goes beyond its baseband operation by integrating a plethora of add-on cards and I/O interfaces. The front-end is an important feature of a cognitive radio, as it has to support a wide range of tuning frequency coupled with adaptive filters and oscillators. Modern RF engines require far more control bandwidth than previous generation of fixed function RF pipeline. Multi-radio platforms make things worse as we have to multiplex and manage datastreams between multiple front-ends. High frequency digital interface is also required for wideband application leading to more control information and analog processing. Typically dataflow between the motherboard and the daughter cards is performed over serial interfaces like SPI that limit the bandwidth and data rate. Therefore, defining a standard interface between the baseboard and add-on daughter cards is required which is also independent of the baseband design. Another important add-on feature is the user I/O. Many choices ranging from PCI, Gigabit Ethernet to Thunderbolt can be made available on radio hardware. The radio architecture will have to be receptive of these various types of I/O sockets to ensure a longer lifetime in the market.

Heterogeneity of radio nodes: If all the radio nodes in a network have the same radio architecture, hardware and processing power, any low level PHY adaptation can be achieved by using a common firmware upgrade, usually in the form of a hardware image (FPGA bitfile) or as a software executable. However, we believe that future cognitive radio networks will comprise of heterogeneous radio nodes that coexist harmoniously using their cognitive capabilities. Although high performance purely software based radios already exist [11], they are large, complex and not practical for mobile applications. New systems will combine specialized software processors [12, 13], be based on reconfigurable computing [14] or on emerging "hybrid FPGA" systems that combine general purpose CPU's, SIMD processing and reconfigurable computing [15]. This plethora of platform choices point towards a more radical form of dynamic software radio reconfiguration where a system not previously designed for a particular waveform (e.g., by a researcher) or during operation.

Heterogeneous computing platform, e.g., the ZYNC platform from Xilinx [15], are often used for deploying SDCRs, primarily to optimize across speed and power consumption. Wireless protocols are very time sensitive and the processing platform has to adhere to the time budget, which in turn dictates the resources required for a particular protocol: e.g., in 802.11a/g a node has to respond to an incoming communication within  $16\mu s$ . So, running 802.11a/g on a general purpose processor without some form of optimization is not practical as it will take too long to decode a packet. This is by far the most important factor that separates modern radio applications from other applications like radar or medical imaging which also use SDRs for speed and power savings. The inter-frame spacing can be different for other protocols and the radio designer will have to optimize the resources used to meet the time budget. The time budget for future protocols that will be used for cognitive radio networks, are not yet defined and so the design method-

ology has to be flexible enough to accommodate these on-demand changes. Also, heterogeneous platforms require different languages when it comes to implementation. While a FPGA based system will only accept HDLs, DSPs and Stream processors will require high level languages and compilers. Since optimization is best left to the domain experts, a high level representation of the dataflow between components is very useful for sharing information across these multiple domains of design. High level description of the SDCR PHY is difficult because it also has to be independent of the target platform.

Design and architecture of next generation SDCRs require knowledge and optimization from different fields of research e.g., DSP and digital communication, electronic design automation, compiler and programming languages, formal methods of system modeling and verification to mention a few. Radio design typically begins with the mathematical model of a waveform, from which a system model is derived with processes and kernels that are compiled to either electrical circuits, software programs or a combination of both. SDCRs are composed of many components interwoven into a complex system of systems and goes beyond the boundaries of a particular kernel or interconnection network. Therefore, it is necessary to abstract the kernel and system design from each other, so that domain specific optimizations can be applied at different stages of the radio design. System design involves multiple subsystems such as, the RF frontend, the ADCs and DACs, user I/O and the MAC layer interface. These, subsystems will have their own set of design constraints that needs to be handled at a system level and should be independent of the kernel level optimization. This will ensure interoperability of a vast number of subsystems that can be developed independent of the waveform or the target hardware used to implement the radio.

In order to address these challenges and provide a unified solution, mechanisms are needed to query the configuration of a system in a platform-independent manner and specify the configuration of a dynamically configurable platform. However, the configuration may involve the use of existing hardware blocks, new software or dynamically reconfigurable computing fabrics or all three methods combined. These configurations can either be specified "bottom up" using an imperative specification or "top down" using a more declarative specification. For example, in the domain of databases, early database techniques to find specific data values involved writing programs to search through a vendor-specific database. Those programs were then bound to that particular problem and that particular platform; this corresponds to the way software is currently developed for cognitive radios. Over time, those programs gave way to a relational algebra and a common specification language (SQL) that both simplifies database access and also allows the database system to improve or optimize the actual query.

A similar problem is faced in cognitive radios – how to specify what is needed, but not over-specify the solution to the point where the features or benefits of a specific platform can not be exploited. We believe that this requires a method for hierarchical description. For example, at a high level, a radio PHY design may want to specify a particular common power-detection mechanism or correlator for packet detection. However, if a system involved in the cognitive network does not "know" that specific design, the design specification can be "lowered" or refined to a more concrete form.

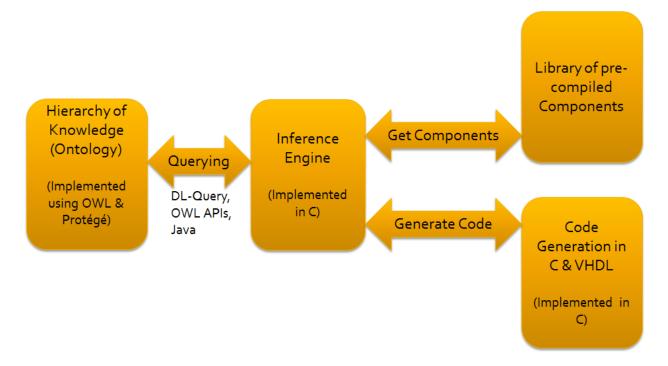

In this thesis, we use an ontology specification, a tool of the semantic web, to capture these hierarchical specifications. Ontologies are a method of knowledge representation that are useful in categorizing large amount of objects within a specified domain, in such a way that different agents can learn and understand the concepts in a domain and their relationships. Ontology is useful in defining taxonomies that organize domains like large collection of web pages and large organizations. The goal is two fold: a structured way of representing a hierarchy of components, their properties and the relationships between them and secondly, to be able to extract information about the domain using queries, such that an agent can learn about other agents and collaborate if needed.

In the domain of cognitive radio networks, agents are characterized by the heterogeneous radio nodes that are trying to collaborate with each other by sharing knowledge about the internal structure of their respective PHY layers, which is nothing but a hierarchy of interconnected components. The use of ontologies in cognitive radio has been studied by Kokar et al. [16, 17] and research [18] has shown that ontology can be effectively used by multiple radios to collaboratively decide on a particular access policy. However, the use of ontology to define the internal structure of a radio PHY hasn't been studied before. In this thesis, we compose the radio PHY on-demand from a high level specification that is represented using an ontology.

The multi-disciplinary nature of building SDCRs require a component based design approach. With appropriate domain knowledge, we are able to extract a set of components and aggregates that are repeated throughout the topology of the radio PHY. Components can vary from basic arithmetic elements like adders, subtractors and multipliers to aggregates of these like, complex multiplier, moving average and FFT blocks. SDCRs are essentially a composition of these basic elements and aggregates along with control signal to direct the flow of samples through the pipeline. The advantage of the aggregates is that they can be treated as *black boxes*, which are optimized for a particular application or even for a target hardware: e.g., a FFT unit for FPGAs will have a different set of optimization than that of the FFTW library that runs on a general purpose processor. Therefore, there is clearly a concept of domain specific optimization embedded in the radio design process. The goal is to bridge this gap as much as possible. Languages used for scientific computing like MATLAB, also employ similar design approach, where domain knowledge is shared across users using pre-defined functions with input and output parameters.

In addition, we use the ontology to describe hierarchical representations of equivalent functionality. For example, there are many possible representations of a correlator. At a high-level, we would like to simply specify that a correlator that meets specific properties is needed. However, a receiving system may not have a specific "correlator" object, and multiple instances of correlators may be needed to finally arrive at an implementable system. The ontology describe relationships between components – for example, either an adder or a fused-multiple-adder (FMA) "is a" functional unit and "is a" adder, and components can belong in many such relationships. In addition to specifying "is a" relationship, a rich web of relationships indicating alternate methods and options must be represented; so must the connections between components – these components and aggregates form the basis of the ontology and the relationship between their instances will define the dataflow. Using a structured representation like ontology, CR nodes can query and learn about the radio PHY without prior knowledge of the structure or the waveform it implements. Once the learning process is over, radios can effectively clone each other and agree on a common mode of communication.

For example, radio A can query radio B if it supports a particular modulation format. In the absence of such a modulation in radio B, it can obtain the description for that particular modulation and compose the internal structure (typically by modifying the I/Q mapping format) for the new modulation. Part of this problem can be solved by parametrizing the modulator. However, this approach is infeasible once the complexity of the system increases, such as in OFDM based protocols. Also, this leads to over-provisioning of resources as it is very hard to predict what new functions will be required in the future for harmonious co-existence of heterogeneous CRs. Using an ontology the radios can understand each other and compose newer subsystems using components from their own library or download from a server without involving the designer or the user. As the subsystems get complex and more application specific, this process can be elevated to a DSP kernel level reconfiguration from a structure level because at that point it gets too complex to formally express and reason on those complex internal structures. Not only does the interconnection between the subsystems need to be programmable, the subsystems themselves require changes to accommodate the superior performance obtained from the protocol. Sometimes these changes are minimal, involving addition or deletion of basic arithmetic elements, while in other cases the changes are major and call for building new components or aggregates altogether. Therefore, to support modern protocols, we need to be able to *clone* the radio PHY, rather than build fixed function pipelines that are brittle when exposed to such novel cross-layer implementations. Hence the term CODIPHY - Composing On-Demand Intelligent PHYsical Layers.

Using suitable back-end compilation, the ontology is translated to the preferred implementation language required by the target platform, thus allowing specific optimizations to be targeted during the implementation phase. For example, a radio expressed as an ontology will allow DSP engineers to describe the structure declaratively, while the radio engineer can use that high level relationship to compose the radio using pre-compiled components and aggregates. Automating this process of expressing the PHY and code generation for onward implementation is the goal of CODIPHY. Now machines can process the radio dataflow and use a rich library of building blocks to compose the radio when it is required to modify the physical structure or the dataflow between various components. CODIPHY is the methodology and toolflow that is able to achieve these in an efficient manner and make CR accessible to the broader community of wireless researchers.

Therefore, the contributions of this thesis are broken into four distinct stages of evolution of a radio PHY from a fixed function processing pipeline to a more flexible substrate suited for cognitive radio and crosslayer networking research. Followed by results from utilizing the flexible platform for wireless crosslayer and cognitive radio research. The final contribution is methodology for synthesizing complex PHYs for heterogeneous processing platforms. We enlist the detailed contribution of this thesis as follows:

- Design, implementation and performance evaluation of an OFDM based 802.11a/g PHY on FPGA with emphasis on the receiver algorithms and structures.

- Evolve the fixed function radio prototype into a SDCR. Specify the requirements of various "tuning knobs" and control parameters required to operate as a frequency agile cognitive radio and facilitate MAC-PHY crosslayer protocol design as well.

- Utilize the flexible PHY to design and implement *five* wireless crosslayer techniques for wireless and cognitive networks. Using theoretical concepts of the OFDM waveform, protocols are designed and evaluated by hardware implementation and experimental results.

- Identify the set of components and aggregates that are used to compose the baseband radio to support a family of OFDM waveforms. This includes Wi-Fi, WiMAX, LTE and any cognitive variant using NC-OFDM. This technique can be applied to other waveforms as well, but we choose OFDM as an example for this thesis for its wide applicability in cognitive radios.

- Create an ontology for the CR PHY. The ontology is designed as a hierarchical knowledge base of different representation levels (system, subsystem, specification and dataflow), which can be used by users of varied expertise, MAC and higher layers and other radio agents as well. By making design decisions at different stages of the radio hierarchy we can facilitate a component based design approach so that the radio designer can specify the exact parameters with limited domain knowledge. Once created, the ontology allows reasoning about the structure of the PHY and the dataflow between its components. This allows CR nodes to agree on not only the high level policies but also how to enforce those policies using proper waveforms at the PHY.

- Query the ontology at different levels and infer the hierarchical knowledge about the PHY structures and its capabilities. This allows knowledge sharing using a high level, declarative representation. Users of varied expertise can choose the granularity of design information.

- Synthesize functioning PHY from the high level design representation targeting FPGAs and general purpose processors. Examples of composing various OFDM subsystems from the ontology is also

presented.

In the realm of radio engineering, CODIPHY provides the answer to "*what to build*" rather than "*how to build*" by expressing the radio pipeline as an ontology. Instead of specifying the architecture of the individual components, CODIPHY represents a system, a level above that by specifying the properties and the hierarchy of the components that are required to build the radio. CODIPHY assumes that these components are made available by various domain experts and that the methodology will only assist in composing the radio from its components. This allows for multiple implementations of the same component targeted for different optimizations ensuring better performance across various dimensions of the radio implementation. Using CODIPHY we can express these qualitative attributes that will assist in generating the correct set of optimized components during the implementation phase.

Existing tools for model driven design for DSP systems, like Xilinx System Generator [19] and Ptolemy [20] are specific methods that govern how things are implemented. For example, System Generator generates code for FPGA based implementation while abstracting the designer from the intricacies of HDLs and Ptolemy generates valid schedules for simulating complex systems on multiprocessor architectures. These methods cannot be used for collaborative learning of CRs because neither of them have the data structure or the reasoning framework to be able to express a system at a functional level, which is the core idea of CODIPHY. Both the methods are useful for building fixed function systems which is detrimental to CRs, where the essence is adaptation through collaborative learning. In the context of this thesis, these modeling tools are considered as domain specific tools that can be an integral part of CODIPHY but are kept separated by using a high level relationship of components. Therefore, CODIPHY will provide the framework that makes radio more malleable and promotes domain specific optimizations while sharing domain knowledge between various research communities.

**Thesis organization:** The concept of CODIPHY is the result of experiences gathered from intersecting areas of research. Whether it is PHY layer prototyping, requiring deep understanding of the signal processing elements or its wide application in crosslayer protocol design and experimental validation, the need to *compose* radio physical layer has been felt at various aspects of wireless research. This thesis is a compilation of all the various steps and experiences that has led to the final realization of CODIPHY.

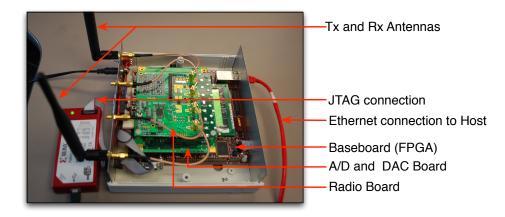

We start by addressing previous work in the area of radio prototyping, wireless crosslayer research and concepts of knowledge sharing in chapter 2. In chapter 3, we discuss the design and implementation of the various signal processing subsystems of an OFDM receiver. This "Physical Layer" is the foundation of this thesis. We extend the basic OFDM PHY to include capabilities for dynamic spectrum access and other cognitive radio processing in chapter 4 thus transforming it to "Intelligent Physical Layers". We present an example implementation of SDCR, which exposes the tunable specifications that caters to the broader community of MAC-PHY crosslaver researchers. In order to show how the PHY is modified to implement crosslayer protocols we present examples of "On-Demand Intelligent Physical Layers" in chapter 5, along with design and evaluation of these applications. At a high level, CODIPHY is composed of three parts that combine to form the idea of "Composing On-Demand Intelligent Physical Layers": Chapter 6, presents a hierarchical knowledge representation methodology using an ontology description that describes complex wireless PHY. Secondly, in chapter 7, we discus the process of retrieving design information by querying the ontology at different levels of granularity and show example of collaboration at the PHY and finally in chapter 8 present the steps required to generate synthesizable FPGA code along with executable C code targeting heterogeneous radio hardware. In chapter ??, we compare CODIPHYto other competing techniques for synthesizing radio PHY and conclude the thesis in chapter 10.

### Chapter 2

#### **Related Work**

Since CODIPHY focuses on convergence of disparate areas of research, it is important to acknowledge the various research efforts in these domains. We categorize this into three broad areas that are relevant to CODIPHY: 1) Methods of radio design and implementations, 2) MAC-PHY crosslayer protocol design, and 3) Cognition and collaboration at the physical layer. CODIPHY addresses the challenges faced in these domains and overcome the drawbacks to form a unified solution of designing complex PHY while allowing for domain specific improvements and research contributions.

Methods of radio design and implementation: The key aspect of architectures of SDR is having a generic framework which achieves the time budget of a wireless protocol within a portable form factor for mobile devices. Originally, digital radios were implemented using a combination of general purpose DSPs or fixed-function logic implemented as an ASIC or using an FPGA. Over time, specialized processor designs have evolved that are finely tuned for handling a set of wireless protocols. However, these processors are mainly suitable for 3G networks, and it's not clear if they are easily adaptable to 4G or other emerging radio standards. Alternative architectures, such as the PicoChip [21] processor combines general purpose processors with fixed-function logic designed to provide more efficient solutions to specific tasks (e.g., correlators for determining if a packet is being received). Radio design is driven by researchers from different communities: DSP and digital communication, Electronic Design Automation, Compiler and programming languages, formal modeling of systems. Each of these groups focus on a particular aspect of the radio but often fail to unify the solution into one system, which is the goal for a practical radio implementation.

Wireless protocol processing can be broadly grouped into four categories: (1) Software processing

only on general purpose processors, (2) On-chip network based architecture, (3) Multiprocessor architecture and (4) Hybrid architecture - general purpose processors along with dedicated accelerators using reconfigurable gate arrays.

When wireless PHY processing is done entirely in software as in [4] and [22], although it aids in programming by using simple high level programming languages, they often fail to meet the protocol timing requirements for modern wireless protocols such as 802.16 and other cognitive radio protocols like 802.22 because of a combination of I/O throughput and post-processing using commercial CPUs. The SORA platform [11], is an implementation of 802.11 physical layer using general purpose CPUs and a radio control board (primarily used for buffering digital samples). Although most of the transceiver is implemented in software, the system isn't able to support NC-OFDM transmission and reception, which is the basic requirement for cognitive radios. The cache optimizations are specifically done to meet Wi-Fi requirements, and will not work for more complex systems.

Network on Chip (NoC) based processing [23, 24, 25] relies heavily on the performance of the routing algorithm and the efficiency of the common functional unit. Reprogramming such devices can only be done at compile time. Unless, the functional units are made multimode, supporting multiple protocols is a challenge using this form of architecture. Other solutions like the FAUST NoC chip [25] and the Magali NoC [26] provide optimized NoCs based on the GALS paradigm, that facilitates swapping of the kernels but that is also limited by the compile time. Also, these are fixed function radio components held together with inflexible logic interfaces, which is sub-optimal for SDRs.

Multiprocessor architectures are particularly effective for radio processing because it meets the protocol timing requirements in most of the cases. SODA [12] provides a multi-processor architecture using optimized SIMD operations for digital processing, but SODA does not address the requirements for CRs and it is not known if the processor could support non-contiguous OFDM or other 4G protocols. In [21], the authors propose a multiprocessor architecture using several hundred processors. Implementation of radio PHY using highly parallel processors is also shown in [27]. Researchers have also used embedded processor to implement a simple single carrier radio transceiver as in [28].

Processor based architectures are often augmented by dedicated hardware acceleration units for par-

ticular algorithms. [29] employs FPGA accelerators for DSP algorithms along with RISC processors, where application specific functions are mapped. These systems often combine dedicated hardware for correlations for signal detection. Software controlled hardware is another form of processing engine that uses software to control certain "knobs" in the hardware to perform multiple tasks. The WARP [30] and KUAR [31] are two such platforms that are capable of certain cognitive radio transmission. Another design approach called partial reconfiguration of FPGA, has been made possible by Xilinx [32], and has been shown to provide run-time reconfigurability for dynamic SDR systems [33] at the cost of high control overhead and resource consumption.

While most of the previous work focuses on architecture of the actual processing engine, very few focus on defining the **requirements** of a true cognitive radio. Therefore, instead of architecting just SDR, future research should be inclined towards the idea of a SDCR. It is important to envision how next generation wireless networks will behave, and the design of the underlying hardware needs to be such that the architecture is ready to embrace any adaptation required.

DSP and digital communication algorithms are usually represented by mathematical equations and joined together to form a processing flow. In order to implement the mathematical structure of a waveform, the equations are translated in the form of a signal flow graph where each **node** represents one or more DSP functions. The graph nodes are parametrized by control information to modify and synchronize the data stream. The data flow graph represents the baseband process of the radio and is mostly composed of forward **edges** with some backward edges for synchronization and iterative loops in the DSP algorithms. The granularity of the data flow model is of importance because that governs the degree of flexibility of the implemented radio. Synchronous data flow based modeling was first introduced for DSP systems in Ptolemy [20]. By analyzing the dataflow graph we can extract a firing schedule for various actors in the graph. Subsequent development of the Dataflow Interchange Format (DIF) [34] has allowed researchers to automate software synthesis from a graph based description of a system [35]. An implementation using DIF for DSP systems has been shown in an example of video coding in [36]. A more recent work in [37] has extended DIF to include topological patterns that are commonly seen in signal processing domain. Although the tool is not exhaustive it shows a that bigger systems can be designed using fundamental building blocks

that repeats itself throughout the processing pipeline. This makes it generic enough to process a particular family of waveforms or applications. However, DIF is limited to auto-generating code and valid schedules for processor based systems which may not be the ideal platform for real-time radio applications. This data flow model has interesting analogies to the flow of software programs, particularly in the realm of stream computing and vector processing. Radio samples can be viewed as streams of floating point or integer numbers that undergo the same transformations which forms the input of another set of processes. This data flow is very typical in radio processing. Stream programming has been employed in modern graphics processors that are shown to be useful for DSP application as well [38]. StreamIt [39], is one such stream programming language that identifies data parallelism in the DSP algorithms and schedules processes to different processor cores to achieve fast computation DSP algorithms. StreamIt and its various peers are good choices for implementing radio functions. However, data-dependent computations like loops and iterative operations need to be addressed with care. Since radio processing has fixed time budgets, it limits the use of software processing unless severely optimized for a particular application, which may make it brittle and prone to failure when implementing other protocols. In order to facilitate re-targeting designs on to different substrates, radio processing logic is sometimes represented in a generic form using behavioral or functional descriptor. These functional description can then be used to generate the required code base for a particular platform of computing - FPGAs, Stream processors, DSPs or general purpose CPUs. The Rosetta [40, 41] functional language presents a method of representing DSP systems as purely functional programs as opposed to conforming to a particular programming language syntax. However, it is still an emerging language and the support for more complex systems like the ones used in SDCRs is not vet known. The wavefrom description language [42] is another example of a text based language to define computation elements used in DSP algorithms. The design flow does not have to be at that low level, instead it can be used to abstract certain low-level structures from the user and expose them as pre-compiled libraries. The granularity of this abstraction however needs to be determined so that there is a seamless integration of research efforts from multiple disciplines.

Another approach used to re-target programs is by extracting the data flow graph from one programming language and then parse and compile it to produce codes in another syntax. Conversion from stream programs to HDLs has been shown in [43], whereas authors in [44] discuss migrating from DSP to a FPGA platform. FPGAs can also be used as co-processor and the code generation from software binaries can be automated to reduce software bottlenecks. This technique has been applied to video decoding algorithms [45] to improve efficiency. Bluespec [46] is another tool that allows system modeling using functional descriptors and use handshaking mechanisms to interconnect subsystems. But it is limited to RTL implementations on FPGAs or ASICs only. It has been used to implement flexible hardware for wireless crosslayer designs [47]. Therefore, in each of these tool flow, representing a DSP process and its interconnection using a data flow graph is essential and individual compilers can be used to automate the code generation with the proper constraints and data structures.

In terms of hardware implementation, HDLs and their tool flow are the most common method. However, over the years there have been tools from the EDA community that facilitates the hardware design flow by hiding the intricacies of the HDLs from the designer. Tools, such as System Generator from Xilinx and AccelDSP from Matlab, uses a combination of Simulink and Matlab's native compiler to implement synthesizable HDLs. Since radio/DSP processes are flow based, it is easier to represent and understand them in schematic form rather than a code base. Complete design and evaluation platform based on library driven schematics greatly reduce the pain of writing and simulating codes written in HDLs. But, unless designed properly this type of tool flow suffers from hand-coded control and synchronization logic for the dataflow that is often brittle due to the data and control dependency between various subsystems. However, systems can be designed with handshaking mechanism or NoC as along as they can be defined by block diagrams using the library components. These tools also provide clock true simulation environments to verify the design before implementing. Simulating the radio as a system and not just at an algorithmic level is important because unlike serial computation model, multiple radio processes operate in parallel to form a complex network of subsystems. Thus, it is important to consider all these factors for selecting the proper tool flow and compilers to implement future SDCRs.

**MAC-PHY crosslayer protocol design:** Researchers have long been focused on the layered architecture of the network protocols and were limited to optimizations and improvements in one particular layer at a time. With the advent of new chipset designs from manufacturers like Atheros, researchers were presented with a higher degree of control over how a device can interact with the communication medium. Now, low-level hardware parameters can be changed using device drivers, like the MadWiFi driver [1] that interacts with the physical hardware to optimize some facets of the waveform. This unprecedented control over the PHY allowed researchers to delve into the physical layer as well. Since few parameters are exposed to the user space it offers limited coverage of the entire space of crosslayer design.

GnuRadio [4], on the other hand provides a very flexible framework. Since the entire PHY is implemented in software using a high level language, it is much easier for a programmer to exploit different aspects of the PHY beyond that was available with the Atheros based hardware. Only drawback is that the entire processing is done offline which makes it harder to test real-time performance of these protocols. These two factors have spurred tremendous efforts in MAC-PHY cross layer protocols over the past decade and still continues to make active contributions to the community.

The similarity among different communication protocols is also reflected in their corresponding physical layer. There is an increasing demand to redesign the common processing engines to perform most of the functions in a fast changing environment of cognitive radio. A close look at the current wireless protocols reveal the need to define a more fundamental set of primitives, beyond just the parameters or the functional operation of a particular transceiver subsystem: e.g., instead of having correlators with fixed coefficients, we should have a method to change the coefficients required for a particular protocol. This is typically required in a cognitive radio environment where the available spectrum varies over time that changes the time domain correlation coefficients [48, 49].

With various concurrent wireless protocols in mind, we define a set of basic capabilities, a generic transceiver should have in order to operate as a SDCR. This deconstruction of the radio physical layer is motivated by a substantial amount of prior research and publication in the cognitive radio and wireless networking community. We focus on OFDM based physical layer as this is a promising enabler for future cognitive radio design. We list the various subsystems of the transceiver and highlight the research that require modification of these subsystems:

• SDCR should be able to transmit and receive in any set of subcarriers [50, 6, 51, 52, 7, 53, 8, 54].

Essentially it should support non-contiguous OFDM transmission and reception so that nodes can communicate using fractured spectrum.

- Not only does it need to adapt to changing spectrum availability, the SDCR should be able to change its modulation (e.g: BPSK, QPSK, 16QAM, 64QAM) at a subcarrier level. Also, high throughput wireless PHY layer techniques require advanced modulations such as superposition coding and hierarchical modulation, which require a high degree of programmability in the modulation levels. In [55, 56, 57, 58, 59], we can find requirement of such systems.

- Depending on the availability of spectrum, the SDCR needs to change the FFT size to control the number of subcarriers to be used for the transmission. Also depending on the channel conditions the duration of the cyclic prefix needs to change to combat multipath channel distortions. WIMAX 802.16 [50] and LTE [60] are examples of wireless protocols that directly requires this capability.

- In order to support NC-OFDM transmission, the SDCR receiver needs programmable correlators which can support arbitrary set of correlator coefficients from a pre-defined superset as chosen by the protocol [48, 61]. [53, 62, 63, 64] are such examples that require synchronization of NC-OFDM preambles which changes the correlator coefficients from one packet to another. Detection of signal based on embedded signature in the waveform is an active area of research. [65] is an example of a cyclostationary detector that is commonly used. These examples show that composing structures for new algorithms is required.

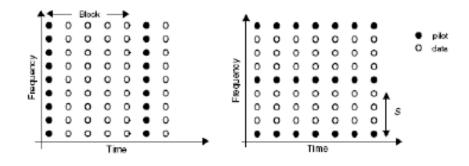

- Channel estimation and Equalization is an important signal conditioning step used in the receivers. To accommodate the changing environment, the transmitter selects different set of pilot subcarriers [66, 50, 67] to assist in the equalization at the receiver end. Therefore the pilot locations and their relevant phase is an important information that the receiver needs to have in order to equalize a NC-OFDM signal.

- Error correction module provide key information about channel conditions that lead to more informed decision in higher layer rate control algorithms [68, 69]. Also, research have shown a

reconfigurable FEC engine [70] is useful is a multi-protocol environment. Not all protocols used all of the FEC modes so instead of over provisioning one should be able to derive the structure from a high level specification for a particular FEC algorithm.

- A very important aspect of Cognitive Radio is **Sensing** [71] for detection of the primary user a channel, which requires post-processing of the FFT results. No other transmitter or receiver blocks are used in this mode. Recent works on simultaneous transmission and reception [7], [52] show requirement of a simple FFT block at the receiver and a threshold based detection. So, a transceiver should be able to perform only FFT and hand over the results to the **Cognitive Engine** to make decision.

- Other physical layer techniques like MIMO or jamming [72, 73, 3] are also implemented as a part of the PHY and should be addressed in the design specifications. Sometimes custom logic is required beyond what has been mentioned in the literature. Re-routing of signals and adding user control signals is also very common in cognitive radio application. Such cases are to be dealt case by case basis and is not possible to make generic across all possible scenarios. But the tool flow to allow that kind of reconfiguration is currently not available for expressing the physical layer of modern cognitive radio.

All of the above examples are either implemented using a full software stack like GnuRadio or uses the limited functionality of the Atheros based Wi-Fi cards. Unfortunately none of the current methods or solutions mentioned in the literature can support the emerging need for MAC-PHY cross layer protocol designers. The current methodologies are brittle and are not properly abstracted for multi-disciplinary contribution rendering it inefficient in most cases or limited in functionality. Authors in [74, 75] have built a fully functional Wi-Fi (802.11a/g) transceiver that provides most of the functions that are addressed above. In [5], authors propose an architecture for modern cognitive radio PHY. However, hand coded controls pose severe impediment while modifying the design to incorporate new features or remove obsolete ones.