# Millimeter-wave GaN MMIC Integration with Additive Manufacturing

by

#### Michael Coffey

B.S., California State Polytechnic University, Pomona, 2010M.S., University of Colorado, Boulder 2014

A thesis submitted to the

Faculty of the Graduate School of the

University of Colorado in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy

Department of Electrical, Computer, and Energy Engineering

2017

# This thesis entitled: Millimeter-wave GaN MMIC Integration with Additive Manufacturing written by Michael Coffey has been approved for the Department of Electrical, Computer, and Energy Engineering

| Zoya Popović    |      |

|-----------------|------|

|                 |      |

| Michael DeLisio |      |

|                 |      |

|                 |      |

|                 | Data |

The final copy of this thesis has been examined by the signatories, and we find that both the content and the form meet acceptable presentation standards of scholarly work in the above mentioned discipline.

Coffey, Michael (Ph.D., Electrical Engineering)

Millimeter-wave GaN MMIC Integration with Additive Manufacturing

Thesis directed by Zoya Popović

This thesis addresses the analysis, design, integration and test of microwave and millimeter-wave monolithic microwave integrated circuits (MMIC or MMICs). Recent and ongoing progress in semiconductor device fabrication and MMIC processing technology has pushed the upper limit in MMIC frequencies from millimeter-wave (30 - 300 GHz) to terahertz (300 - 3000 GHz). MMIC components operating at these frequencies will be used to improve the sensitivity and performance of radiometers, receivers for communication systems, passive remote sensing systems, transceivers for radar instruments and radio astronomy systems. However, a serious hurdle in the utilization of these MMIC components, and a main topic presented in this thesis, is the development and reliable fabrication of practical packaging techniques.

The focus of this thesis is the investigation of first, the design and analysis of microwave and millimeter-wave GaN MMICs and second, the integration of those MMICs into usable waveguide components. The analysis, design and testing of various X-band (8-12 GHz) thru H-band (170-260 GHz) GaN MMIC power amplifiers (PA or PAs), including a V-band (40-75 GHz) voltage controlled oscillator, is the majority of this work. Several PA designs utilizing high-efficiency techniques are analyzed, designed and tested. These examples include a  $2^{nd}$  harmonic injection amplifier, a Class-E amplifier fabricated with a GaN-on-SiC 300 GHz  $f_T$  process, and an example of the applicability of supply-modulation with a Doherty power amplifier, all operating at 10 GHz. Two H-band GaN MMIC PAs are designed, one with integrated CPW-to-waveguide transitions for integration. The analysis of PA stability is especially important for wideband, high- $f_T$  devices and a new way of analyzing stability is explored and experimentally validated.

Last, the challenges of integrating MMICs operating at millimeter-wave frequencies are discussed and assemblies using additive and traditional manufacturing are demonstrated.

# Dedication

This thesis is dedicated to my mother Teresa, my girlfriend Caitlyn, and my dear old Granddad, for their help is how I got through it.

#### Acknowledgements

This thesis was made possible by the constant hard work of Zoya Popović to do her best as an educator, professor, and research advisor. Without her, there would be a lot less PhDs in the world, including my own. I would like to acknowledge the people I have worked with in this field who are my role models for hard work and persistence: Mike DeLisio, Chad Deckman, Miroslav Micović, Gregor Lasser, Mike Litchfield, Scott Schafer and Maxwell Duffy. I want to also acknowledge the people I worked with who made it a better experience in the lab and in Boulder: Andrew Zai, Sean Korhummel, Ignacio Ramos and Mauricio Pinto. The last year of the program had various deadlines and pressures of its own and my friend and neighbor Blaine Krumpe has to be credited for making me forget them often.

# Contents

# Chapter

| 1        | Intro | eduction and Motivation                                         | 1  |

|----------|-------|-----------------------------------------------------------------|----|

|          | 1.1   | Introduction to MMIC Technology and Design                      | 5  |

|          | 1.2   | Introduction to Additive Manufacturing                          | 9  |

|          | 1.3   | Thesis Overview                                                 | 10 |

| <b>2</b> | Effic | iency-Enhancement Techniques for X-Band GaN MMIC PAs            | 12 |

|          | 2.1   | Introduction                                                    | 12 |

|          | 2.2   | Output Harmonic Injection MMIC PA                               | 13 |

|          |       | 2.2.1 Output Harmonic Injection MMIC PA Design                  | 15 |

|          |       | 2.2.2 Measurements and Discussion                               | 16 |

|          | 2.3   | Doherty Power Amplifier MMIC PA with Supply Modulation          | 22 |

|          |       | 2.3.1 The Doherty PA                                            | 22 |

|          |       | 2.3.2 X-band Doherty PA Design and Layout                       | 23 |

|          |       | 2.3.3 Characterization with Supply Modulation                   | 26 |

|          | 2.4   | Class-E MMIC PA                                                 | 29 |

|          |       | 2.4.1 Design and Layout of Class-E and Class-E Cascode MMIC PAs | 33 |

|          |       | 2.4.2 Measurements and Comments                                 | 36 |

|          | 2.5   | Contributions from This Chapter                                 | 38 |

| 3 | Ana  | lysis and Design of a Reverse-Channel U-and V-band VCO         | 39  |

|---|------|----------------------------------------------------------------|-----|

|   | 3.1  | Millimeter-wave Voltage Controlled Oscillators                 | 39  |

|   | 3.2  | Qorvo's 90-nm GaN-on-SiC process                               | 42  |

|   |      | 3.2.1 Passive Technology                                       | 42  |

|   |      | 3.2.2 Active Technology                                        | 43  |

|   | 3.3  | Reverse-Channel Operation                                      | 44  |

|   | 3.4  | Design and Layout                                              | 45  |

|   | 3.5  | AM Waveguide Intergration                                      | 57  |

|   | 3.6  | Measurements and Conclusion                                    | 62  |

|   | 3.7  | Contributions from This Chapter                                | 65  |

| 4 | Ana  | lysis and Design of 235 GHz GaN-on-SiC Amplifiers              | 66  |

|   | 4.1  | Motivation for MMICs Operating at 235 GHz                      | 66  |

|   | 4.2  | HRL T4 GaN-on-SiC Process and Device Characteristics           | 69  |

|   |      | 4.2.1 Passive Technology                                       | 69  |

|   |      | 4.2.2 Active Technology and Device Characteristics             | 71  |

|   | 4.3  | Design                                                         | 73  |

|   |      | 4.3.1 On-chip Power Combining with Even Odd Mode Analysis      | 76  |

|   |      | 4.3.2 Design Features                                          | 80  |

|   |      | 4.3.3 Transition to WR 4.3 Rectangular Waveguide               | 84  |

|   | 4.4  | Measurements and Conclusion                                    | 87  |

|   | 4.5  | Contributions from This Chapter                                | 89  |

| 5 | Stab | pility Analysis in Microwave Circuits                          | 90  |

|   | 5.1  | Introduction to Stability Analysis in Microwave Circuits       | 90  |

|   | 5.2  | A General Technique for Stability Analysis of Microwave PAs    | 96  |

|   |      | 5.2.1 Comparison to Single-Injection Analysis                  | 100 |

|   | 5.3  | Application to Single and Multiple Stage PA Stability Analysis | 105 |

149

|   |      | 5.3.1 Stability Example with a Commercial S-Band Amplifier                   | . 105       |

|---|------|------------------------------------------------------------------------------|-------------|

|   |      | 5.3.2 Stability Example with a Two-stage X-Band GaN MMIC                     | . 110       |

|   | 5.4  | Discussion and Conclusion                                                    | . 113       |

|   | 5.5  | Contributions from This Chapter                                              | . 113       |

| 6 | Mill | meter-wave Component Integration Methods                                     | <b>11</b> 4 |

|   | 6.1  | Introduction                                                                 | . 114       |

|   | 6.2  | AM for Millimeter-wave Components                                            | . 115       |

|   |      | 6.2.1 Measured Performance                                                   | . 119       |

|   |      | 6.2.2 Analysis and Conclusion                                                | . 125       |

|   | 6.3  | Thermal Challenges in Millimeter-wave Component Design and Additive Manufac- |             |

|   |      | tured Heat Pipes                                                             | . 127       |

|   |      | 6.3.1 Thermal Analysis for MMIC Design                                       | . 127       |

|   |      | 6.3.2 FEM Thermal Analysis                                                   | . 130       |

|   |      | 6.3.3 Additive Manufactured AlSi10Mg Heat Pipes                              | . 135       |

|   | 6.4  | Conclusion                                                                   | . 140       |

|   | 6.5  | Contributions from This Chapter                                              | . 141       |

| 7 | Futu | re Work, Summary and Contributions                                           | 142         |

|   | 7.1  | Future work in Millimeter-wave MMIC Design and Fabrication                   | . 142       |

|   | 7.2  | Future work in AM Integration                                                | . 145       |

|   | 7.3  | Summary and Contributions                                                    | . 146       |

|   |      |                                                                              |             |

|   |      |                                                                              |             |

Bibliography

# Tables

| 1.1 | Summary of results in the above MMIC technology figure               |

|-----|----------------------------------------------------------------------|

| 2.1 | Summary of X-band PA Performance                                     |

| 5.1 | Ring Oscillator Circuit Parameters                                   |

| 6.1 | Summary of AM Waveguide Surface Finish Characteristics at 95 GHz 124 |

| 6.2 | Compatibility of Working Fluids and Heat Pipe Materials              |

| 6.3 | Summary of Heat Pipe Parameters                                      |

# Figures

# Figure

| 1.1 | Millimeter-wave MMIC technology progression over the years with a variety of output                           |    |

|-----|---------------------------------------------------------------------------------------------------------------|----|

|     | power levels, operating frequencies and different fabrication technology. The three                           |    |

|     | marker sizes represent $<10\mathrm{mW},$ between $10\mathrm{mW}$ and $1\mathrm{W},$ and $>1\mathrm{W}.$       | 2  |

| 1.2 | (a) 10 GHz output harmonic injection MMIC PA (b) 10 GHz Class-E amplifier MMIC                                |    |

|     | PA (c) V-band VCO (d) 235 GHz 8-way combined MMIC PA                                                          | 4  |

| 1.3 | A typical FET layout cell. This device is $8x75\mu\mathrm{m}$ , for a total periphery of $600\mu\mathrm{m}$ . |    |

|     | With a $3.4\mathrm{W/mm}$ output power density, this device has a potential output power                      |    |

|     | of $> 2$ W. Source: [1]                                                                                       | 5  |

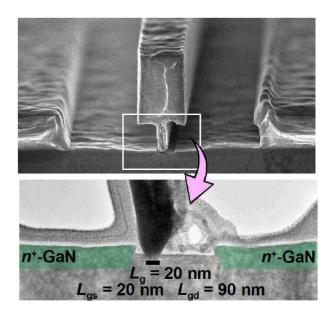

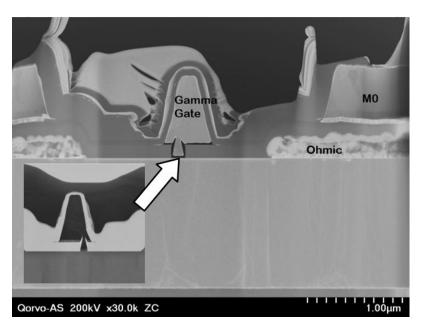

| 1.4 | A SEM photograph of the gamma-gate used in Chapter 3. The transistors in this                                 |    |

|     | process exhibit $f_T > 72\mathrm{GHz}$ . Photograph: Qorvo                                                    | 7  |

| 1.5 | A SEM photograph of the T-gate used in Chapter 4. The transistors in this process                             |    |

|     | exhibit $f_T > 300\mathrm{GHz}$ . Photograph: HRL Laboratories                                                | 7  |

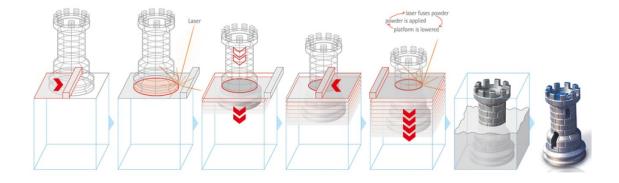

| 1.6 | The DMLS process. The wire frame represents the design and the solid part is                                  |    |

|     | built up from individual layers of discrete metal particles fused together with a laser.                      |    |

|     | Source: [2]                                                                                                   | 9  |

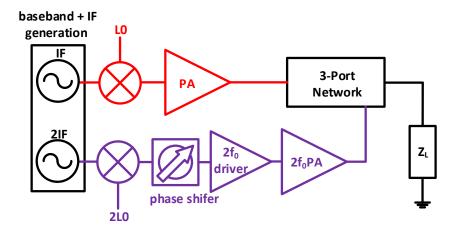

| 2.1 | Block diagram of a HI power amplifier. The $f_0$ path is shown in red and the $2f_0$                          |    |

|     | path in purple                                                                                                | 14 |

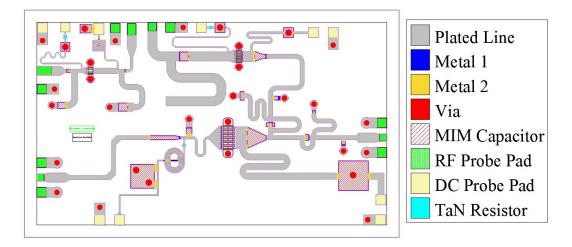

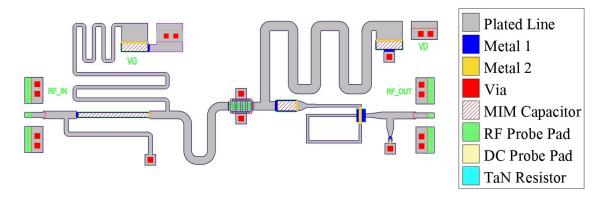

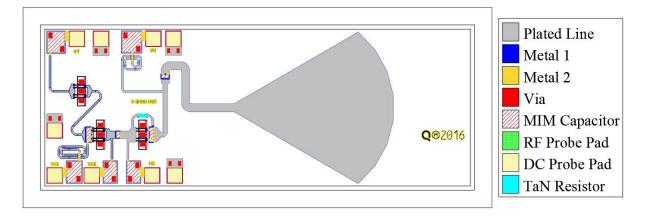

| 2.2 | Layout of the harmonic injection amplifier. The legend shows metal layers, via,                   |    |

|-----|---------------------------------------------------------------------------------------------------|----|

|     | resistor, and capacitor locations, and DC and RF probe pads. Plated line refers to                |    |

|     | the combination of Metal $1 + \text{Metal } 2$ to form a high current capacity transmission       |    |

|     | line                                                                                              | 16 |

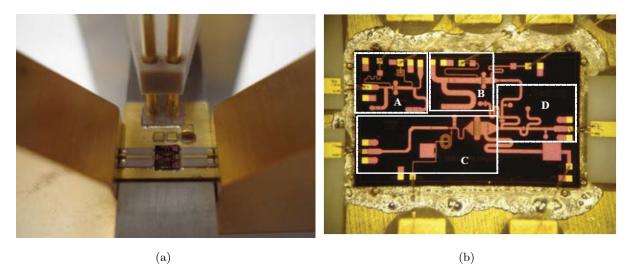

| 2.3 | a) Fixture for RF and DC interface to MMIC. Spring-loaded pins (top) provide DC                   |    |

|     | bias and supply and coaxial-to-microstrip transitions provide RF input and output b)              |    |

|     | the fabricated output harmonic injection PA with $A$ and $B$ highlighting the 2-stage             |    |

|     | $2f_0$ amplifier, $C$ representing the main $f_0$ PA and $D$ showing the output network           |    |

|     | with diplexer.                                                                                    | 17 |

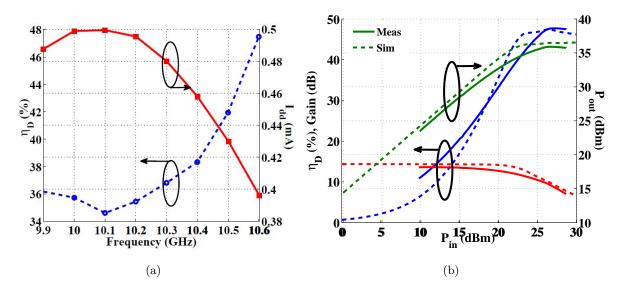

| 2.4 | (a) Measured drain efficiency (blue) and $I_D$ (red) versus frequency. In (b) simulated           |    |

|     | (dashed) and measured (solid) $\eta_D$ , gain, and $P_{out}$ at 10.6 GHz                          | 17 |

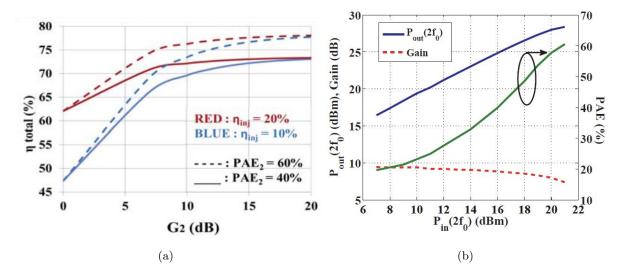

| 2.5 | (a) Total calculated amplifier efficiency versus gain, $G_2$ , for the 20 GHz driver am-          |    |

|     | plifier for different $\eta_{inj}$ and $PAE_{2f_0}$ . (b) Measured gain, output power and PAE of  |    |

|     | the 20 GHz driver amplifier                                                                       | 19 |

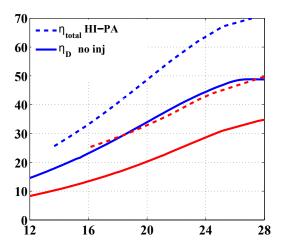

| 2.6 | Calculated total $\eta_D$ at 10 GHz (red) and 10.6 GHz (blue) with and without output             |    |

|     | harmonic injection (dashed and solid lines) based on measured $f_0$ and $2f_0$ PA data.           | 21 |

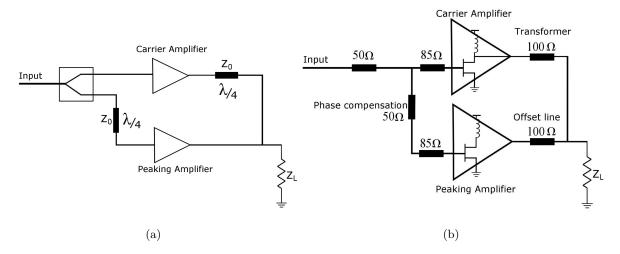

| 2.7 | (a) Conventional topology of the Doherty power amplifier. (b) The Doherty architec-               |    |

|     | ture used in this work. The $\lambda/4$ transformer is replaced with a combined matching          |    |

|     | network and impedance transformer. The input is an unequal-power reactive divider                 |    |

|     | that compensates the output phase offset                                                          | 23 |

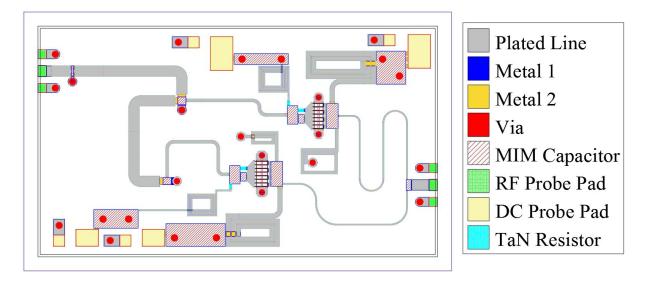

| 2.8 | Layout of X-Band MMIC Doherty PA. Vias are visible in the capacitor-over-via                      |    |

|     | bypass capacitors and in the ground pads for RF and DC probes. The legend shows                   |    |

|     | important layers, similar to the HI-PA. The total die size is $3.8\mathrm{mm}$ x $2.3\mathrm{mm}$ | 24 |

| 2.9 | The MMIC DPA on a CuMo carrier with alumina microstrip interconnects as tested.                   |    |

|     | 100 pF bypass capacitors are shown connected to drain and gate DC pads. The total                 |    |

|     | die size is 3.8 mm x 2.3 mm.                                                                      | 25 |

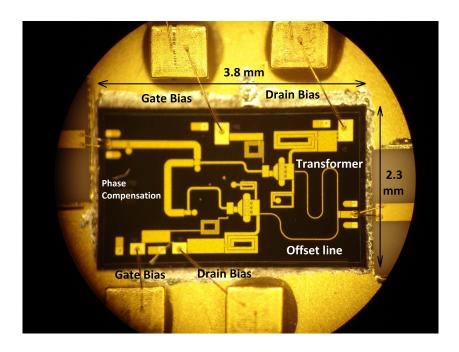

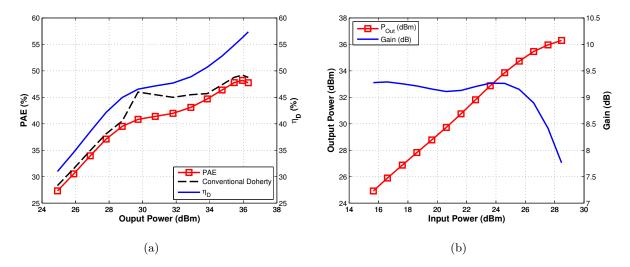

| 2.10 | (a) Measured drain efficiency (blue) and PAE (red) of the DPA versus output power                |    |

|------|--------------------------------------------------------------------------------------------------|----|

|      | at 10 GHz. The dashed line shows idealized Doherty PAE for a comparison. (b)                     |    |

|      | Measured output power (red) and gain (blue) of the DPA versus input power at                     |    |

|      | 10 GHz                                                                                           | 26 |

| 2.11 | Adjacent channel power for the fixed-supply Doherty PA with various output powers.               |    |

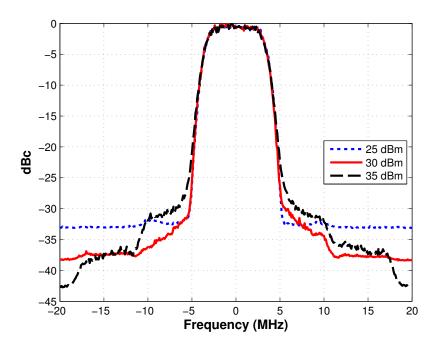

|      | No DPD or predistortion was used                                                                 | 27 |

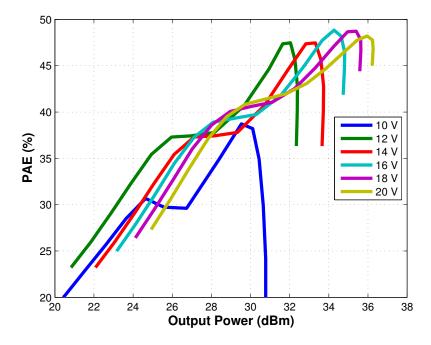

| 2.12 | PAE and output power in a supply modulation experiment where both carrier and                    |    |

|      | peaking PA were simultaneously modulated                                                         | 28 |

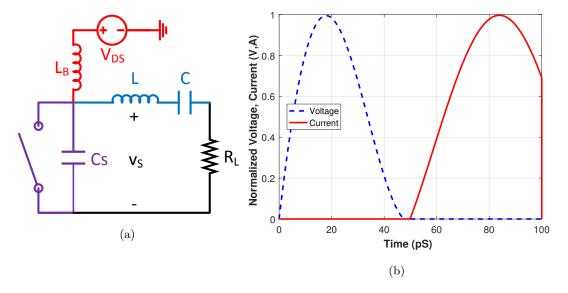

| 2.13 | (a) The ideal Class-E amplifier circuit. (b) The switching waveforms for an ideal,               |    |

|      | $f_S=10\mathrm{GHz},\mathrm{Class\text{-}E}$ amplifier                                           | 30 |

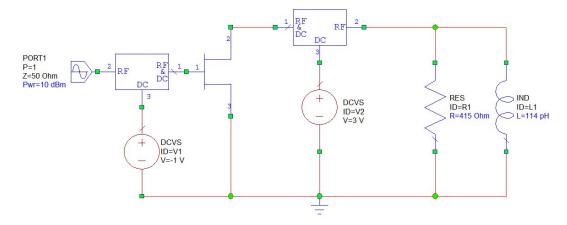

| 2.14 | Simulation circuit for determining the nonlinear device capacitance $C_s$                        | 32 |

| 2.15 | Tuning the simulated dynamic load line of the Class-E amplifier. In (a) the dynamic              |    |

|      | load line without $C_s$ cancelled, in (b) a inductance of 114 pH minimizes the hysteresis        |    |

|      | in the load line                                                                                 | 32 |

| 2.16 | Layout View of the X-Band Class-E amplifier. The legend shows the relevant layers                |    |

|      | and passive components. The total die size is 2.335 mm x 0.807 mm                                | 33 |

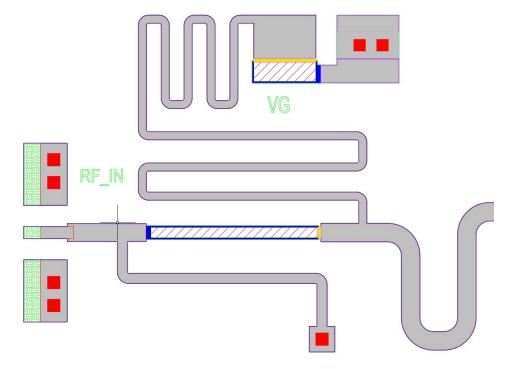

| 2.17 | Input matching network layout view of the X-Band Class-E amplifier. The total size               |    |

|      | of the network is 1.15 mm x 0.807 mm                                                             | 34 |

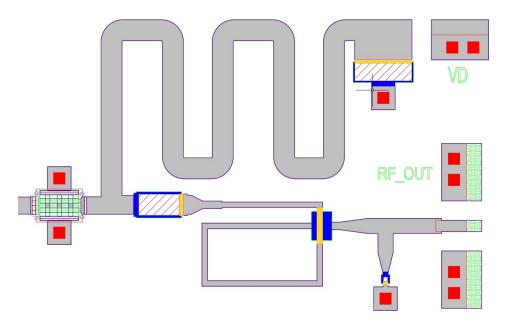

| 2.18 | Layout view of the X-Band Class-E amplifier output matching network. The total                   |    |

|      | size of the network is $1.02\mathrm{mm}$ x $0.807\mathrm{mm}$                                    | 35 |

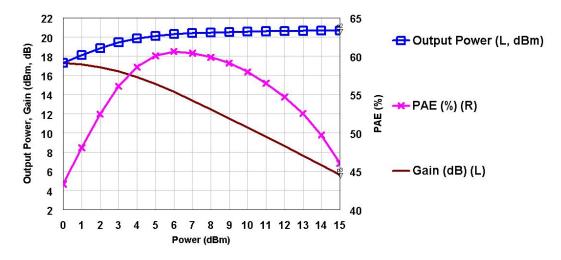

| 2.19 | The simulated PAE (right), gain and output power (left) of the Class-E amplifier                 | 36 |

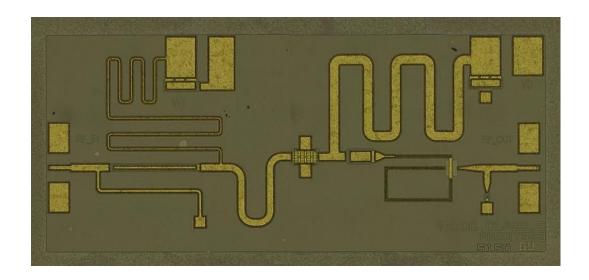

| 2.20 | Microphotograph of X-Band Class-E amplifier. The total die size is $2.335\mathrm{mm}$ x          |    |

|      | 0.807 mm                                                                                         | 37 |

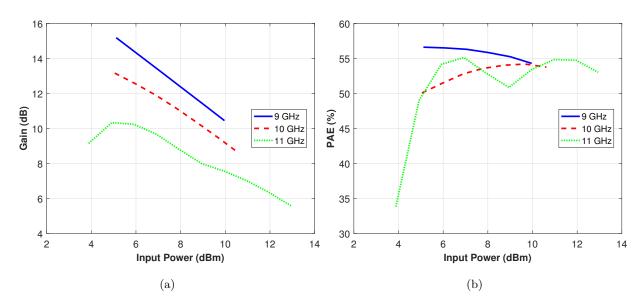

| 2.21 | Class-E gain, output power and PAE measured from 9-11 GHz at $V_D=3{\rm V.}$                     | 37 |

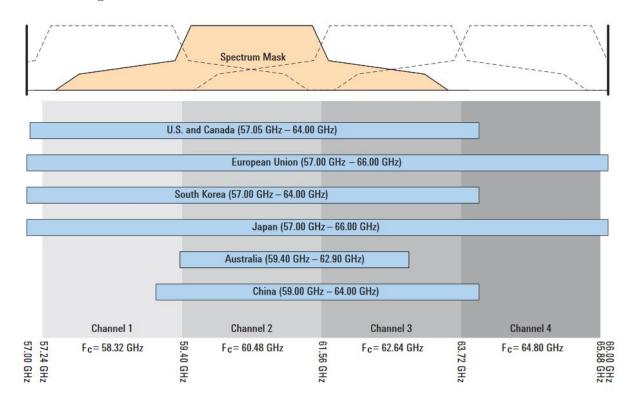

| 3.1  | An overview of the unlicensed spectrum available in the $57\text{-}66\mathrm{GHz}$ range in each |    |

|      | region where the standard is finalized. Source: [3]                                              | 40 |

| 3.2  | Gamma-gate SEM photograph. The source connection is on the right and the drain                                                  |    |

|------|---------------------------------------------------------------------------------------------------------------------------------|----|

|      | is on the left, the S-D separation is 2 $\mu$ m. Photograph: Qorvo                                                              | 43 |

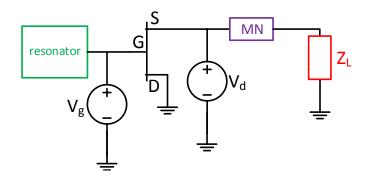

| 3.3  | The reverse channel oscillator circuit schematic. DC gate bias and drain supply                                                 |    |

|      | paths are not shown                                                                                                             | 45 |

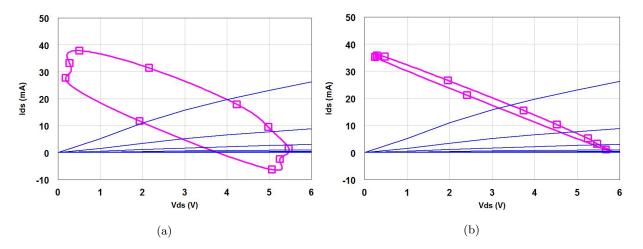

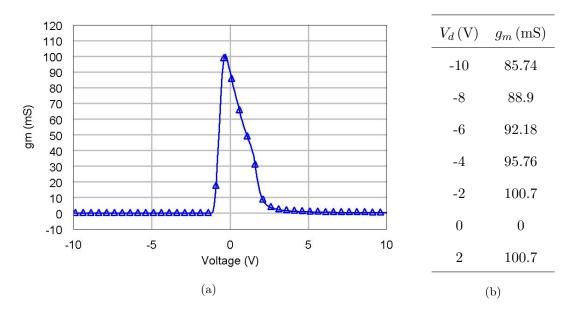

| 3.4  | a) Reverse channel $\frac{\mathrm{d}i_{ds}}{\mathrm{d}v_{gs}}$ for varying $V_g$ . The peak is at -0.3 V. b) The range of $g_m$ |    |

|      | for different drain voltages showing peak transconductance at -2 V                                                              | 46 |

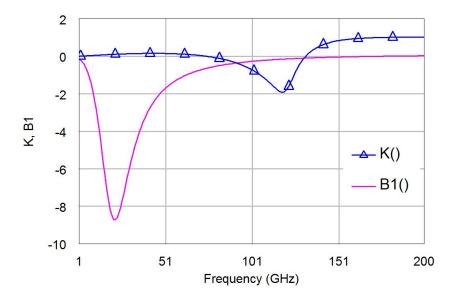

| 3.5  | Range of potentially unstable operation for the reverse channel device. The $K$ -factor                                         |    |

|      | is shown in blue and the $B_1$ factor in pink. The device is potentially unstable until                                         |    |

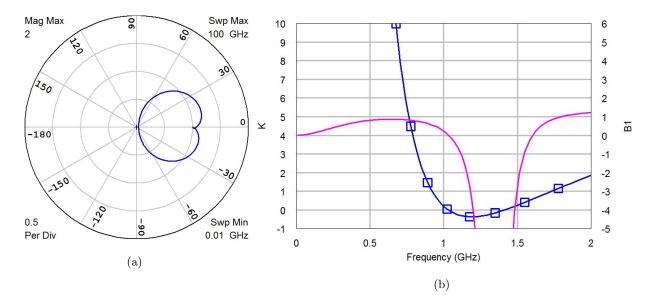

|      | 174 GHz but was modeled from 0.5 to 110 GHz                                                                                     | 47 |

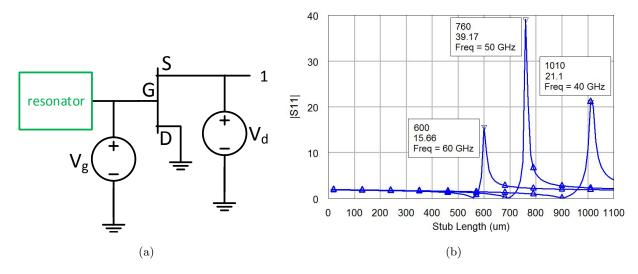

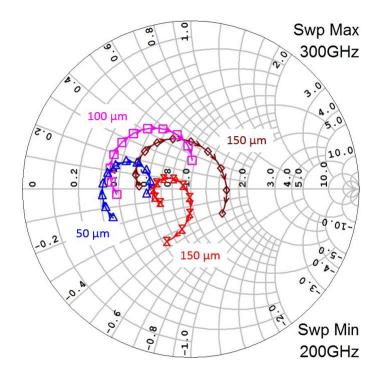

| 3.6  | (a) The oscillator with port 1 referenced. (b) Small-signal simulated $ S_{11} $ for var-                                       |    |

|      | ious gate resonator stub lengths. The $1.01\mathrm{mm}$ stub corresponds to an oscillation                                      |    |

|      | frequency at $40\mathrm{GHz}$ and the $600\mu\mathrm{m}$ stub corresponds to an output frequency at                             |    |

|      | $60\mathrm{GHz}$ . The second number in the markers shows the magnitude of $S_{11}$ , which is $>$                              |    |

|      | 1 for all frequencies                                                                                                           | 48 |

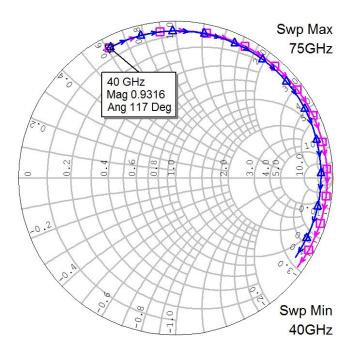

| 3.7  | The simulated reflection coefficients for the $1.01\mathrm{mm}$ fixed length stub in pink and                                   |    |

|      | the tunable short circuit stub in blue with Vg = -1.5 V. $\ \ldots \ \ldots \ \ldots \ \ldots$                                  | 49 |

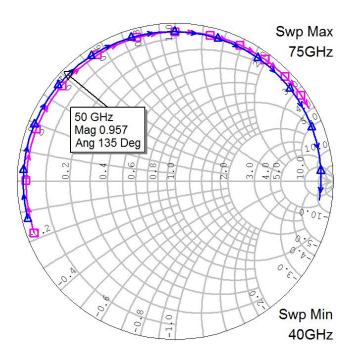

| 3.8  | The simulated reflection coefficient for the 760 $\mu\mathrm{m}$ fixed length stub in pink and the                              |    |

|      | tunable short circuit stub in blue with Vg = -5.3 V                                                                             | 49 |

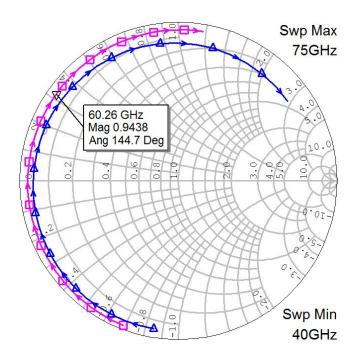

| 3.9  | The $600\mu\mathrm{m}$ fixed length stub reflection coefficient in pink and the tunable short                                   |    |

|      | circuit stub in blue with Vg = -20.6 V                                                                                          | 50 |

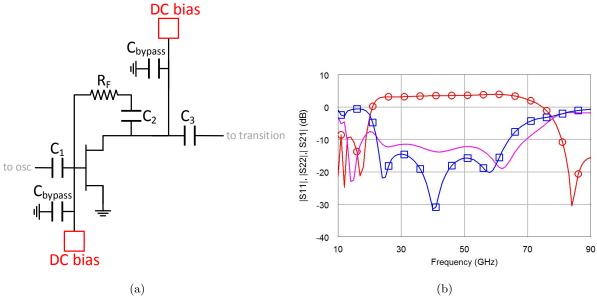

| 3.10 | (a) The circuit schematic of the feedback buffer amplifier. $C_1$ and $C_3$ are DC blocking                                     |    |

|      | capacitors $C_2$ routes DC bias (capacitor top plate) and blocks DC (capacitor bottom                                           |    |

|      | plate.) (b) The simulated S-parameters of the buffer amplifier, $ S_{21} $ is shown in red,                                     |    |

|      | $ S_{11} $ in blue and $ S_{22} $ in pink. The gain of the buffer amplifier is 4 dB at the center                               |    |

|      | of the band                                                                                                                     | 51 |

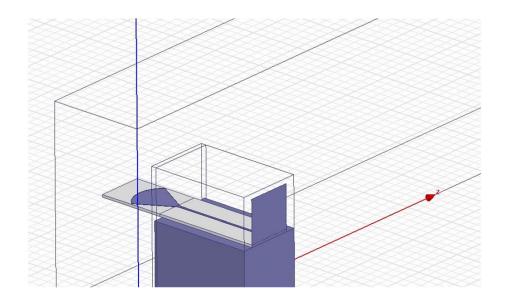

| 3.11 | The simulation setup for the radial stub microstrip-to-waveguide transition on a                          |    |

|------|-----------------------------------------------------------------------------------------------------------|----|

|      | $50\mu\mathrm{m}$ SiC substrate. The transition is inside a WR-15 waveguide and excited with              |    |

|      | a microstrip mode in a cavity with a reduced height to suppress higher order modes.                       | 52 |

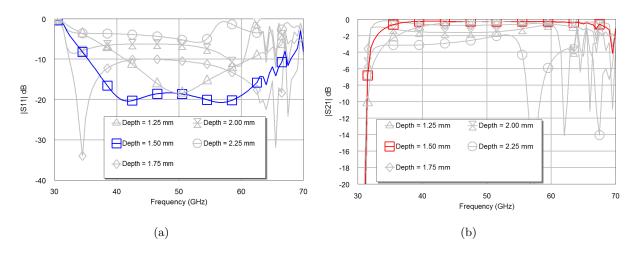

| 3.12 | (a) Simulated $ S_{11} $ and variations of the probe depth into the waveguide. (b) $ S_{21} $             |    |

|      | and variations of the probe depth into the waveguide. The insertion loss for the                          |    |

|      | transition is $0.23\mathrm{dB}$ at $50\mathrm{GHz}$                                                       | 52 |

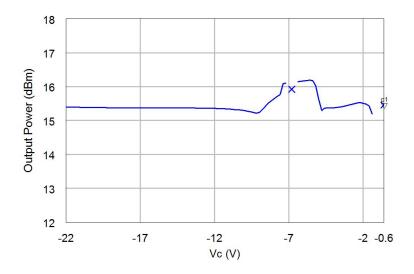

| 3.13 | The simulated output power versus control voltage, $V_c$ , for the complete reverse-                      |    |

|      | channel oscillator. The simulation includes the tunable stub, reverse-channel oscil-                      |    |

|      | lator, buffer amplifier and S-parameters from the microstrip-to-waveguide simulation.                     | 53 |

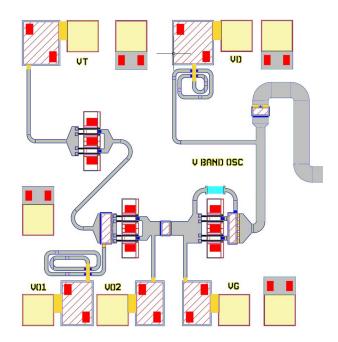

| 3.14 | The detailed layout of the V-band oscillator. The total die size is $2.7 \mathrm{x} 1.15  \mathrm{mm}^2.$ | 53 |

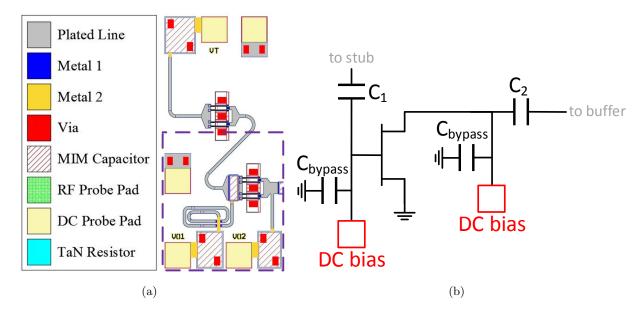

| 3.15 | (a) The reverse channel oscillator layout detail, highlighted in purple. (b) The cor-                     |    |

|      | responding circuit schematic                                                                              | 54 |

| 3.16 | (a) The tunable short circuit stub, highlighted in purple. (b)The circuit schematic                       |    |

|      | of the tunable short circuit stub                                                                         | 55 |

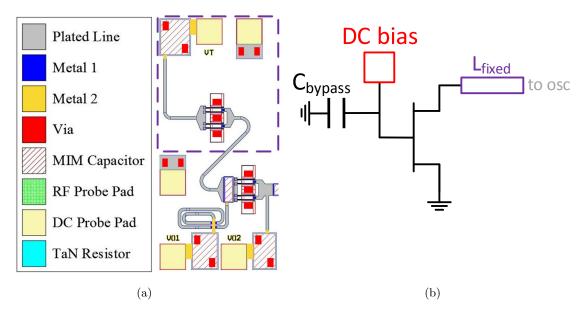

| 3.17 | (a) The layout detail of the buffer amplifier. (b) The circuit schematic of the feedback                  |    |

|      | buffer amplifier. $C_1$ and $C_3$ are DC blocking capacitors, $C_2$ acts as part of a bias tee.           | 56 |

| 3.18 | Close-up view of the detailed layout of the tunable short-circuit stub, oscillator                        |    |

|      | circuit, and buffer amplifier                                                                             | 56 |

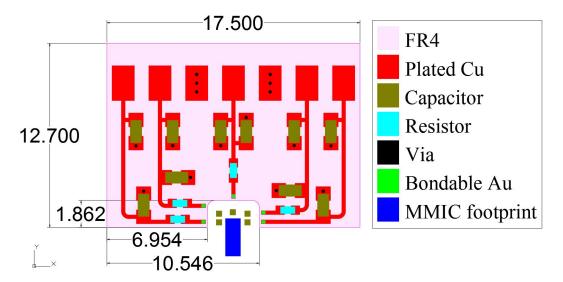

| 3.19 | Assembly drawing of the bias and control board. The total size is $17.5 \text{x} 12.5  \text{mm}^2$ .     |    |

|      | All dimensions are specified in mm                                                                        | 57 |

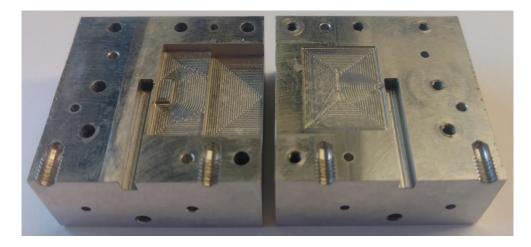

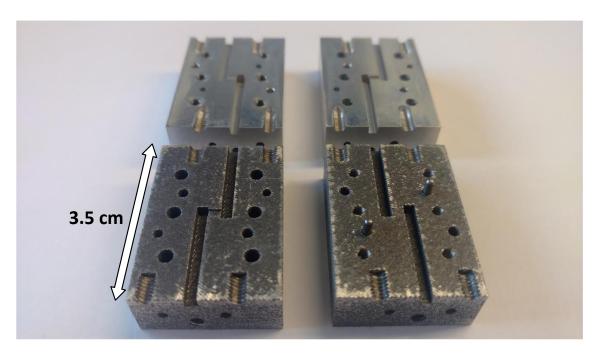

| 3.20 | Photograph of machined V-band waveguide housing. The waveguide is WR-15 and                               |    |

|      | made of Al. Each split block is approximately $3.5\mathrm{cm}$ per side. WR-19 waveguide                  |    |

|      | housings were also fabricated                                                                             | 58 |

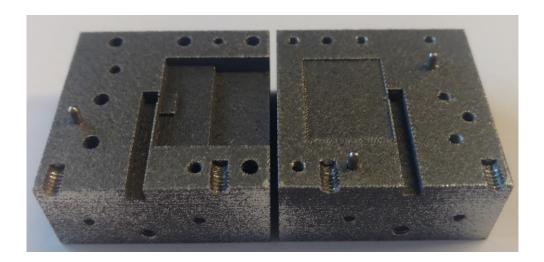

| 3.21 | Photograph of AM V-band waveguide housing. The waveguide is WR-15 and made                                |    |

|      | of AlSi10Mg. Each split block is approximately $3.5\mathrm{cm}$ per side. WR-19 waveguide                 |    |

|      | housings were also fabricated                                                                             | 58 |

| 3.22 | Photograph of the AM V-band test assemblies with AM and traditional machining.                                         |    |

|------|------------------------------------------------------------------------------------------------------------------------|----|

|      | The AM structures are shown in the foreground and traditionally machined in the                                        |    |

|      | background                                                                                                             | 59 |

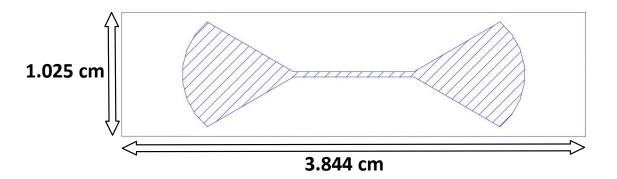

| 3.23 | Assembly drawing of the V-band alumina test structure. The metal layer is hatched                                      |    |

|      | and the bare alumina is white. The thin film size is $3.844 \mathrm{x} 1.025  \mathrm{mm}^2$ and $100  \mu \mathrm{m}$ |    |

|      | thick                                                                                                                  | 59 |

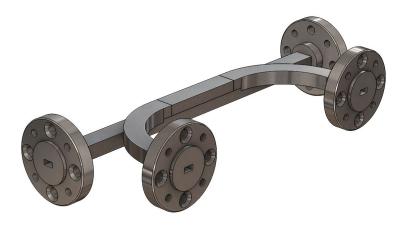

| 3.24 | Assembled machined V-band waveguide-to-microstrip-to-waveguide test structure.                                         |    |

|      | The waveguide is WR-15 and made of Al                                                                                  | 60 |

| 3.25 | Assembled AM V-band waveguide-to-microstrip-to-waveguide test structure. The                                           |    |

|      | waveguide is WR-15 and made of AlSi10Mg                                                                                | 60 |

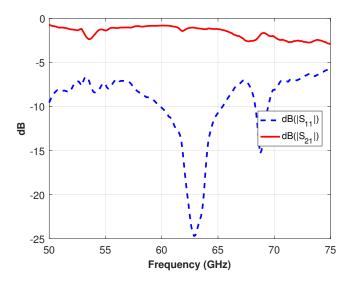

| 3.26 | $ S_{11} $ and $ S_{21} $ for the machined V-band waveguide-to-microstrip-to-waveguide test                            |    |

|      | structure. The $ S_{21} $ data shown is the measured loss divided by two to approximate                                |    |

|      | the loss of a single transition                                                                                        | 61 |

| 3.27 | $ S_{11} $ and $ S_{21} $ for the AM V-band waveguide-to-microstrip-to-waveguide test struc-                           |    |

|      | ture. The $ S_{21} $ data shown is the measured loss divided by two to approximate the                                 |    |

|      | loss of a single transition                                                                                            | 61 |

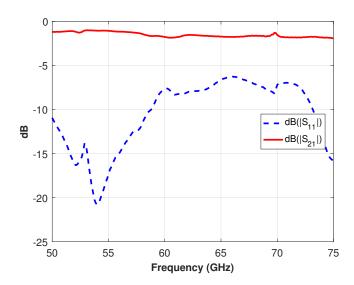

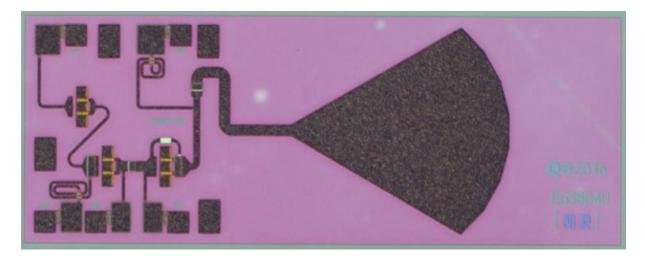

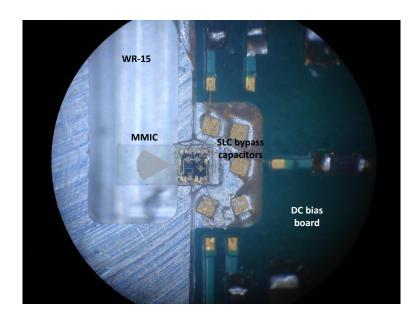

| 3.28 | Microphotograph of the VCO during fabrication. The total die size is $2.7 \mathrm{x} 1.15  \mathrm{mm}^2$ .            | 62 |

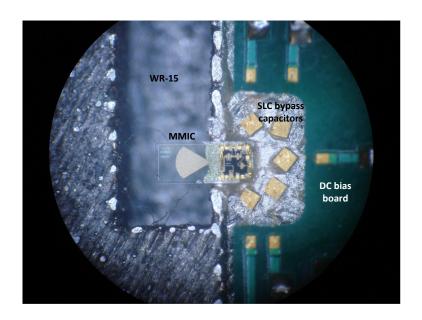

| 3.29 | Complete V-Band oscillator assembly with MMIC, bypass capacitors, bias board and                                       |    |

|      | DC wirebond connections. The waveguide housing is fabricated in Al with traditional                                    |    |

|      | machining. The waveguide is WR-15 and made of Al                                                                       | 63 |

| 3.30 | Complete V-Band oscillator assembly with MMIC, bypass capacitors, bias board and                                       |    |

|      | DC wirebond connections. The waveguide housing is fabricated in AlSi10Mg with                                          |    |

|      | AM                                                                                                                     | 63 |

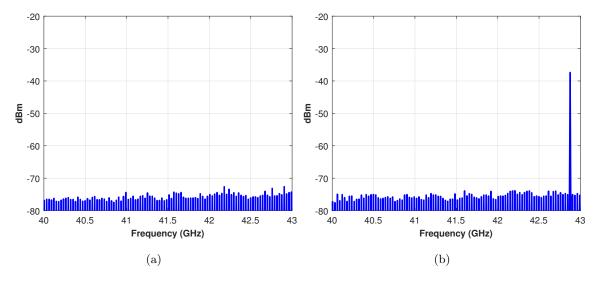

| 3.31 | (a) The noise floor of the N9030A. b) The output tone frequency and power for $V_c$                                    |    |

|      | = -2 V. The tone power is -37.38 dBm and the frequency is 42.76 GHz                                                    | 64 |

| 3.32 | (a) The output tone frequency and output power for $V_c = -3 \mathrm{V}$ . The tone power                      |    |

|------|----------------------------------------------------------------------------------------------------------------|----|

|      | is $-38.82\mathrm{dBm}$ and the frequency is $42.88\mathrm{GHz}$ . (b) The output tone frequency and           |    |

|      | output power for $V_c = -6 \mathrm{V}$ . The tone power is $-35.84 \mathrm{dBm}$ and the frequency is          |    |

|      | 40.99 GHz                                                                                                      | 65 |

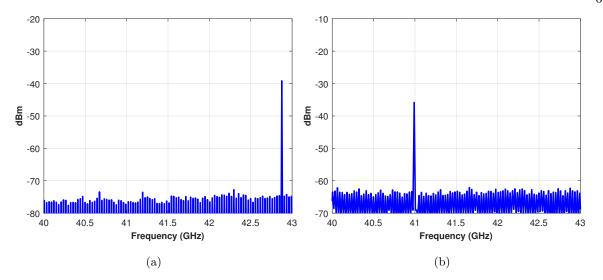

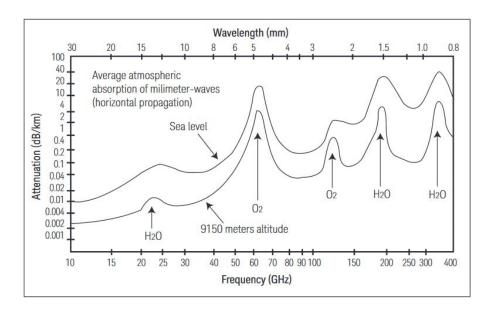

| 4.1  | Atmospheric attenuation from 10 to $400\mathrm{GHz}$ at sea level and approximately $9\mathrm{km}$ .           |    |

|      | A region of relatively low attenuation occurs between 200-300 GHz                                              | 67 |

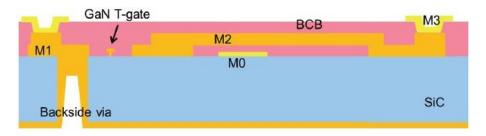

| 4.2  | Cross-section view of CMP Cu interconnects combined with GaN-on-SiC MMIC                                       |    |

|      | technology. Source: [4] $\dots$                                                                                | 70 |

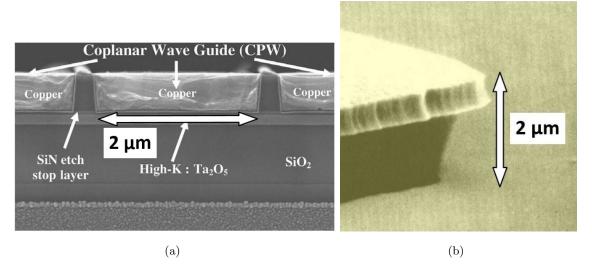

| 4.3  | a) An example of a CPW line fabricated in a Cu damascene process on Si. The                                    |    |

|      | profile of the traces is vertically uniform. (b) The non-uniform vertical profile of a                         |    |

|      | microstrip metal trace that has been developed with a photoresist liftoff process [5], [6]                     | 70 |

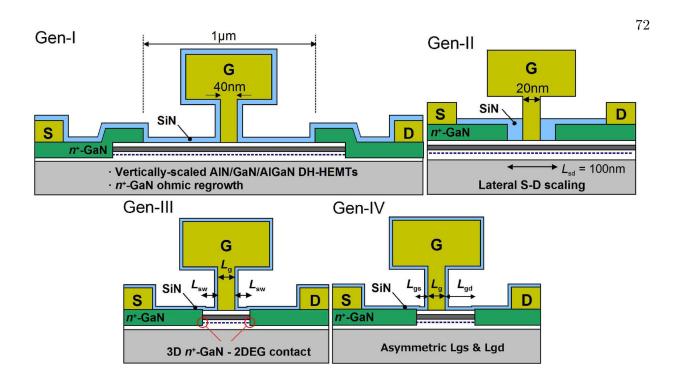

| 4.4  | The various generations of transistor technology scaling at HRL. The current work                              |    |

|      | was performed with Gen-IV technology. Source: [7]                                                              | 72 |

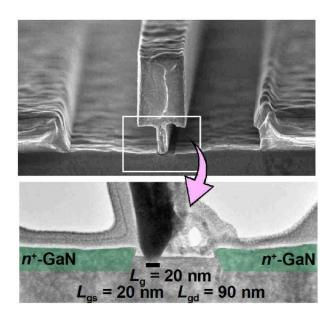

| 4.5  | SEM photograph of HRL's Generation-IV T-gate. The gate length is 20 nm and the                                 |    |

|      | asymmetric-self-aligned gate fabrication process allows for a $L_{gs}=20\mathrm{nm}$ and $L_{gd}=$             |    |

|      | 90 nm. Source: [8]                                                                                             | 72 |

| 4.6  | $G_{max}$ (black) and K (blue dashed) for the $4\mathrm{x}20\mu\mathrm{m}$ device. The discontinuity at        |    |

|      | approximately 447 GHz corresponds to where K $> 1$                                                             | 74 |

| 4.7  | $G_{max}$ (black) and K (blue dashed) for the $4 \mathrm{x} 100  \mu\mathrm{m}$ device. The discontinuities at |    |

|      | approximately 278 and 447 GHz correspond to where $K>1$ . This device has a                                    |    |

|      | limited unconditionally stable region between the two frequency points                                         | 74 |

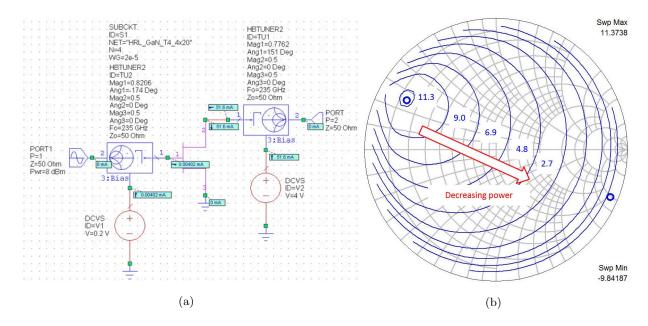

| 4.8  | (a) Single $4x20\mu\mathrm{m}$ device load and source pull simulation setup. (b) The output                    |    |

|      | power contours on the Smith chart show the optimal load impedance for maximum                                  |    |

|      | power                                                                                                          | 75 |

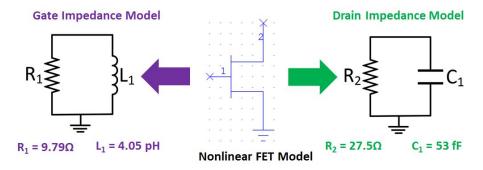

| 4.9  | The optimal gain and output power equivalent gate and drain models for the $4x20 \mu m$                                            |    |

|------|------------------------------------------------------------------------------------------------------------------------------------|----|

|      | device. The gate behaves slightly inductive and the aggressive scaling of the tran-                                                |    |

|      | sistor geometry results in a very low $(53\mathrm{fF})$ equivalent drain output capacitance                                        | 76 |

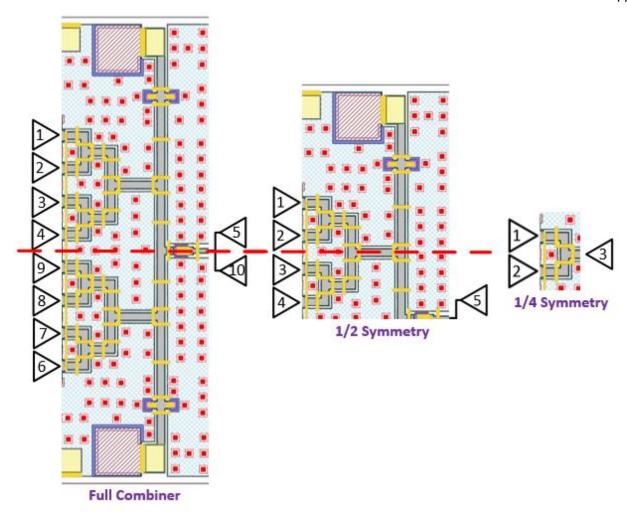

| 4.10 | The 8-way combiner and half and quarter symmetrical sections. The half and quarter                                                 |    |

|      | symmetrical networks are analyzed for odd mode instabilities                                                                       | 77 |

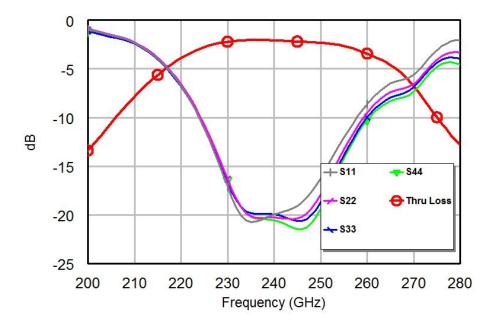

| 4.11 | Simulated 8-way combiner S-parameters with even mode excitation. The results are                                                   |    |

|      | from an EM simulation of the entire combiner. The loss mid-band is $2.1\mathrm{dB.}$                                               | 79 |

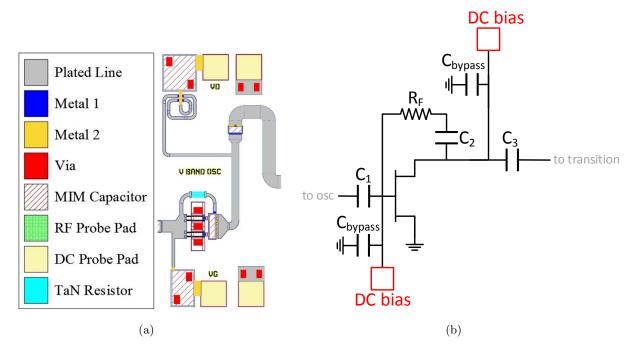

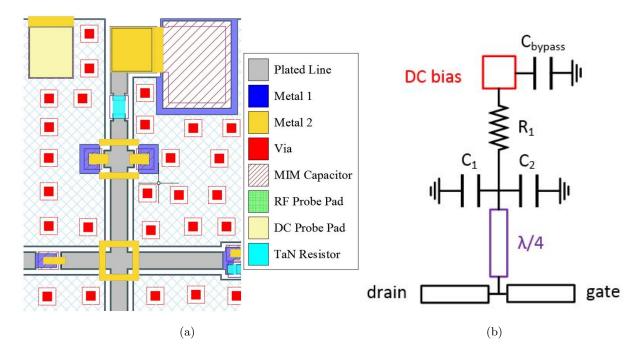

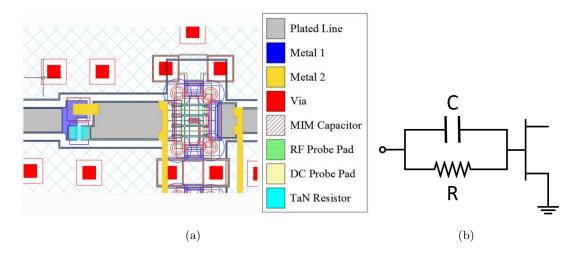

| 4.12 | (a) The bias tee structure used in the MMIC PA design. The small shunt capacitors                                                  |    |

|      | (red hatch pattern over M1) are a quarter-wave from the interstage connecting lines.                                               |    |

|      | The series resistor (cyan) is for stability. (b) The schematic view of the bias tee                                                |    |

|      | structure                                                                                                                          | 80 |

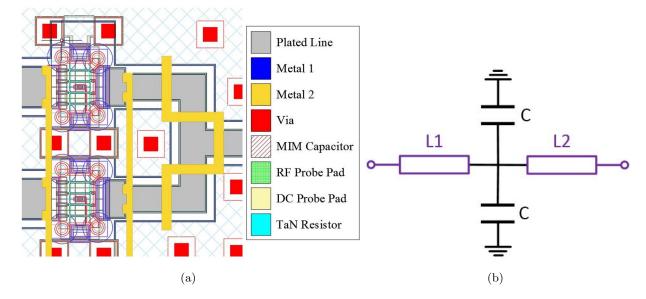

| 4.13 | a) The layout view of multiple air bridges at CPW line bends and discontinuities. b)                                               |    |

|      | The circuit schematic for the air bridge. C $\approx 4.5\mathrm{fF}$ and this can be a minor tuning                                |    |

|      | element in the design process                                                                                                      | 81 |

| 4.14 | The input impedance of the air bridge network with increasing length $L_1$ . The total                                             |    |

|      | length of $L_1+L_2$ is kept constant and $L_1$ ranges from 50 to 200 $\mu \mathrm{m}$ in 50 $\mu \mathrm{m}$ steps.                | 82 |

| 4.15 | a) The layout view of the parallel RC network in series with the transistor gate. b)                                               |    |

|      | The circuit schematic of the parallel RC network. R = 54.6 $\Omega$ and C = 42.2 fF. $$                                            | 82 |

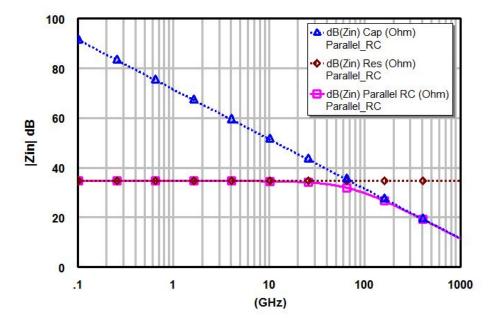

| 4.16 | Impedance plot of the parallel RC stability network at each device gate. The                                                       |    |

|      | impedance of the network (pink) is the parallel summation of the capacitor (blue) and                                              |    |

|      | the resistor (brown). The response of the network is the inversion of the impedance                                                |    |

|      | plot shown and acts as a high-pass filter                                                                                          | 83 |

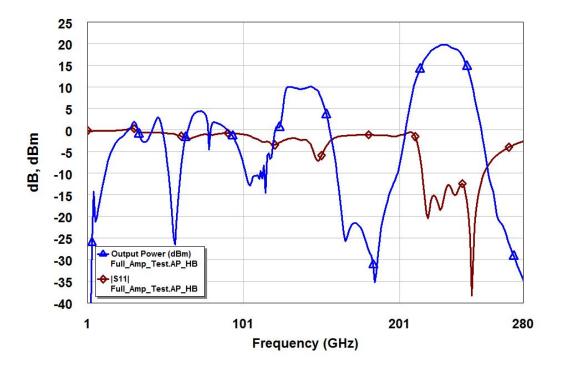

| 4.17 | The $ S_{11} \mathrm{dB}$ (brown) and $ S_{21} \mathrm{dB}$ (blue) for the 4-stage amplifier with the $4\mathrm{x}20\mu\mathrm{m}$ |    |

|      | nonlinear model. There is significant gain at lower frequencies. For a $10\mathrm{dBm}$ input                                      |    |

|      | power, the simulation shows $>20\mathrm{dBm}$ output power and $10\mathrm{dB}$ large signal gain                                   | 84 |

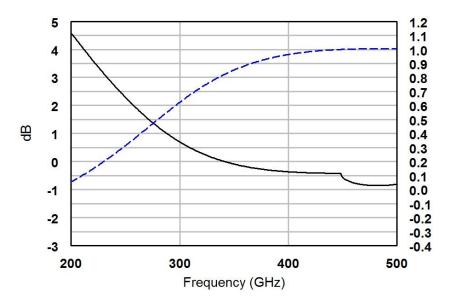

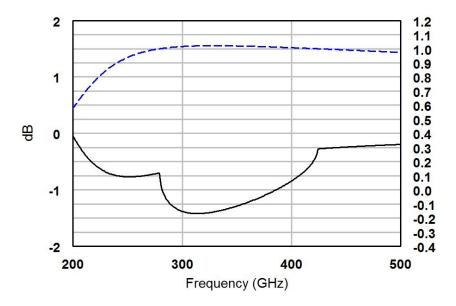

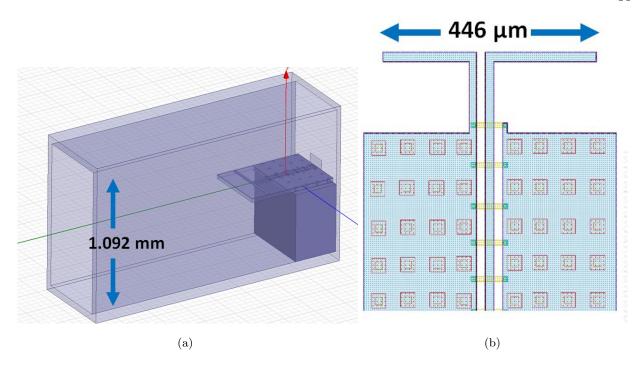

| 4.18 | a) Simulation view of the dipole probe for CPW-to-waveguide transition. b) Detail                                                  |    |

|      | of the dipole transition. The dipole is approximately $1\lambda$ at $235\mathrm{GHz}$                                              | 85 |

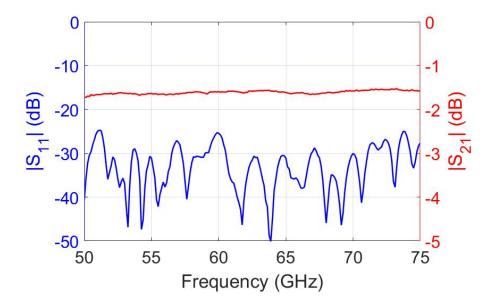

| 4.19 S-parameters of the CPW-to-waveguide transition. $ S_{21}  dB$ is in green and $ S_{11}  dI$ |                                                                                                                                    |    |  |  |

|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

|                                                                                                   | in red                                                                                                                             | 85 |  |  |

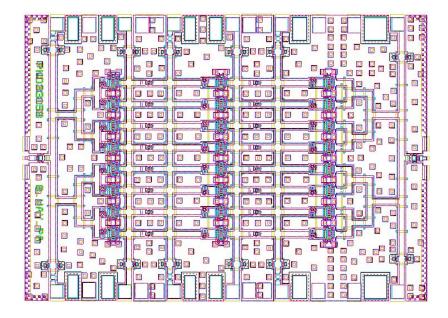

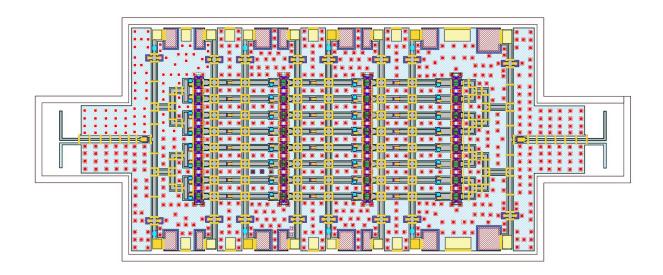

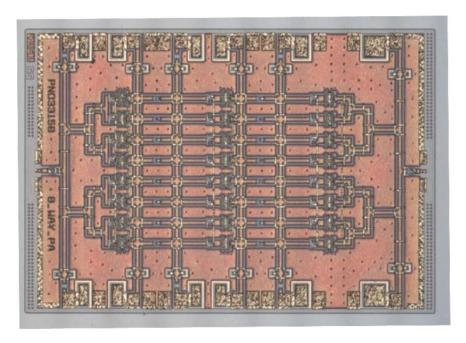

| 4.20                                                                                              | Layout view of the 3-stage 8-way combined PA. The MMIC dimensions are $2.2 \mathrm{x} 1.65  \mathrm{mm}^2$                         | 86 |  |  |

| 4.21                                                                                              | Detailed layout view of the 4-stage 8-way combined PA with CPW-to-waveguide                                                        |    |  |  |

|                                                                                                   | transitions on input and output. The MMIC dimensions are $4.4x1.8\mathrm{mm}^2.$                                                   | 86 |  |  |

| 4.22                                                                                              | Microphotograph of the fabricated 3-stage, 8-way combined MMIC PA. The MMIC                                                        |    |  |  |

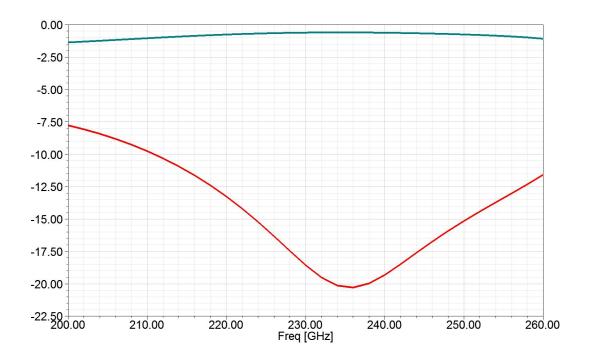

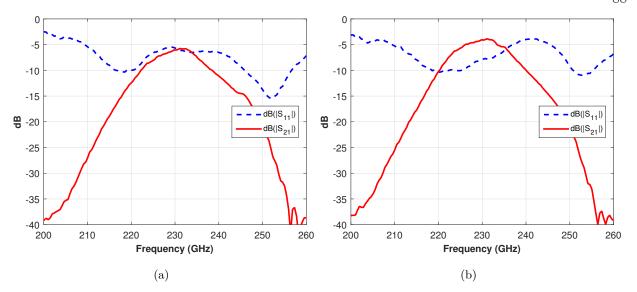

|                                                                                                   | dimensions are $2.2x1.65 \mathrm{mm}^2$                                                                                            | 87 |  |  |

| 4.23                                                                                              | Measured $ S_{11} $ dB and $ S_{21} $ dB for the 3-stage, 8-way combined PA. $ S_{11} $ is shown                                   |    |  |  |

|                                                                                                   | in dashed lines                                                                                                                    | 88 |  |  |

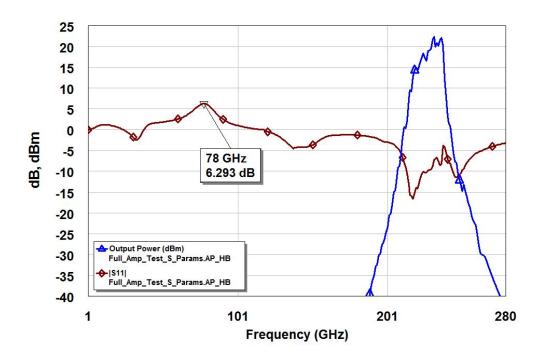

| 4.24                                                                                              | The $ S_{11} \mathrm{dB}$ (brown) and $ S_{21} \mathrm{dB}$ (blue) for the 4-stage amplifier with the $4\mathrm{x}20\mu\mathrm{m}$ |    |  |  |

|                                                                                                   | S-parameters. There is a significant positive $ S_{11} $ at 78 GHz and this is indicative of                                       |    |  |  |

|                                                                                                   | an out of band oscillation                                                                                                         | 88 |  |  |

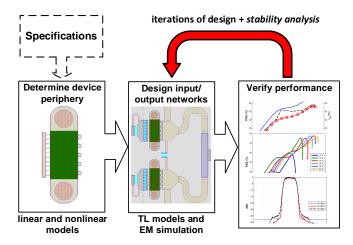

| 5.1                                                                                               | Typical MMIC PA design flow. The boxes represent a step in the process with the                                                    |    |  |  |

|                                                                                                   | additional text representing what tools and methods are used to achieve the step                                                   | 91 |  |  |

| 5.2                                                                                               | Two-transistor ring oscillator in [9]. Components with fixed values: $R_1 = 10 \Omega,  L_1$                                       |    |  |  |

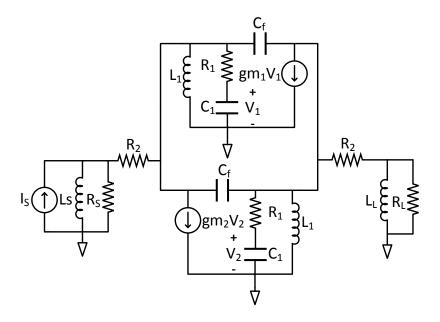

|                                                                                                   | = 560 pH, $g_{m1}$ = 500 mS, $g_{m2}$ = 400 mS, $C_f$ = 0.1 pF, $C_1$ = 16 pF                                                      | 93 |  |  |

| 5.3                                                                                               | (a) Polar plot of the NDF for case I from Table 5.1. (b) K (blue-square) and $B_1$                                                 |    |  |  |

|                                                                                                   | (pink) for case I. The NDF correctly predicts instability and the $K$ -factor incorrectly                                          |    |  |  |

|                                                                                                   | predicts stable behavior                                                                                                           | 94 |  |  |

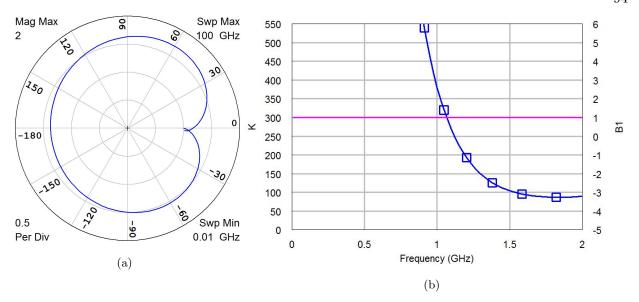

| 5.4                                                                                               | (a) Polar plot of the NDF for case II in Table 5.1. (b) K (blue-square) and $B_1$ (pink)                                           |    |  |  |

|                                                                                                   | for case II. The NDF correctly predicts instability and the $K$ -factor correctly predicts                                         |    |  |  |

|                                                                                                   | unstable behavior                                                                                                                  | 94 |  |  |

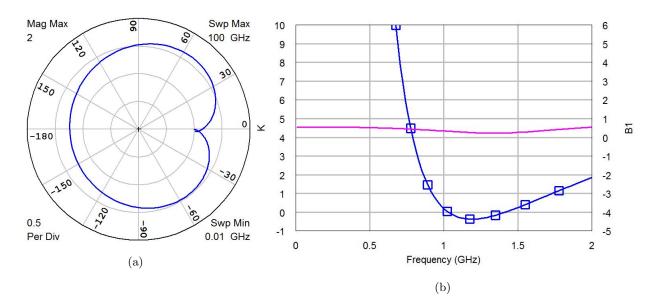

| 5.5                                                                                               | (a) Polar plot of the NDF for case III (b) K (blue-square) and $B_1$ (pink) for case III.                                          |    |  |  |

|                                                                                                   | The NDF correctly predicts instability and the $K$ -factor correctly predicts unstable                                             |    |  |  |

|                                                                                                   | behavior                                                                                                                           | 95 |  |  |

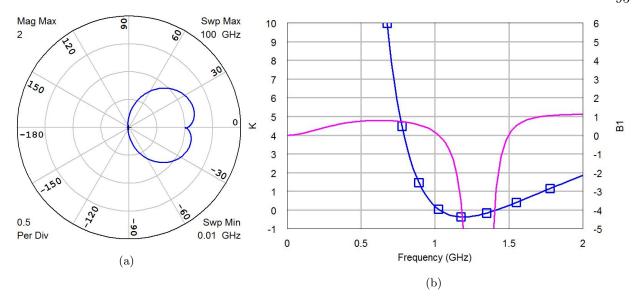

| 5.6  | (a) Polar plot of the NDF for case IV (b) K (blue-square) and $B_1$ (pink) for case IV.            |

|------|----------------------------------------------------------------------------------------------------|

|      | The NDF correctly predicts stability and the $K$ -factor incorrectly predicts unstable             |

|      | behavior                                                                                           |

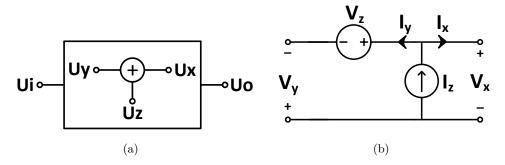

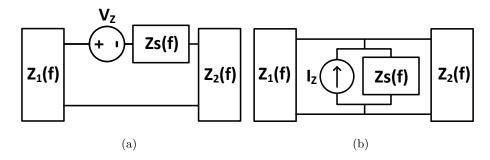

| 5.7  | (a) Network diagram with injection source. (b) Injection source template used in                   |

|      | this paper. $U_z$ will be $V_z$ or $I_z$ for voltage or current injection, respectively 97         |

| 5.8  | Single source injection schemes, (a) voltage injection and (b) current injection. The              |

|      | impedances to the left and right of the injection location are frequency and possibly              |

|      | input drive dependent                                                                              |

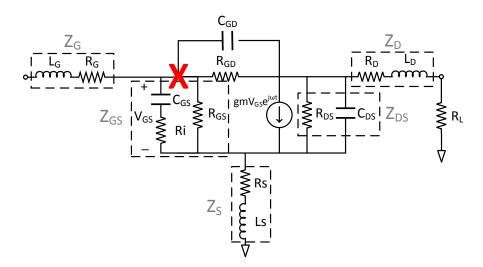

| 5.9  | Small signal HEMT model with lead parasitics, $C_{GD}$ and $C_{GS}$ and parasitic paths            |

|      | $R_{GS}$ , $R_{GD}$ and $R_{DS}$ . The current source injection location is at the node connecting |

|      | $R_{GD}$ to $R_{GS}$ , marked with a red X. The simulation is performed first without and          |

|      | later including $C_{GD}$ , $C_{GS}$ , and $R_i$                                                    |

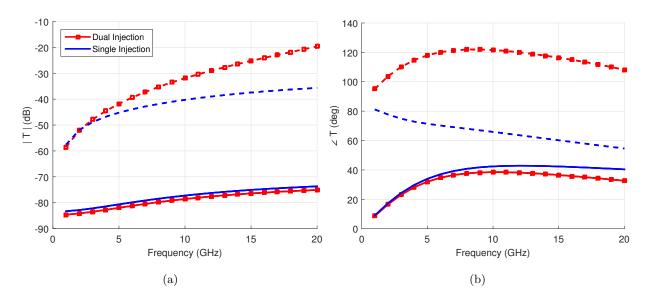

| 5.10 | Loop gain magnitude (a) and phase (b) for single and dual-injection with $C_{GD}$ , $C_{GS}$ ,     |

|      | and $R_i$ (dashed line) and without (solid line)                                                   |

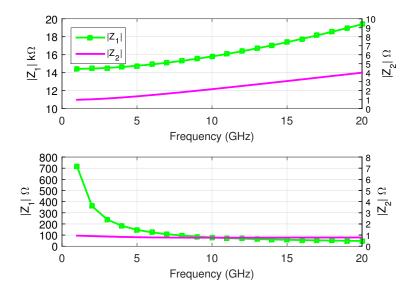

| 5.11 | Impedance relationship for the FET model without (top) and with $C_{GD}$ , $C_{GS}$ , and          |

|      | $R_i$ , (bottom) of the left $(Z_1)$ and right $(Z_2)$ networks at the injection plane for single  |

|      | current source injection                                                                           |

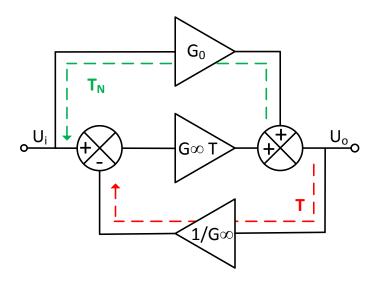

| 5.12 | Alternative feedback model. The additional path for forward transmission is a result               |

|      | of the GFT                                                                                         |

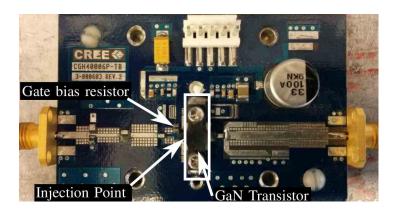

| 5.13 | CREE demonstration board for the CGH40006P $6\mathrm{W}$ GaN transistor. The gate bias             |

|      | resistor was removed to cause the amplifier to become unstable                                     |

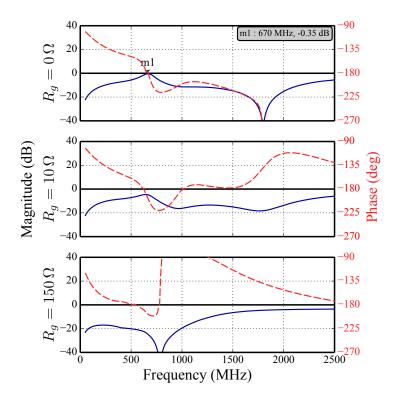

| 5.14 | Simulated loop gain of the demonstration board at $0\mathrm{dBm}$ input power; magnitude           |

|      | (solid line) and phase (dotted line). With $R_g{=}0\Omega,$ the phase passes through $180^\circ$   |

|      | at approximately $670\mathrm{MHz}$ while the amplitude is at $-0.4\mathrm{dB}$ . This shows a high |

|      | probability of oscillation. However, with $R_g = 10 \Omega$ , the gain margin increases to 5 dB    |

|      | and a $150\Omega$ resistor eliminates the peaking in the loop gain                                 |

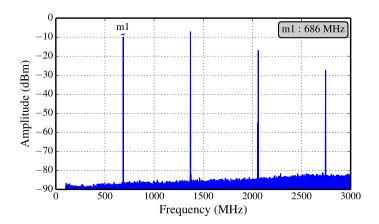

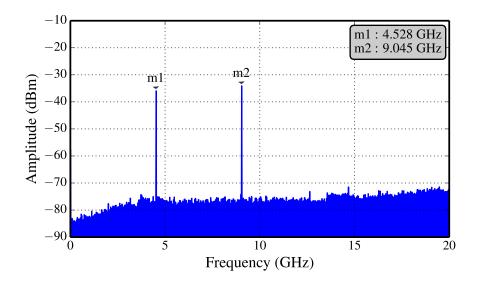

| 5.15 | Measured power spectrum of the CREE development board. The frequency of os-                                                |

|------|----------------------------------------------------------------------------------------------------------------------------|

|      | cillation is at 686 MHz with a bias of $V_g$ =-2.7 V and a 0 $\Omega$ resistor on the gate bias                            |

|      | line. The amplifier is designed to work from $500\mathrm{MHz}$ to $6\mathrm{GHz}$ and the harmonics                        |

|      | of the oscillation are also visible at the output                                                                          |

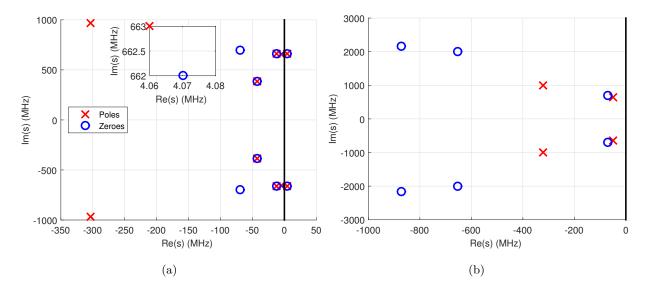

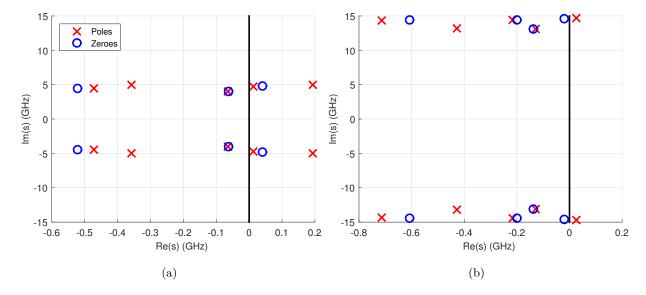

| 5.16 | Pole-zero plots of the transfer functions of the CREE evaluation board with $0\Omega$ (a)                                  |

|      | and $10\Omega$ (b) gate resistors. The single injection technique identifies RHP poles at                                  |

|      | 662 MHz that are not canceled by the nearby RHP zeroes. The inset shows the                                                |

|      | quasi-cancellation                                                                                                         |

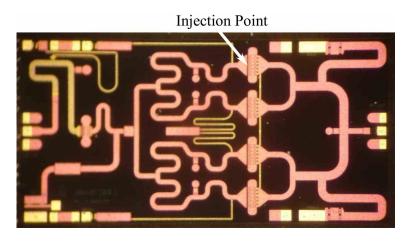

| 5.17 | X-band two-stage GaN MMIC designed for $10\mathrm{W}$ that after fabrication, was found                                    |

|      | to be highly unstable. The chip is $4\mathrm{mm}\times2.3\mathrm{mm}.$ All devices are $12\mathrm{x}100\mu\mathrm{m}.$ 110 |

| 5.18 | Measured power spectrum of the MMIC. The frequency of oscillation is at $4.528\mathrm{GHz}$                                |

|      | with a bias of $V_{g1}$ =-3.25 V on the first stage and $V_{g2}$ =-3.6 V on the second stage.                              |

|      | The vertical amplitude scale is relative because of the use of a coupler at the output                                     |

|      | of the PA                                                                                                                  |

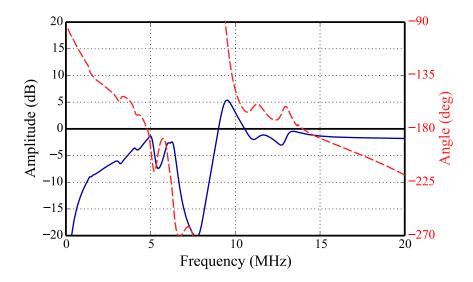

| 5.19 | Simulated two-stage X-band GaN MMIC PA loop gain; magnitude (solid line) and                                               |

|      | phase (dotted line)                                                                                                        |

| 5.20 | Pole-zero plots of the transfer functions of the X-band GaN MMIC PA plotted from                                           |

|      | (a) 1-6 GHz with 0 dBm input power and (b) 6 - 15 GHz with 8 dBm input power.                                              |

|      | Predicted instabilities at $4.69$ , $4.99\mathrm{GHz}$ in (a) and $14.67\mathrm{GHz}$ in (b) are close to                  |

|      | measured results and verified by the dual-injection technique                                                              |

| 6.1  | Straight 10 cm WR-10 waveguide model used for AM fabrication                                                               |

| 6.2  | WR-10 20 dB directional coupler model used for AM fabrication                                                              |

| 6.3  | Straight $10\mathrm{cm}$ WR-10 waveguides implemented in a variety of materials. From left                                 |

|      | to right: metal (Cu) coated plastic (MCP), GRCop-84 (Cu), Inconel 625 (Ni), and 3                                          |

|      | AlSi10Mg with different laser settings                                                                                     |

| 6.4  | From left to right: WR-10 20 dB directional couplers in metal (Cu) coated plastic                         |

|------|-----------------------------------------------------------------------------------------------------------|

|      | (MCP) and AlSi10Mg with different laser settings                                                          |

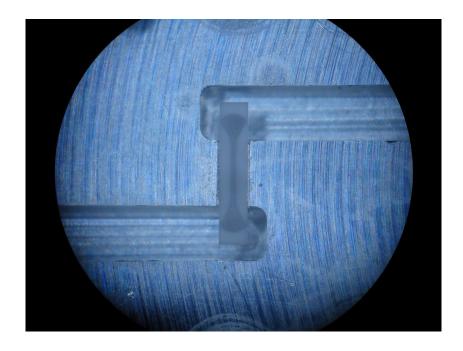

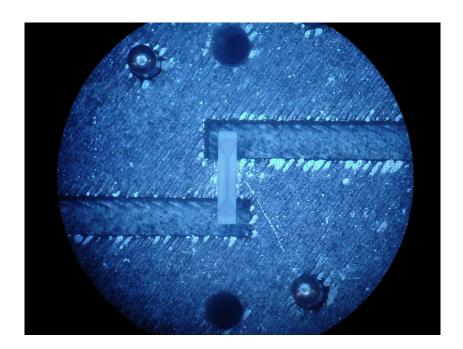

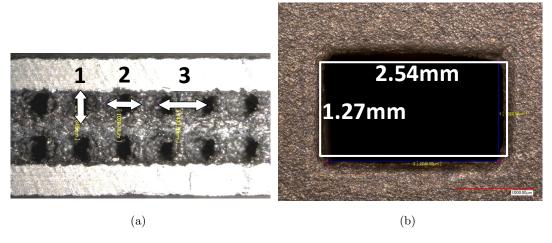

| 6.5  | a) Microphotograph of the interior of the $20\mathrm{dB}$ directional coupler after destructive           |

|      | testing. White arrows show fabricated dimensions: 1) 1020 $\mu\mathrm{m}$ hole diameter 2) a              |

|      | $818\mu\mathrm{m}$ hole diameter and 3) a $1433\mu\mathrm{m}$ hole-to-hole spacing. b) Aperture dimension |

|      | deviation for the Cu waveguide. Inset is the correct WR-10 dimensions, as fabricated:                     |

|      | 2.25 mm x 1.39 mm                                                                                         |

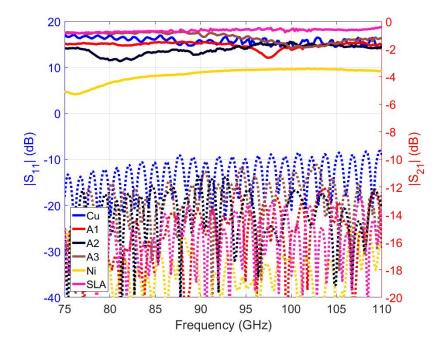

| 6.6  | S-parameter results for the various fabricated WR-10 $10\mathrm{cm}$ waveguide sections. The              |

|      | calibration $ S_{11} $ was $<$ -20 dB and it is assumed the standing wave pattern is due to               |

|      | aperture dimension deviation and/or imperfect flange mating                                               |

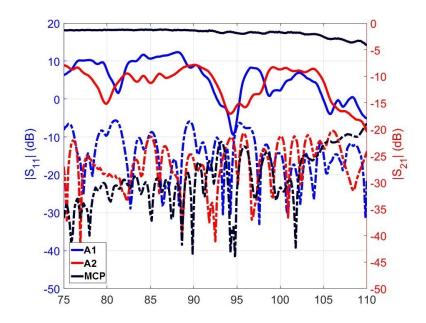

| 6.7  | Measured $ S_{11} $ and $ S_{21} $ for the various fabricated WR-10 20 dB directional couplers.           |

|      | $ S_{11} $ is shown in dashed lines                                                                       |

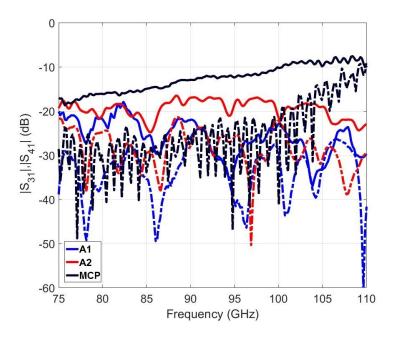

| 6.8  | Measured coupling, $ S_{31} $ , and isolation, $ S_{41} $ , for the various fabricated WR-10 20 dB        |

|      | directional couplers. The isolation, $ S_{41} $ , is shown in dashed lines                                |

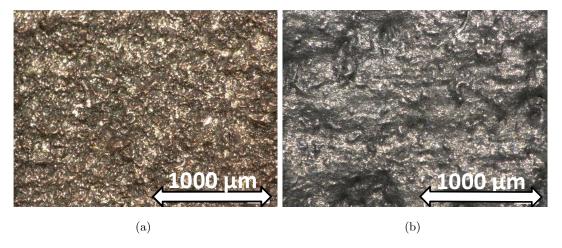

| 6.9  | a) WR-10 GRC<br>op-84 and b) AlSi10Mg A3 $10\mathrm{cm}$ waveguide section interior surface               |

|      | at 200x zoom                                                                                              |

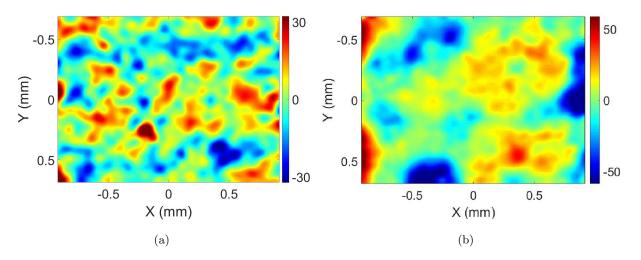

| 6.10 | a) Measured WR-10 GRC<br>op-84 $10\mathrm{cm}$ waveguide topographical color map showing                  |

|      | $\pm~30\mu\mathrm{m}$ height deviation. b) Measured WR-10 AlSi<br>10Mg A3 10 cm waveguide to-             |

|      | pographical color map showing $\pm$ 50 $\mu$ m height deviation                                           |

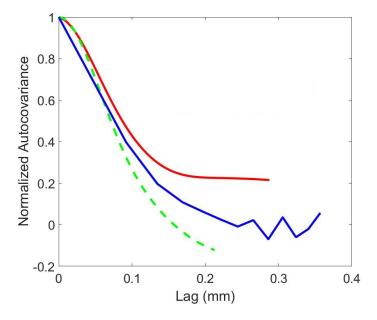

| 6.11 | Normalized autocorrelation $L_q$ , for GRCop-84. Autocorrelation lengths $L_h$ , horizon-                 |

|      | tal, and $L_v$ , vertical show the computed $L_q$ is a good fit to the ACV model before                   |

|      | edge effects in the FOV limit affect accuracy                                                             |

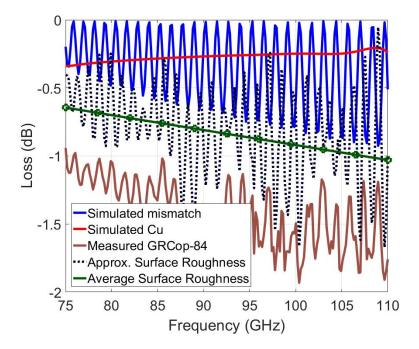

| 6.12 | Different loss mechanisms for GRCop-84 AM waveguide. The surface roughness loss                           |

|      | is approximated by subtracting simulated losses (mismatch from aperture dimension                         |

|      | deviations and idealized Cu loss) from the measured S-parameter data. Average                             |

|      | surface roughness loss (green) is the moving average of the calculated approximate                        |

|      | surface roughness loss                                                                                    |

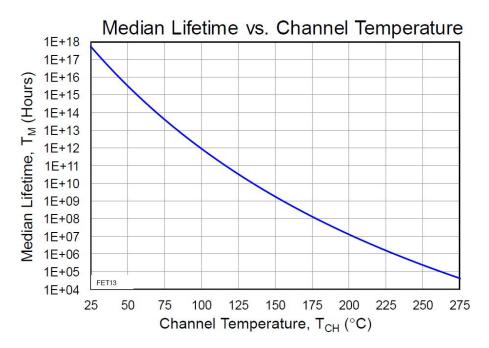

| 6.13 | Mean time to device failure based on junction temperature for an X-band, 60-W                       |

|------|-----------------------------------------------------------------------------------------------------|

|      | $\operatorname{GaN}$ PA. MTTF > one million hours is a commonly specified standard in military      |

|      | and SATCOM applications. Source: [10]                                                               |

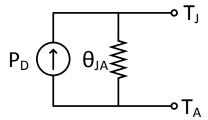

| 6.14 | The equivalent electrical circuit model for thermal operation of a transistor amplifier.            |

|      | Current, resistance and voltage are analogous to dissipated power, thermal resistance,              |

|      | and temperature                                                                                     |

| 6.15 | A more complex equivalent circuit model for thermal operation. The thermal re-                      |

|      | sistances represent interfaces in the physical layout of the transistor amplifier. The              |

|      | capacitors represent thermal inertia of the layers between the interfaces                           |

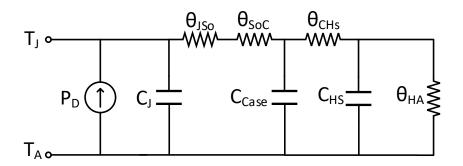

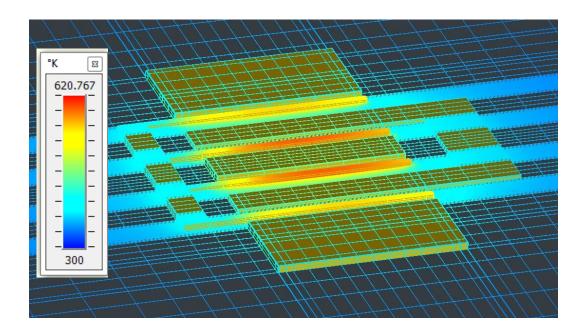

| 6.16 | The HRL T4 $4\mathrm{x}20\mu\mathrm{m}$ device with 3.3 W dissipated power. The channel temperature |

|      | is shown in the legend and peaks at $550\mathrm{K}$                                                 |

| 6.17 | The mesh for the FEM thermal simulation of the HRL T4 4x20 $\mu$ m device 132                       |

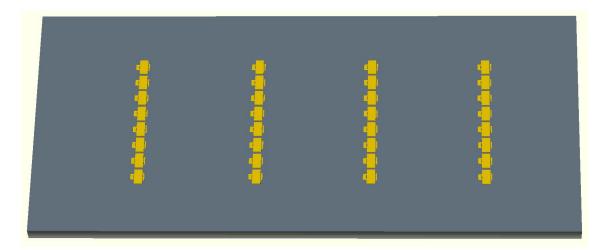

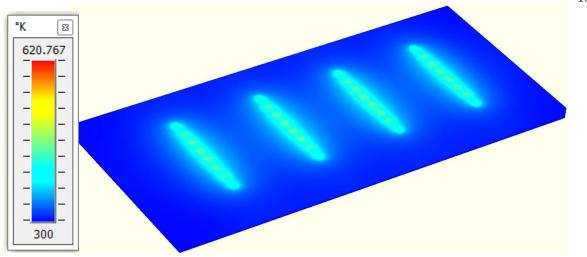

| 6.18 | The thermal analysis simulation setup. The devices are those shown in Fig. 6.16                     |

|      | arranged in the same X-Y mapping as the full amplifier. The MMIC dimensions are                     |

|      | 4.4 mm x 1.8 mm                                                                                     |

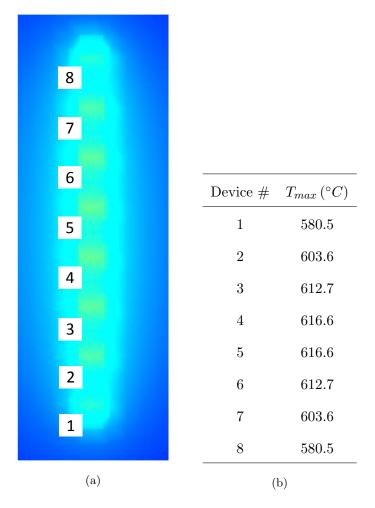

| 6.19 | The 4-stage 8-way power combined MMIC PA thermal solution. The maximum                              |

|      | temperature is 620 K, a 320 $^{\circ}\mathrm{C}$ temperature rise. The MMIC dimensions are 4.4 mm   |

|      | x 1.8 mm                                                                                            |

| 6.20 | a) The device numbers for the 8-way combiner and b) the maximum device temper-                      |

|      | atures, $T_{max}$                                                                                   |

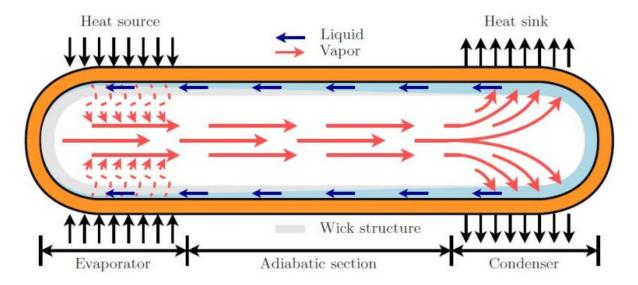

| 6.21 | The operation of a fixed-conduction heat pipe. Source: [11]                                         |

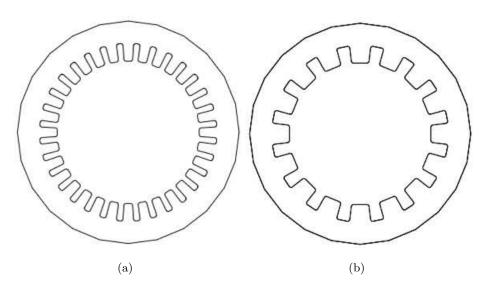

| 6.22 | a) Heat Pipe 1 wick profile. The total outside diameter (OD) is $10\mathrm{mm}$ . (b) Heat          |

|      | Pipe 2 wick profile. The number of teeth is reduced and the spacing between doubled.137             |

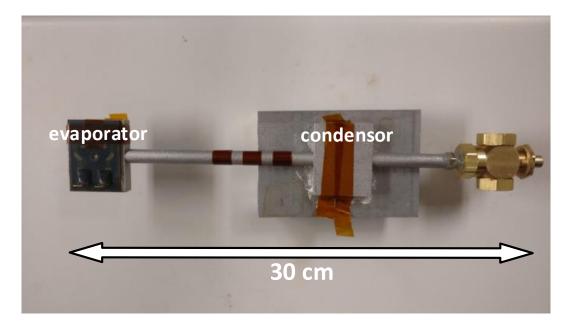

| 6.23 | Setup for heat pipe testing. The thermocouples are attached to the outside of the                   |

|      | condenser and evaporator. The temperature difference between the evaporator and                     |

|      | condenser is $\Delta T$ . The total pipe length is 30 cm                                            |

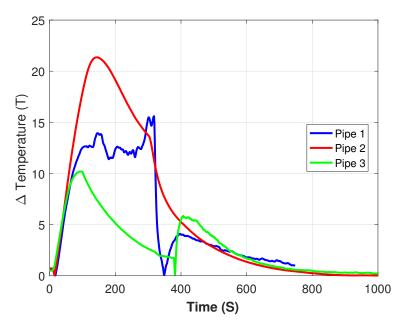

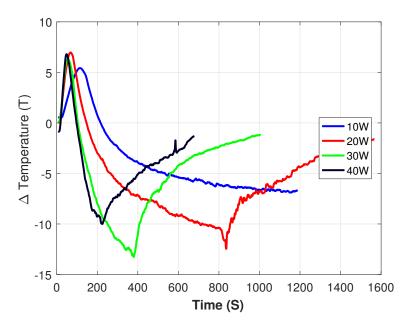

| 6.24 | $\Delta T$ for different heat pipe wick structures over time with a 20 W thermal load 139           |

| 6.25 | Pipe 3 $\Delta T$ for various thermal loads. The thermal conductivity is a function of |

|------|----------------------------------------------------------------------------------------|

|      | dissipated power and varies over the power range                                       |

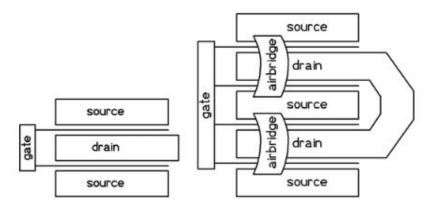

| 7.1  | A symmetrical two finger HEMT shown on the left. Scaling the device for power          |

|      | handling or thermal management creates asymmetrical devices and can cause oscil-       |

|      | lations. Source: [12]                                                                  |

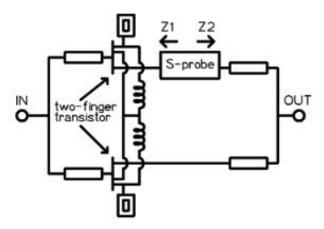

| 7.2  | The simulation setup for determining the stability of asymmetric devices. Instead      |

|      | of a S-probe, the stability analysis in chapter 5 could be used to validate stability. |

|      | Source: [12]                                                                           |

| 7.3  | S-parameters for a 11 cm straight waveguide section fabricated in maraging steel 145   |

#### Chapter 1

#### **Introduction and Motivation**

#### Contents

| 1.1 | Introduction to MMIC Technology and Design | 5  |

|-----|--------------------------------------------|----|

| 1.2 | Introduction to Additive Manufacturing     | 9  |

| 13  | Thesis Overview                            | 10 |

Advances in MMIC design and fabrication have been the driver for continually improving performance in wireless systems such as cellular phone technology, satellite communications, military and automotive radar systems, electronic warfare, radiometers, and remote sensing technology. A MMIC is a monolithic microwave integrated circuit, such as the ones designed and fabricated in this work and shown in Figs. 1.2a - 1.2d. The monolithic part of the name refers to the fact that the circuit is fabricated on a single piece of semiconductor material, usually GaAs, GaN, InP or SiGe. The microwave part of the name refers to the fact that the circuit is operating between 300 MHz to 300 GHz [13]. The last important part of the name is integrated which refers to the fact that the MMIC does not contain a single transistor or device, but a mix of transistors, diodes, capacitors, inductors, transmission lines, integrated antennas, and RF and DC interface structures. Further integration, such as on-die power conversion and control circuits is an on-going research topic in this field. Similar to silicon developments, one day an entire RF system might be on a single chip (system-on-a-chip). The design of millimeter-wave MMICs, that is MMICs that operate above 30 GHz, is the main focus of this work.

MMIC design and fabrication is a relatively new field, the first MMIC was reported in 1976

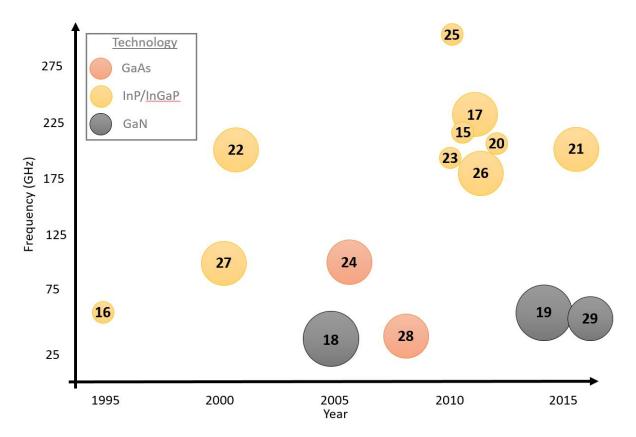

in [14] and advances in output power, gain, operating frequency, and efficiency are continually being made. In Fig. 1.1 the output power, frequency of operation and year of reported result for various millimeter-wave MMIC PAs and oscillators is shown. There are few results before 1995. A summary of the technology progression is also shown in table form in Table 1.1.

Figure 1.1: Millimeter-wave MMIC technology progression over the years with a variety of output power levels, operating frequencies and different fabrication technology. The three marker sizes represent  $<10\,\mathrm{mW}$ , between  $10\,\mathrm{mW}$  and  $1\,\mathrm{W}$ , and  $>1\,\mathrm{W}$ .

Table 1.1: Summary of results in the above MMIC technology figure.

| Freq. (GHz) | $P_{out} (\mathrm{mW})$ | Tech.                | Year | Ref. |

|-------------|-------------------------|----------------------|------|------|

| 220         | 10                      | InP                  | 2010 | [15] |

| 60          | 8.128                   | InP                  | 1995 | [16] |

| 220         | 50                      | InP                  | 2010 | [17] |

| 28-34       | 4000                    | $\operatorname{GaN}$ | 2005 | [18] |

| 70          | 1300                    | $\operatorname{GaN}$ | 2014 | [19] |

| 220         | 0.724                   | InP                  | 2011 | [20] |

| 200         | 220                     | InP                  | 2015 | [21] |

| 205         | 250                     | InP                  | 2001 | [22] |

| 192         | 7.94                    | InP                  | 2009 | [23] |

| 90          | 267                     | GaAs                 | 2005 | [24] |

| 324         | 1.3                     | InP                  | 2008 | [25] |

| 195         | 100                     | InP                  | 2013 | [26] |

| 90          | 427                     | InP                  | 1999 | [27] |

| 46          | 151.35                  | GaAs                 | 2007 | [28] |

| 70          | 800                     | GaN                  | 2016 | [29] |

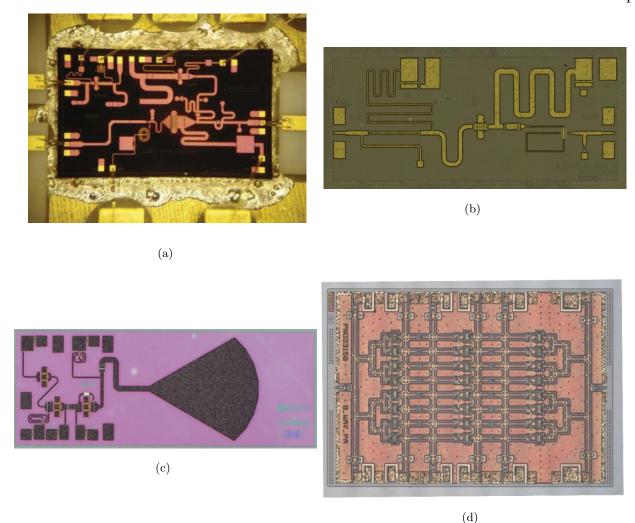

The goal of this thesis is to explore non-conventional circuit designs using advanced GaN MMIC technologies, with a focus on increasing operating frequency and output power. A summary of the MMICs designed towards this goal is shown in Figs. 1.2a - 1.2d. Starting from a 0.15  $\mu$ m gate length commercial GaN process, the first harmonically-injected 10-GHz MMIC PA is successfully implemented and shows the possibility of achieving simultaneous high efficiency and linearity without analog or digital predistortion (DPD). The output harmonic injection MMIC PA demonstrated a PAE of 70% at 10.6 GHz with 3.6 W of output power in a 3.8 mm x 2.3 mm footprint. Next, a 10 GHz Class-E amplifier was designed and fabricated in a 20 nm gate length,  $f_T > 300$  GHz, process to investigate the effects of gate geometry scaling on efficiency.  $f_T$ , the transition frequency, is the maximum frequency where a transistor can amplify. The Class-E amplifier achieved > 55% efficiency at 9 GHz with 8 dB of gain. The third design, Fig. 1.2c, is a U- and V-band (40-60 and 50-75 GHz respectively) VCO designed in a 90 nm gate length process. Last, in Fig. 1.2d, the same  $f_T > 300$  GHz process was used to fabricate a power combined 235 GHz GaN MMIC.

Figure 1.2: (a) 10 GHz output harmonic injection MMIC PA (b) 10 GHz Class-E amplifier MMIC PA (c) V-band VCO (d) 235 GHz 8-way combined MMIC PA.

Millimeter-wave applications require that the MMIC be packaged properly and typically interface to waveguide for test and integration. To investigate new methods of packaging and interfacing with millimeter-wave MMICs, the V-band VCO and 235 GHz power combined PA include microstrip-to-waveguide or CPW-to-waveguide transitions. While this work does not focus on the fabrication technology of these devices, the design of a MMIC inherently requires some knowledge of the relevant manufacturing terms and of how planar transistor layouts look. An overview of the important terms used in this thesis is given so that the reader can understand the concepts they relate to. Last, an overview of each thesis chapter is presented.

#### 1.1 Introduction to MMIC Technology and Design

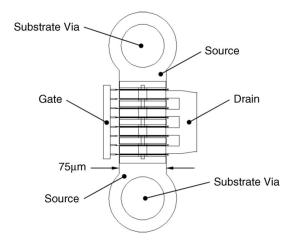

The work in this thesis revolves around access to high-frequency transistor technology and low-loss passive interconnects and component technology. The layout view of a typical high-frequency transistor used in this work is shown in Fig. 1.3. The important parameters are the number of gate fingers, the gate width, and the gate length. In Fig. 1.3, the transistor has a 75  $\mu$ m gate width, 8 gate fingers and the gate length is 0.15  $\mu$ m, which is not given from the layout view, but is a process dependent parameter.

Figure 1.3: A typical FET layout cell. This device is  $8x75 \mu m$ , for a total periphery of  $600 \mu m$ . With a 3.4 W/mm output power density, this device has a potential output power of > 2W. Source: [1]

Shrinking the gate length continues to be the primary method of achieving higher frequency operation in MMICs. The above example transistor would be referred to as a  $8x75 \,\mu\mathrm{m}$  device. By knowing the MMIC fabrication process power density limits and the single device (frequently called the unit cell) periphery, the total theoretical output power of a multi-transistor PA can be determined. Other terms used in this work are defined below:

• SiC substrate - All of the MMICs presented in this thesis are fabricated on silicon carbide (SiC) substrates. The transistor devices are all gallium nitride (GaN), so the processes used to fabricate the circuits are often called GaN-on-SiC. Several different SiC polytypes (crystal

structures that vary in one dimension from each other) are popular, with 4H and 6H being widely used. The use of different polytypes results in slightly different dielectric constants for the substrates, from  $\epsilon_r = 9.7$  to 10. SiC substrates are used for high-power density microwave circuits because they have high thermal conductivities, from 390-490 W/m-K. Commercially available SiC wafers are currently sold in a variety of diameters, from 76 to 150 mm [30].

- HEMT All of the transistor devices in this thesis are metamorphic high electron mobility transistors (HEMTs). The use of GaN HEMTs implies several characteristics that all the MMICs in this work share. First, the devices have a positive drain voltage supply in the range of 4 20 V, depending on the gate length. In general, shorter gate lengths result in higher frequency performance but lower breakdown voltages,  $V_{br}$  or  $V_{breakdown}$ . With the exception of very advanced processes, microwave HEMTs utilize a depletion mode topology, meaning the gate voltage that controls the flow of electrons or two dimensional electron gas (2DEG) in the device is negative in reference to ground. This means the devices must be biased with a negative gate voltage (pinched-off) before applying the drain supply voltage.

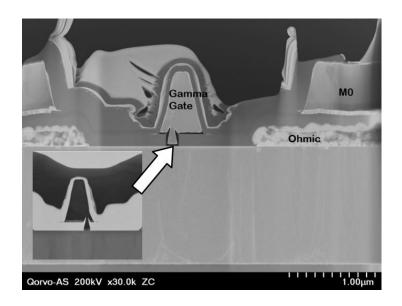

- T-gate and Γ-gate These structures are important breakthroughs in device technology that allow GaN HEMTs to operate at high frequencies and/or with high output power. The T-gate from the process used in chapter 4 is shown in Fig. 1.4. The Γ-gate from the process used in chapter 3 is shown in Fig. 1.5. The Γ-gate is a modified T-gate that reduces the gate parasitics to allow for higher frequency operation and output power.

Figure 1.4: A SEM photograph of the gamma-gate used in Chapter 3. The transistors in this process exhibit  $f_T > 72 \,\text{GHz}$ . Photograph: Qorvo

Figure 1.5: A SEM photograph of the T-gate used in Chapter 4. The transistors in this process exhibit  $f_T > 300\,\mathrm{GHz}$ . Photograph: HRL Laboratories

The modeling of microwave transistors is an entire research topic on its own with associated theory and measurement techniques. Active and passive device simulation in a MMIC design are two very different things. The predicted behavior of passive elements is generally accurate for MMIC designs because the entire network is eventually fully EM simulated, typically with a method-of-moments (MoM) technique. The predicted behavior of the transistor however is not simulated with a MoM technique, it is derived from S-parameters (small-signal behavior) or large-signal models that are capable of predicting the nonlinear relationship between input and output voltages and currents. It is useful, however, to know what models are commonly used in the design of MMICs, how those models are created and what can go wrong in the simulations using those models. The most important idea to keep in mind is that trusting a model to predict behavior outside of its validated operation range is very risky. Depending on the mode of operation of a PA, the fabricated device could oscillate, have greatly reduced power or efficiency or simply do nothing at all. For the designs in this work, Angelov or EEHEMT models were used.

The Angelov/Chalmers model exists in many forms and was published by Angelov in [31]. Several versions of it are named after individuals who contributed important improvements to the model such as Zirath, Rorsman and Angelov [32]. Because the work on the various forms of the model was performed at Chalmers University of Technology in Gothenburg, Sweden, the model is also called the Chalmers model. The model is known for being especially good at predicting the behavior of HEMTs, which at this point in time are the main device used in GaN MMICs. The current Angelov model has improved capacitance, breakdown, and noise modeling. It has a single-pole thermal circuit approximation to account for heating effects. The Chalmers/Angelov model is known to be particularly well suited for the modeling of GaN FETs.

The EEHMET model was developed by EEsof before being acquired by HP/Agilent/Keysight. The AC and DC behavior of the model is separated for simpler extraction. The temperature and self-heating effects are modeled through equations, not an electro-thermal approximation circuit. More information on this model is given in [33]. Other popular models are the Curtice model, the Root model, the Statz model and the Triquint-own-model (TOM) [13].

#### 1.2 Introduction to Additive Manufacturing

This section describes some of the necessary background knowledge needed to further the understanding of the additive manufactured (AM) components discussed in the thesis. The AM components in this thesis are fabricated in two different ways:

Direct Metal Laser Sintering - is an additive manufacturing process that uses discrete metal particles in movable powder bed and a laser to form structures. The metal particles are deposited in a powder bed and the laser fuses the particles together with heat. A structure is built up layer by layer in the powder bed by an iterative process of fusing the metal particles, lowering the powder bed, and then sweeping a new layer of metal particles across the bed. A summary of the process is shown in Fig. 1.6. The layer thickness depends on the metal particle size and usually varies from 20 to  $200 \,\mu\text{m}$  [34]. To fabricate structures with different surface finishes and feature sizes, the laser power and spot diameter can be varied for the particular component. More details about DMLS are given in chapter 6.

Figure 1.6: The DMLS process. The wire frame represents the design and the solid part is built up from individual layers of discrete metal particles fused together with a laser. Source: [2].

Sterolithography with Metal Coated Plastic - is an additive manufacturing process that uses a liquid, resin based photopolymer in a vat [34]. A UV-laser is used to initialize the photopolymerization process as the laser solidifies the liquid. Similar to DMLS, after the first layer is complete, the part is lowered into the vat and the next layer is fabricated. The layer thickness is determined

by the photopolymer density and in this work was  $25 \,\mu\text{m}$ . The printed plastic part is then treated to allow for metal (Cu) plating. The chemical treatment is a proprietary process of the Swissto12 corporation [35]. Because the components are fabricated with a plastic skeleton, the parts are not as mechanically or thermally robust as solid metal counterparts [36].

#### 1.3 Thesis Overview

The goal of this thesis is to explore non-conventional circuit designs using advanced GaN MMIC technologies, with a focus on increasing operating frequency and output power. To facilitate that goal, several MMIC designs with increasing operating frequency are performed and evaluated. The issues encountered with stability in wideband and very high-frequency designs are addressed with a new stability technique that is compared to established methods. Last, an investigation of packaging and thermal solutions is performed. A summary of the thesis chapters is given below:

- Chapter 2 efficiency enhancement techniques for X-Band GaN MMIC PAs discusses three different techniques for efficiency enhancement, output harmonic injection, a supply modulated Doherty power amplifier, and a Class-E amplifier in a 300 GHz  $f_T$  GaN-on-SiC process.

- Chapter 3 analysis and design of a reverse-channel V-band VCO discusses the design of a V-band VCO in a 90 nm GaN-on-SiC process that uses an integrated (on-chip) microstrip-to-waveguide transition and traditionally machined and AM split block waveguide housings. The active and passive technology, including the advanced 90-nm Γ-gate HEMT is summarized.

- Chapter 4 analysis and design of 235 GHz GaN-on-SiC amplifiers details the design of

power combined multiple stage amplifiers in CPW. Active and passive technology needed

to fabricate circuits at 235 GHz is summarized and measurements are made. A CPW-towaveguide integrated transition is designed to eliminate parasitics from wirebonding and

simplify future module integration.

- Chapter 5 stability analysis in microwave circuits presents a new way of analyzing stability in MMIC and microwave amplifier circuits. This chapter also contains a summary of modern stability analysis techniques and proof of concepts that validate the new technique.

- Chapter 6 millimeter-wave component integration methods contains a summary of results

for W-band waveguide structures manufactured using currently available AM techniques.

This chapter also contains a discussion on energy loss due to surface roughness effects. A

FEM thermal analysis is performed and a AM heat pipe thermal solution is presented and

experimentally validated.

# Chapter 2

#### Efficiency-Enhancement Techniques for X-Band GaN MMIC PAs

#### Contents

| 2.1 | Intro | oduction                                                             | 12 |  |  |

|-----|-------|----------------------------------------------------------------------|----|--|--|

| 2.2 | Outj  | Output Harmonic Injection MMIC PA                                    |    |  |  |

|     | 2.2.1 | Output Harmonic Injection MMIC PA Design                             | 15 |  |  |

|     | 2.2.2 | Measurements and Discussion                                          | 16 |  |  |

| 2.3 | Doh   | erty Power Amplifier MMIC PA with Supply Modulation                  | 22 |  |  |

|     | 2.3.1 | The Doherty PA                                                       | 22 |  |  |

|     | 2.3.2 | X-band Doherty PA Design and Layout                                  | 23 |  |  |

|     | 2.3.3 | Characterization with Supply Modulation                              | 26 |  |  |

| 2.4 | Clas  | s-E MMIC PA                                                          | 29 |  |  |

|     | 2.4.1 | Design and Layout of Class-E and Class-E Cascode MMIC PAs $\ \ldots$ | 33 |  |  |

|     | 2.4.2 | Measurements and Comments                                            | 36 |  |  |

| 2.5 | Cont  | tributions from This Chapter                                         | 38 |  |  |

#### 2.1 Introduction

Modern spectrally-efficient communication signals, such as LTE-Advanced, use multiple subcarriers resulting in high peak-to-average power ratios (PAPR) and large channel bandwidths [37]. Since the number of users, wireless devices and requested data rates will likely continue to grow, new solutions in RF and digital hardware and communication protocols will continue to be researched and developed. The majority of current RF front end research is in investigating how to linearly amplify these spectrally-efficient signals in the low or sub-GHz range for the mobile handset, Internet-connected devices, and base station markets. The necessity of battery operation for handsets and wireless devices and overall efficiency for the base stations drives designers in these markets to maximize PA efficiency. The pressure of balancing the trade-offs between high efficiency, maximum output power, strict linearity, and bandwidth in the 350 billion dollar cellular market has led to new levels of performance utilizing ever more complex amplifier topologies [38], [39]. However, the efficiency enhancement techniques used in the low GHz range can also be applied to X-band amplifiers that are used as phased array unit cells, radar system amplifiers or as main amplifiers in the military and commercial SATCOM markets. This chapter investigates the application of three distinct efficiency-enhancement techniques: output harmonic injection, the Doherty power amplifier topology with supply modulation, and Class-E operation in a high  $f_T$  GaN-on-SiC process, all at X-band frequencies.

#### 2.2 Output Harmonic Injection MMIC PA