### CHARACTERIZATION AND DESIGN OF A LOW-POWER WIRELESS POWER DELIVERY SYSTEM

by

#### EREZ AVIGDOR FALKENSTEIN

B.S., University of Colorado, 2010M.S., University of Colorado, 2010

A thesis submitted to the Faculty of the Graduate School of the University of Colorado in partial fulfillment of the requirements for the degree of Doctor of Philosophy Department of Electrical and Computer Engineering 2011 This thesis entitled:

Characterization and Design of a Low-Power Wireless Power Delivery System written by Erez Avigdor Falkenstein

has been approved for the Department of Electrical and Computer Engineering

Zoya Popović

Dejan S. Filipović

Date \_\_\_\_\_

The final copy of this thesis has been examined by the signatories, and we Find that both the content and the form meet acceptable presentation standards Of scholarly work in the above mentioned discipline. Falkenstein, Erez Avigdor (Ph.D., Electrical Engineering)

Characterization and Design of a Low-Power Wireless Power Delivery System Thesis directed by Professor Zoya Popović

This thesis focuses on a design methodology for low-power non-directional far-field wireless powering. The power receiver consists of one or more antennae which receive plane waves transmitted by the powering source, and deliver the RF power to a rectifying element. The resulting DC power is optimally transferred to the electronic application via a power management circuit. The powering is independent of the electronic application which can include wireless transmission of sensor data.

The design and implementation of an integrated rectifier-antenna at low incident power densities (from 25-200 $\mu$ W/cm<sup>2</sup>) is presented. Nonlinear source-pull measurements and harmonic balance simulations are used for finding the optimal rectifying device RF and DC impedances for efficient rectification. Experimental results show that an antenna design with a specific complex impedance reaches the highest rectification efficiency. Several examples of the design methodology are shown. In specific, characterization of a linearly polarized rectifying patch antenna at frequency of 1.96 GHz is detailed, with an optimal RF impedance of  $137 + j149 \Omega$ and an optimal DC load of  $365\Omega$  resulting in RF to DC conversion efficiency of 63% (simulated) for the rectifier alone and 54% (measured) for the total rectifying antenna. A compact design (eliminating SMA connector) of a dual-polarized rectifier antenna integrated with two rectifiers, one for each polarization is detailed. The complications and issues of combining the powers from the two polarizations are addressed. A analysis of required RF and DC isolation in multiple-rectifier integrated rectifier-antenna is developed and confirmed. Measurement results of a 2.45 GHz integrated rectifier antenna show conversion efficiency of 56% and very small dependance on rotation angle between powering polarization and receiving rectifier antenna (ratio of maximum to minimum power as the antenna is rotated of 1.09).

### $D \, \text{edication}$

This thesis is dedicated to the memory of my inspiring father, Eliezer O. Falkenstein (1938 - 1991).

# Personal Acknowledgments

I am truly grateful to my father for the engineering interest that he cultivated in me. My father, a holocaust survivor, an engineer [1, 2, 3, 4] and a friend of mine ("haver-sheli"), died December 13 th 1991. As a young child, I was encouraged by him to ask questions and be curious. Every mechanical or electrical toy I got form my parents also came with my fathers explanation of the concepts that made it operate. Words cannot convey my gratitude to my mother and sisters for always being supportive. I wish to thank my entire extended family for their support.

I owe my appreciation to the former and current research group members who have made graduate school a great experience: Dr. Jonathan Chisum, Rob Scheeler, Frank Trang, Mike Roberg, Asmita Dani, Jennifer Imperial, Xavier Palomer, Brad Lindseth, Dan Kuester (K pup), Scoot schafer, Dr. Evan Cullens, Dr. Negar Ehsan, Dr. Charles R. Dietlein, Dr. Mike Elsbury, Dr. John Hoversten, Dr. Miloš Janković, Dr. Nicola Kinzie, Dr. Qianli Mu, Dr. Mabel Ramírez, Dr. Néstor López, Dr. Luke Sankey and Dr. Leonardo Ranzani (The nard dog).

To Laura, who deserves applause for her patience dealing with me throughout the last few years of school; thank you for ignoring my faults and encouraging my merits. Last, but not the least, I'd like to thank our dog, Louie, who after long days at school, always greets me with lots of happiness.

# PROFESSIONAL ACKNOWLEDGMENTS

I am profoundly grateful to Professor Zoya Popović. Without her, all of the work in this thesis would of not been possible. She has provided guidance, motivation, opportunity and has developed an amazing research group.

I cannot express my appreciation to Daniel Costinett from the Power Electronics group, who has always been willing to help with any problem, regardless of relevance to his own research or time constraints.

I am very grateful to the countless others how have provided guidance and advice throughout the research leading to this thesis including, professor Regan A. Zane, Dr. Thurein Paing, Dr. Joseph Hagerty and all of the microwave and RF group members for many helpful discussions.

Last, but certainly not the least, I would like to thank my committee, Prof' Zoya Popović, Prof' Edward F. Kuester, Prof' Dejan S. Filipović, Prof' Regan A. Zane, Prof' Richard T. Mihran and Prof' Penina Axelrad, for taking the time to teach me and listen to me.

# $C\,o\,{\rm N\,T\,E\,N\,T\,S}$

| 1        | Intr | roduction                                         | 1  |

|----------|------|---------------------------------------------------|----|

|          | 1.1  | MOTIVATION                                        | 1  |

|          |      | 1.1.1 Introduction                                | 1  |

|          |      | 1.1.2 Background Survey                           | 2  |

|          |      | 1.1.3 Low-Power Non-Directional Wireless Powering | 5  |

|          |      | 1.1.4 Thesis Outline                              | 9  |

| <b>2</b> | Wir  | relessly Powered Sensor Platforms                 | 11 |

|          | 2.1  | Introduction                                      | 12 |

|          | 2.2  | Energy Sources for Wireless Sensors               | 13 |

|          | 2.3  | Approach                                          | 16 |

|          | 2.4  | RF Power Reception                                | 17 |

|          | 2.5  | Power Management                                  | 18 |

|          | 2.6  | Load Management                                   | 22 |

|          | 2.7  | Summary                                           | 25 |

| 3        | Mic  | crowave Rectifier Analysis                        | 26 |

|          | 3.1  | Introduction                                      | 26 |

|          | 3.2  | Time-Domain Analysis                              | 27 |

|          | 3.3  | Harmonic Analysis                                 | 51 |

|          |      | 3.3.1 Amplifier and Rectifier Classes             | 52 |

|          | 3.4               | Summ                                                                            | nary                                                                                                                                                                                                                                                                          | 60                                                                                                                       |

|----------|-------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 4        | Rec               | tifying                                                                         | g Element Simulations and Measurements                                                                                                                                                                                                                                        | 62                                                                                                                       |

|          | 4.1               | Introd                                                                          | luction                                                                                                                                                                                                                                                                       | 63                                                                                                                       |

|          | 4.2               | Rectif                                                                          | ying diode impedance                                                                                                                                                                                                                                                          | 63                                                                                                                       |

|          | 4.3               | Harm                                                                            | onic Balance Simulations                                                                                                                                                                                                                                                      | 70                                                                                                                       |

|          | 4.4               | Comp                                                                            | arison of Harmonic Balance and                                                                                                                                                                                                                                                |                                                                                                                          |

|          |                   | Source                                                                          | e-Pull                                                                                                                                                                                                                                                                        | 72                                                                                                                       |

|          | 4.5               | Harm                                                                            | onic Balance Simulation and Large Signal Scattering Parame-                                                                                                                                                                                                                   |                                                                                                                          |

|          |                   | ters A                                                                          | nalysis                                                                                                                                                                                                                                                                       | 76                                                                                                                       |

|          |                   | 4.5.1                                                                           | Large Signal Scattering Parameters                                                                                                                                                                                                                                            | 76                                                                                                                       |

|          |                   | 4.5.2                                                                           | Simulation Results                                                                                                                                                                                                                                                            | 77                                                                                                                       |

|          | 4.6               | Summ                                                                            | nary                                                                                                                                                                                                                                                                          | . 81                                                                                                                     |

| -        | <b>A</b>          |                                                                                 |                                                                                                                                                                                                                                                                               |                                                                                                                          |

| <b>5</b> | Ant               | cenna a                                                                         | and Rectifier; design, integration and Measurement                                                                                                                                                                                                                            | 82                                                                                                                       |

| 5        | <b>Ant</b><br>5.1 |                                                                                 | and Rectifier; design, integration and Measurement<br>ana Design For Integration With Rectifiers                                                                                                                                                                              | <b>82</b><br>83                                                                                                          |

| 5        |                   |                                                                                 |                                                                                                                                                                                                                                                                               |                                                                                                                          |

| 5        |                   | Anten                                                                           | ana Design For Integration With Rectifiers                                                                                                                                                                                                                                    | 83                                                                                                                       |

| 5        |                   | Anten<br>5.1.1<br>5.1.2                                                         | ana Design For Integration With Rectifiers                                                                                                                                                                                                                                    | 83<br>84                                                                                                                 |

| 5        | 5.1               | Anten<br>5.1.1<br>5.1.2                                                         | ana Design For Integration With Rectifiers                                                                                                                                                                                                                                    | 83<br>84<br>85                                                                                                           |

| 5        | 5.1               | Anten<br>5.1.1<br>5.1.2<br>Integr                                               | ana Design For Integration With Rectifiers          Antenna Feed Point Design          Antenna, Matching and DC Line Design Validation          ated Rectifier Antenna Characterization                                                                                       | 83<br>84<br>85<br>92                                                                                                     |

| 5        | 5.1               | Anten<br>5.1.1<br>5.1.2<br>Integr<br>5.2.1                                      | ana Design For Integration With Rectifiers                                                                                                                                                                                                                                    | 83<br>84<br>85<br>92<br>93                                                                                               |

| 5        | 5.1               | Anten<br>5.1.1<br>5.1.2<br>Integr<br>5.2.1<br>5.2.2<br>5.2.3                    | ana Design For Integration With Rectifiers                                                                                                                                                                                                                                    | 83<br>84<br>85<br>92<br>93<br>96                                                                                         |

| 5        | 5.1<br>5.2        | Anten<br>5.1.1<br>5.1.2<br>Integr<br>5.2.1<br>5.2.2<br>5.2.3                    | ana Design For Integration With Rectifiers          Antenna Feed Point Design          Antenna, Matching and DC Line Design Validation          ated Rectifier Antenna Characterization          Measurements and Calibration          Efficiency Definition          Results | <ul> <li>83</li> <li>84</li> <li>85</li> <li>92</li> <li>93</li> <li>96</li> <li>98</li> </ul>                           |

| 5        | 5.1<br>5.2        | Anten<br>5.1.1<br>5.1.2<br>Integr<br>5.2.1<br>5.2.2<br>5.2.3<br>Integr          | ana Design For Integration With Rectifiers                                                                                                                                                                                                                                    | <ul> <li>83</li> <li>84</li> <li>85</li> <li>92</li> <li>93</li> <li>96</li> <li>98</li> <li>106</li> </ul>              |

| 5        | 5.1<br>5.2        | Anten<br>5.1.1<br>5.1.2<br>Integr<br>5.2.1<br>5.2.2<br>5.2.3<br>Integr<br>5.3.1 | ana Design For Integration With Rectifiers                                                                                                                                                                                                                                    | <ul> <li>83</li> <li>84</li> <li>85</li> <li>92</li> <li>93</li> <li>96</li> <li>98</li> <li>106</li> <li>106</li> </ul> |

| 6 | Dua | al Pola | rization Integrated Rectifier Antenna                                                                                              | 114   |

|---|-----|---------|------------------------------------------------------------------------------------------------------------------------------------|-------|

|   | 6.1 | Introd  | uction                                                                                                                             | 115   |

|   |     | 6.1.1   | Background                                                                                                                         | 116   |

|   |     | 6.1.2   | This work                                                                                                                          | 116   |

|   | 6.2 | Dual I  | Linear Polarization Patch Integrated Rectifier Antenna                                                                             | 118   |

|   |     | 6.2.1   | Single DC Load                                                                                                                     | 122   |

|   |     | 6.2.2   | Split DC Load                                                                                                                      | . 131 |

|   | 6.3 | Summ    | ary                                                                                                                                | . 141 |

| 7 | Sun | nmary   | and Contributions                                                                                                                  | 144   |

|   | 7.1 | Thesis  | summary and outlook                                                                                                                | 144   |

|   | 7.2 | Future  | e Work                                                                                                                             | 147   |

|   |     | 7.2.1   | Rectifier Topologies and Devices                                                                                                   | 147   |

|   |     | 7.2.2   | Antenna and array considerations                                                                                                   | 149   |

|   |     | 7.2.3   | Integration with power management, storage and control $% \left( {{{\left[ {{{\left[ {{\left[ {{\left[ {{\left[ {{\left[ {{\left[$ | . 151 |

|   |     | 7.2.4   | Wireless powering system and transmitter considerations .                                                                          | 155   |

|   |     | 7.2.5   | Propagation environment considerations                                                                                             | 156   |

|   | 7.3 | Thesis  | $s$ contributions $\ldots$                        | 158   |

### Bibliography

# LIST OF TABLES

|       | 1 Overview of integrated rectifier antennas and rectifiers described in     | 1.1 |

|-------|-----------------------------------------------------------------------------|-----|

| 7     | the literature.                                                             |     |

|       | 1 Adaptive transmission test results using 5.8 GHz patch integrated         | 2.1 |

|       | rectifier antenna. Negative $I_{bat}$ indicates net power flow into the     |     |

| 23    | battery.                                                                    |     |

|       | 1 Summary of DC load and diode impedance at the fundamental                 | 3.1 |

| 34    | frequency for the waveforms from Fig. $3.5$                                 |     |

|       | 2 Efficiency simulation rectifier results for sevral input powers. $R_L$ is | 3.2 |

| . 51  | the optimal load                                                            |     |

|       | 1 Summary of measured and simulated rectified power for optimal             | 4.1 |

|       | RF and DC impedance at the diode terminals seen in Fig. $4.12$ and          |     |

| 76    | Fig. <b>4.13</b>                                                            |     |

|       | 1 DC output power from source pull measurement at 1.96 GHz, input           | 5.1 |

|       | power of 10 dBm and DC load of $460\Omega$ for the three matching           |     |

| 93    | conditions of integrated rectifier antennas A1 to A3                        |     |

| 98    | 2 Measured optimal efficiencies for the 3 antennas $\ldots \ldots \ldots$   | 5.2 |

| . 141 | 1 DCAR overview described in the literature                                 | 6.1 |

| 7.1 | Summary of Measured Maximum Rectified Power for Optimal RF |     |

|-----|------------------------------------------------------------|-----|

|     | and DC Impedance at the Diode Terminals                    | 148 |

## LIST OF FIGURES

| 1.1 | Microwave power transmission experiment in space on a small satel-                     |   |

|-----|----------------------------------------------------------------------------------------|---|

|     | lite and on the International Space Station                                            | 2 |

| 1.2 | The rectifying antenna array used in Shinohara's field experiment                      |   |

|     | at a frequency of 2.45 GHz. The size is $3.2\mathrm{m}\times3.6\mathrm{m}.$            | 3 |

| 1.3 | Layout of the 64-element array. Received RF power is rectified at                      |   |

|     | each spiral locally and the combined dc power for all elements is                      |   |

|     | extracted using two dc collection lines at the edges of the array (not                 |   |

|     | shown).                                                                                | 4 |

| 1.4 | $60\mathrm{W}$ light-bulb being lit from $2\mathrm{m}$ away. Note the "obstruction" in |   |

|     | the center. The loop radius is $25\mathrm{cm}$ and the frequency is $9.9\mathrm{MHz}.$ | 6 |

| 1.5 | Block diagram of a wireless powering system. An RF power trans-                        |   |

|     | mitter transmits a plane wave incident on a rectenna element or                        |   |

|     | array (RF power receiver). Following rectification is a DC stage with                  |   |

|     | power management. In this paper, we consider a narrowband low                          |   |

|     | power non directional power transmitter. The electronic application                    |   |

|     | for this study is a wireless sensor platform. The power density at                     |   |

|     | the receiver is between 25 to $200 \mu W/cm^2$ .                                       | 7 |

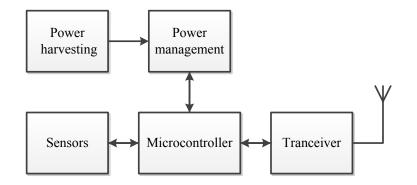

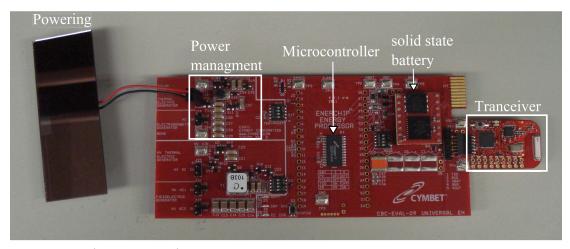

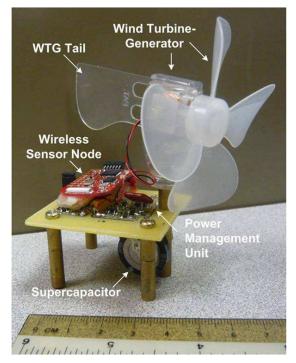

- 2.1 Basic sensor platform block diagram. The power harvesting could be one of many sources (solar, electromagnetic, wind, etc). The power management is responsible for maintaining the correct voltages to all components of the platform and storing the harvested energy. One or more sensors are connected to the microcontroller and provide measurement data as demanded. The transceiver transmits data packets of the sensed data and can receive control commands from base station. The microcontroller provides all timing and control signals to all of the components of the platform. . . . . . . . . .

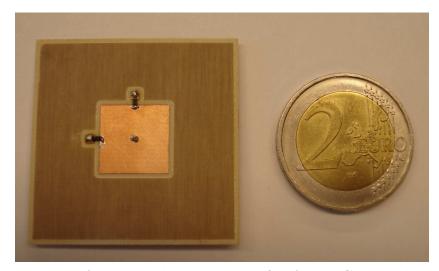

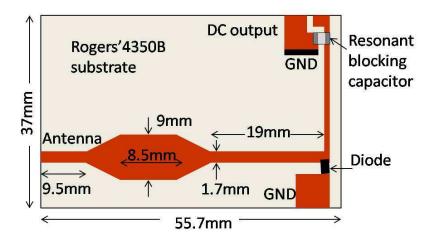

| 2.5 | $5$ $$ Photo of integrated antenna rectifier for $5.8{\rm GHz}$ dual polarization |      |

|-----|-----------------------------------------------------------------------------------|------|

|     | reception and rectification. The antenna is fabricated on a Rogers                |      |

|     | 4350b substrate, and the diodes are soldered to the high-impedance                |      |

|     | points. The two DC connections are taken from the diode terminals                 |      |

|     | and through an isolated via in the voltage null of the patch, which               |      |

|     | is 1.3cm squared in size.                                                         | 18   |

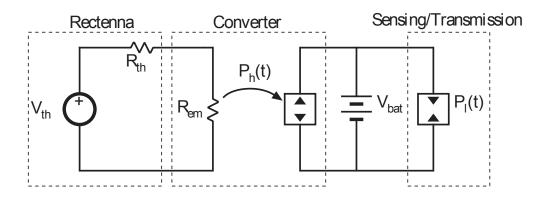

| 2.6 | Averaged model of the converter, integrated antenna rectifier, and                |      |

|     | load                                                                              | 19   |

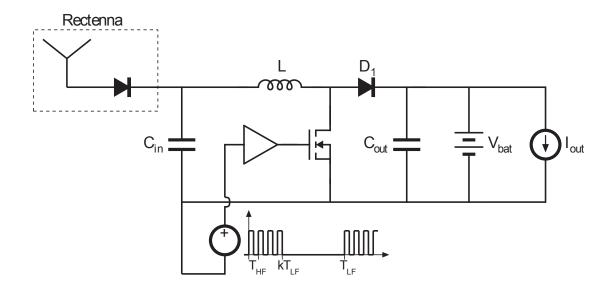

| 2.7 | Circuit diagram of the converter portion of the power management                  |      |

|     | module. $I_{out}$ represents the load on the battery presented by the             |      |

|     | control, sensing, and transmission circuitry                                      | 20   |

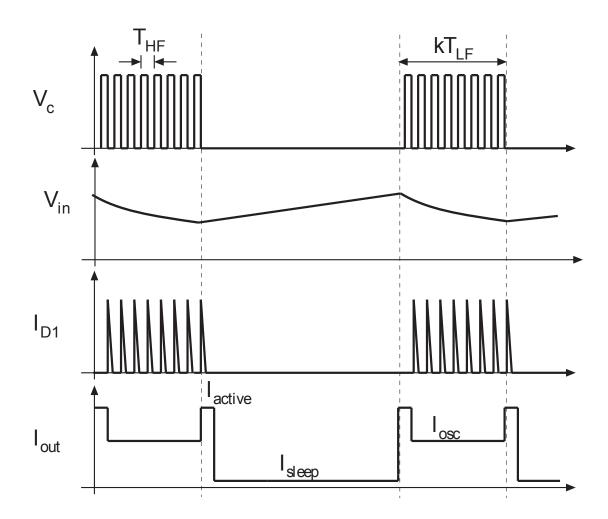

| 2.8 | MOSFET switching waveform Vc, Converter input voltage $V_{in}$ (with              |      |

|     | exaggerated ripple), diode current $I_{D1}$ , and battery load current $I_{ctl}$  |      |

|     | caused by the generation the gate drive signals. $\ldots$ $\ldots$ $\ldots$       | . 21 |

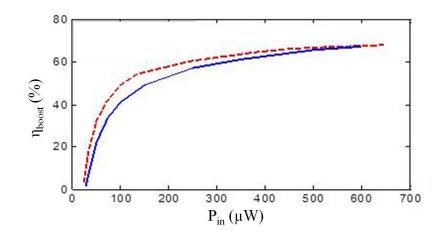

| 2.9 | Measured and predicted efficiency of circuit as a function of available           |      |

|     | input DC power.                                                                   | 22   |

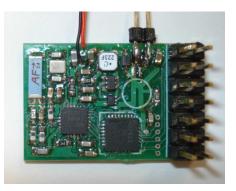

| 2.1 | 0 The 2.1x1.7 cm circuit contains both power management and sen-                  |      |

|     | sor/transmitter circuitry                                                         | 24   |

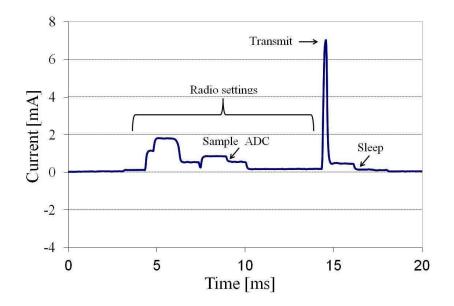

| 2.1 | 1 Measured total current consumption of the circuit described in                  |      |

|     | Fig. 2.4 and shown in Fig. 2.10. $\ldots$                                         | 24   |

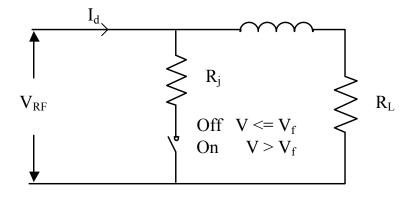

| 3.1 | Circuit model of an ideal diode with constant forward bias voltage                |      |

|     | connected to an RF choke and a DC load. $R_j$ is a small on resistance,           |      |

|     | in the ideal case it is a perfect short, in a more realistic model it is          |      |

|     | a few $\Omega$ to a few tens of $\Omega$                                          | 29   |

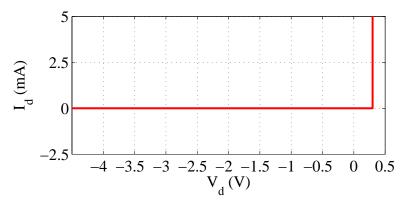

| 3.2 | 2 I-V curve for an ideal diode with constant forward bias voltage                 |      |

|     | $(R_j = 0\Omega)$                                                                 | 29   |

| 3.3  | I-V curve for an ideal switch diode model with constant resistance                    |    |

|------|---------------------------------------------------------------------------------------|----|

|      | $R_j = 50\Omega$                                                                      | 30 |

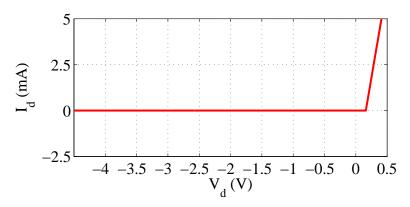

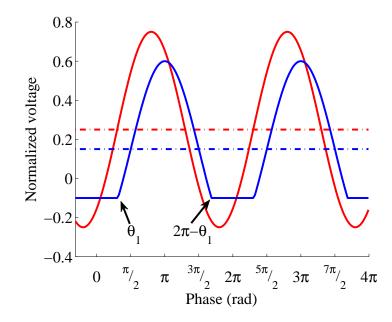

| 3.4  | Generator Voltage waveform (red) and the resulting voltage wave-                      |    |

|      | form across the diode $V_d$ from Fig. 3.1 (blue) following the IV curve               |    |

|      | in . $3.2$ . The points of transition from forward bias to reverse and                |    |

|      | vice verse are labeled $(\theta_1)$ and $(2\pi - \theta_1)$ . Notice that the forward |    |

|      | bias voltage is a non zero value                                                      | 30 |

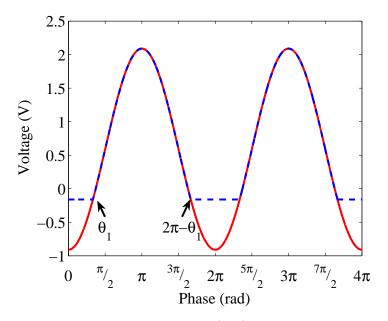

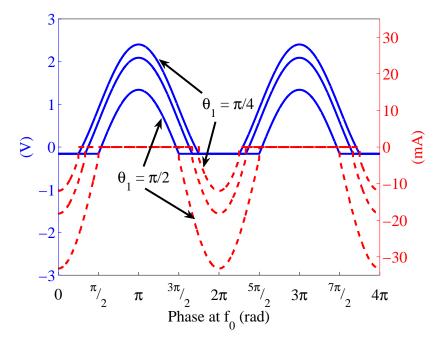

| 3.5  | Diode voltage $V_d$ (blue) and current through the diode $I_d$ (dashed                |    |

|      | red), for conduction angle $\theta_1 = \pi/2$ , $\pi/3$ and $\pi/4$                   | 33 |

| 3.6  | Dependance of the forward bias period $2\theta_1$ on the DC load resistance           |    |

|      | while keeping the voltage amplitude constant. Notice that reaching                    |    |

|      | very small values of $\theta_1$ is not practical since the DC load climbs to          |    |

|      | values of many $k\Omega$ 's rapidly                                                   | 34 |

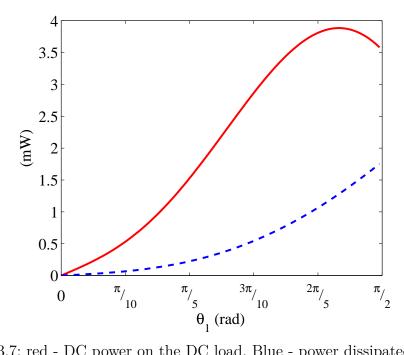

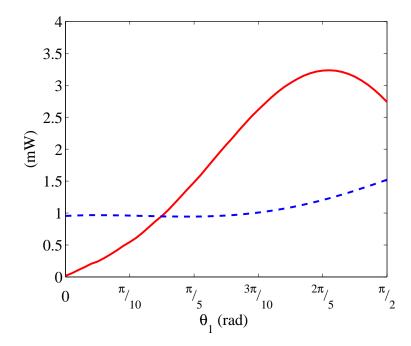

| 3.7  | red - DC power on the DC load, Blue - power dissipated in the                         |    |

|      | diode. The powers are for a constant input voltage amplitude while                    |    |

|      | sweeping the DC load to adjust the forward bias angle $theta_1$                       | 35 |

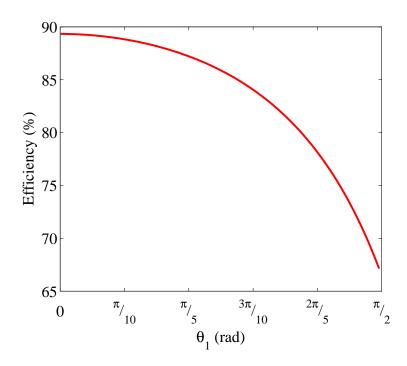

| 3.8  | Rectification efficiency for the circuit in Fig $3.1$ as a function of the            |    |

|      | forward bias period calculated using $(3.14)$                                         | 35 |

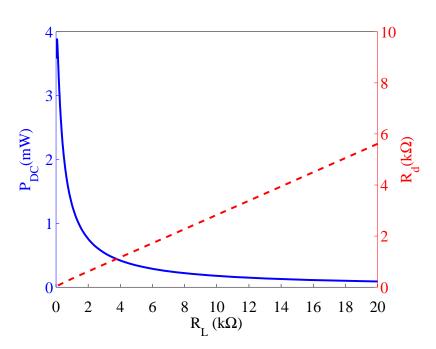

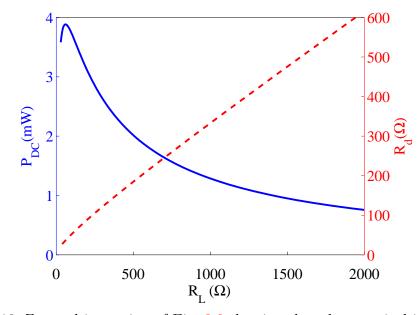

| 3.9  | Output DC power (blue) and diode impedance at the fundamental                         |    |

|      | frequency (red) as a function of the DC load $R_L$                                    | 36 |

| 3.10 | Zoomed in version of Fig. $3.9$ showing that the practical impedances                 |    |

|      | in terms of impedance matching are in the region of high DC power.                    | 37 |

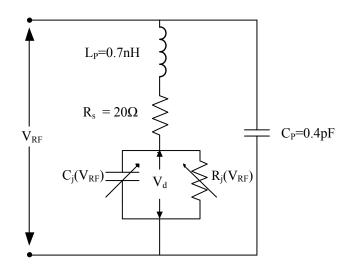

| 3.11 | Detailed circuit model for the Skyworks SMS-7630-79 Schottky diode                    |    |

|      | including package parasitics and nonlinear junction characteristics.                  | 38 |

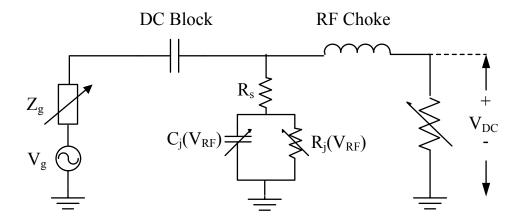

| 3.12 | Circuit schematic using the detailed nonlinear resistance, nonlinear                  |    |

|      | capacitance and series resistor as the rectifying element                             | 38 |

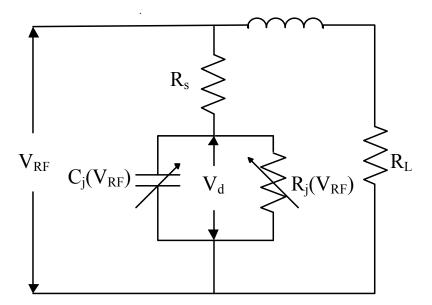

| 3.13 | Simplified diode model. $R_s$ is the series resistance of the diode, $R_j$           |    |

|------|--------------------------------------------------------------------------------------|----|

|      | and $C_j$ are the junction resistance and capacitance as a function of               |    |

|      | $V_d$ . $R_L$ is the DC load connected to the diode through a low-pass               |    |

|      | filter.                                                                              | 39 |

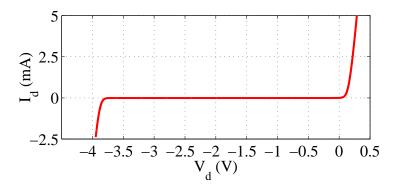

| 3.14 | I-V curve for the SMS-7630-79 diode obtained from simulations                        |    |

|      | using the manufacturer Spice model.                                                  | 39 |

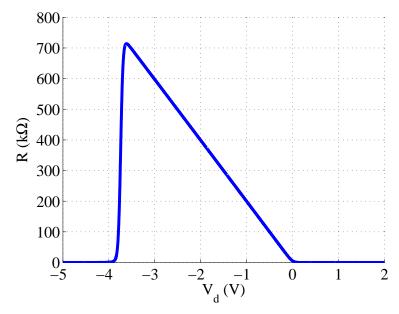

| 3.15 | Diode junction resistance as a function of voltage. The data is                      |    |

|      | extracted in Agilent ADS form SPICE model parameters at DC for                       |    |

|      | the Skyworks SMS-7630-79 Schottky diode                                              | 40 |

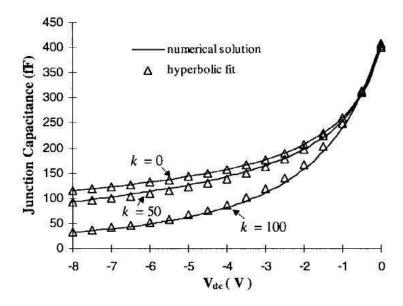

| 3.16 | Junction capacitance versus bias voltage for three Gaussian doping                   |    |

|      | profiles $(k = 0, k = 50, k = 100)$ for Shottky diode with area of                   |    |

|      | $150 \mu \mathrm{m}^2$ used in the analysis by Salameh and Linton                    | 42 |

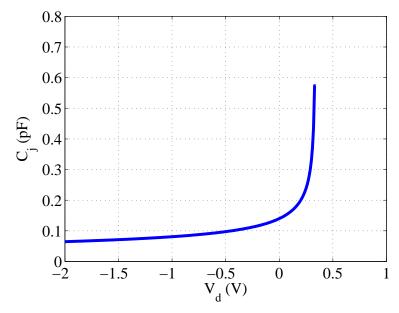

| 3.17 | SMS-7630-79 Schottky diode junction capacitance as a function                        |    |

|      | of voltage using $(3.22)$ . This is a simplified approximation to the                |    |

|      | junction capacitance not including the diffusion capacitance effect.                 | 43 |

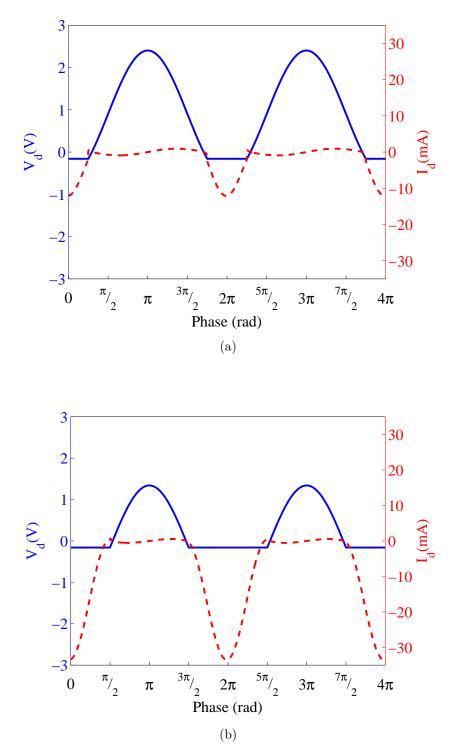

| 3.18 | diode voltage $V_d$ (blue) and current through the diode $I_d$ (red)                 |    |

|      | for different values of $(\theta_1)$ , $\pi/4$ (a) and $\pi/2$ (b) for a diode model |    |

|      | including junction capacitance $(3.22)$                                              | 44 |

| 3.19 | red - DC power on the DC load, Blue - power dissipated in the                        |    |

|      | diode. The powers are for a constant input voltage amplitude while                   |    |

|      | sweeping the DC load to adjust the forward bias angle $\theta_1$ . In contrast       |    |

|      | to Fig. $3.7$ the model used to evaluate the powers pesented in the                  |    |

|      | plot include the effects of the paracitic nonlinear junction capacitance.            | 45 |

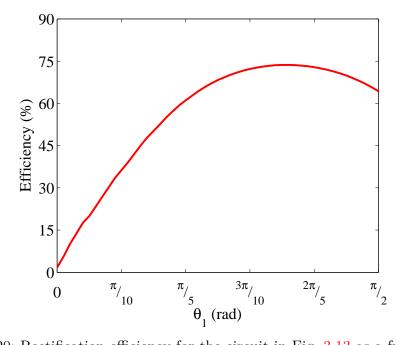

| 3.20 | Rectification efficiency for the circuit in Fig. $3.13$ as a function of             |    |

|      | the forward bias period calculated using $3.14.$                                     | 46 |

3.21 Example voltage waveforms: input voltage V across diode (red) and voltage  $V_d$  across nonlinear portion of the diode model (blue). The dashed red line shows the DC components of the input waveform and the blue is the DC component of the voltage across the nonlinear portion of the diode while it is reverse biased. . . . . . . . . . .

47

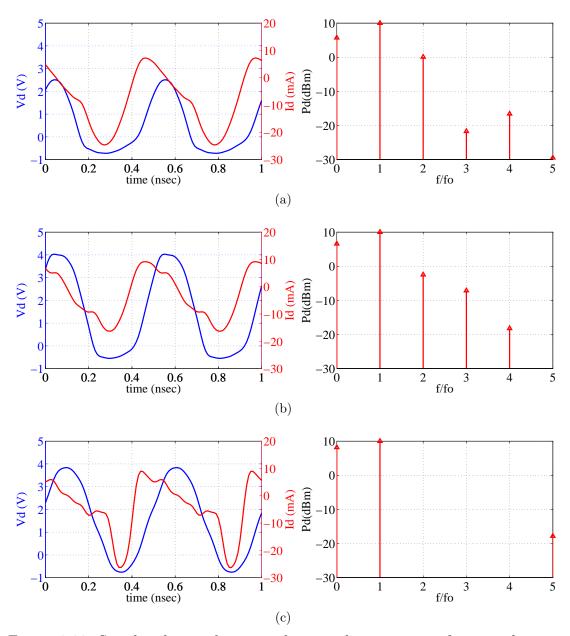

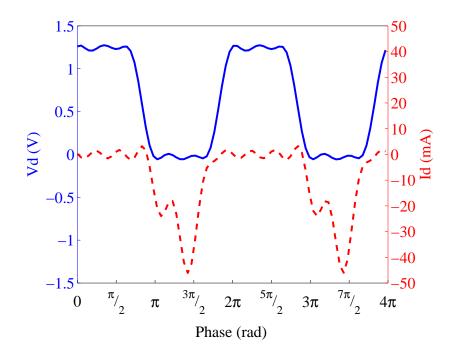

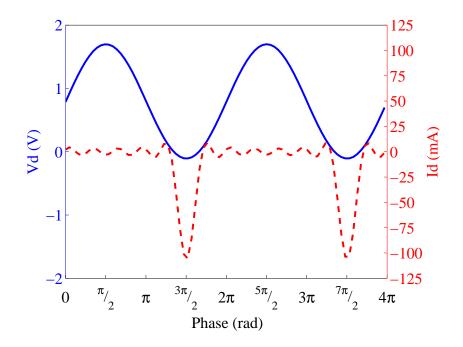

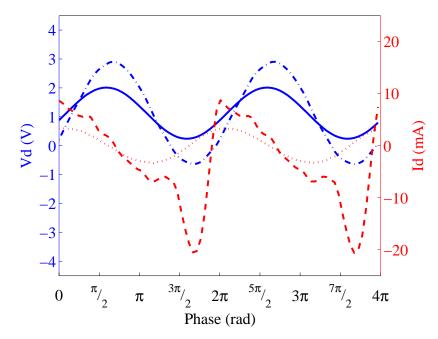

- 3.23 Voltage (blue) and current (dashed red) time-domain waveforms corresponding to class-F harmonic terminations. Obtained from harmonic balance simulations in Agilent ADS using an ideal switch with  $R_{on}=1 \Omega$  and  $R_{off}=5 M\Omega$  with the switch transition at  $V_d=0$ and a DC load of 190 $\Omega$ . The harmonic conditions are created using six  $\lambda/4$  stubs for harmonic terminations, shorts at even harmonics and opens at odd harmonics.

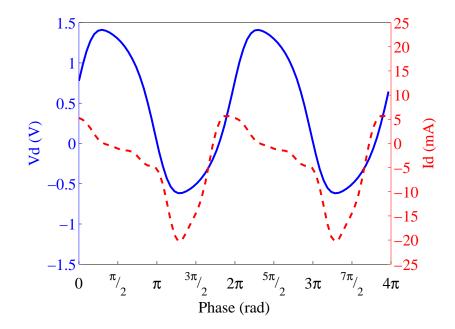

- 3.24 Voltage (blue) and current (dashed red) time-domain waveforms, obtained from harmonic balance simulation in ADS using a Skyworks schottky diode Spice model. The input power is 10 dBm at a frequency of 2.45 GHz. The harmonic conditions where created using six harmonic terminations, with the same stubs used in the previous class-F simulation with the ideal switch.

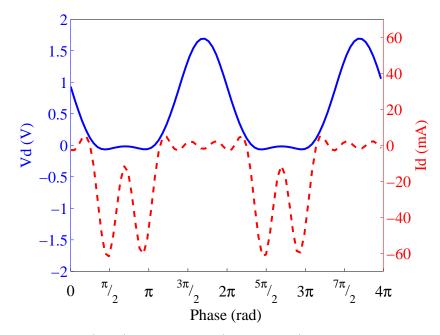

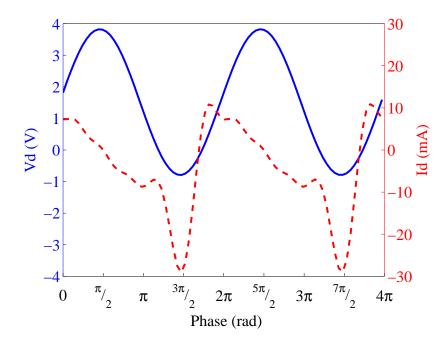

- 3.25 Voltage (blue) and current (dashed red) time-domain waveforms corresponding to class- $F^{-1}$  harmonic terminations. Obtained from harmonic balance simulations in Agilent ADS using an ideal switch with  $R_{on}=1 \Omega$  and  $R_{off}=5 M\Omega$  with the switch transition at  $V_d=0$ and a DC load of 190 $\Omega$ . The harmonic conditions are created using six  $\lambda/4$  stubs for harmonic terminations, shorts at odd harmonics and opens at even harmonics.

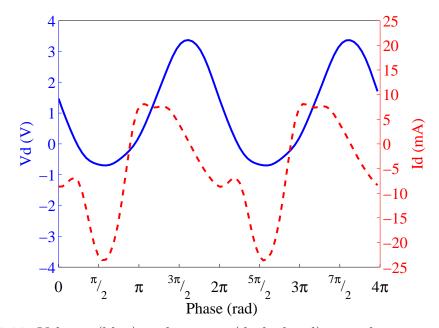

- 3.26 Voltage (blue) and current (dashed red) time-domain waveforms, obtained from harmonic balance simulation in ADS using a Skyworks schottky diode Spice model. The input power is 10 dBm at a frequency of 2.45 GHz. The harmonic conditions where created using six harmonic terminations, with the same stubs used in the previous class- $F^{-1}$  simulation with the ideal switch. . . . . . .

57

58

- 3.27 Voltage (blue) and current (dashed red) time-domain waveforms corresponding to class-C harmonic terminations. Obtained from harmonic balance simulations in Agilent ADS using an ideal switch with  $R_{on}=1 \Omega$  and  $R_{off}=5 \text{ M}\Omega$  with the switch transition at  $V_d=0$ and a DC load of 190 $\Omega$ . The harmonic conditions are created using six  $\lambda/4$  stubs for harmonic terminations, shorting the harmonics.

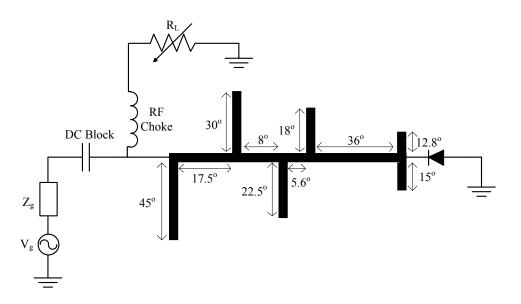

- 3.28 Microstrip circuit example of a harmonic terminated class C rectifier. The terminated harmonics are 2nd to 7th. Each stub is a  $\lambda/4$  length at its harmonic frequency. The design is done using the diode plane as the reference plane. Starting with the higher harmonic stubs at the reference plane and adding the lower harmonic stubs at a distance that transforms there impedance to a short at the diode plane. All lengths in the figure are in electrical degrees at the fundamental frequency. The fundamental is assumed to be matched. . . . . .

- xix

| 3.29 | Voltage (blue) and current (dashed red) time-domain waveforms,                       |    |

|------|--------------------------------------------------------------------------------------|----|

|      | obtained from harmonic balance simulation in ADS using a Sky-                        |    |

|      | works schottky diode Spice model. The input power is $10\mathrm{dBm}$ at             |    |

|      | a frequency of $2.45\mathrm{GHz}$ . The harmonic conditions where created            |    |

|      | using six harmonic terminations, with the same stubs used in the                     |    |

|      | previous class-C simulation with the ideal switch. $\ldots$ . $\ldots$ .             | 60 |

| 4.1  | Block diagram of the source-pull RF-DC measurement. The rectified                    |    |

|      | voltage is measured across a DC load resistor while the RF power to                  |    |

|      | the diode (DUT) and the impedance presented at the diode input                       |    |

|      | are varied                                                                           | 65 |

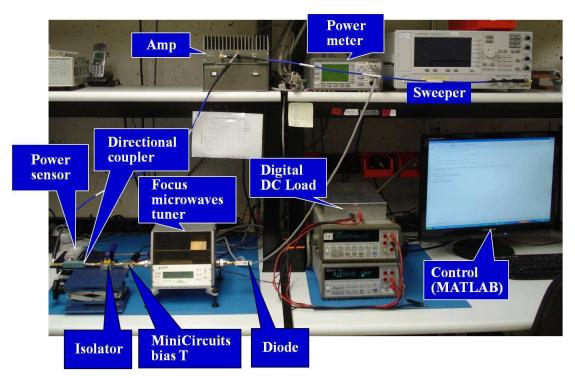

| 4.2  | Photograph of the source-pull RF-DC measurement. The rectified                       |    |

|      | voltage is measured across a variable DC load resistor while the                     |    |

|      | RF power to the diode (DUT) and the impedance presented at the                       |    |

|      | diode input are varied. This is repeated for several values of the DC                |    |

|      | load resistor                                                                        | 66 |

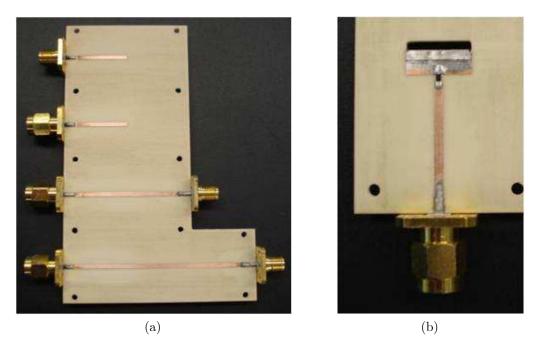

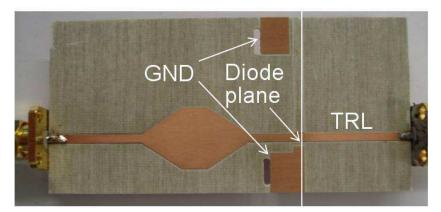

| 4.3  | (a) TRL calibration and (b) test circuit used in the source-pull.                    |    |

|      | The test circuit is narrowband and designed to move the impedance                    |    |

|      | of the diode towards the middle of the Smith chart at the design                     |    |

|      | frequency.                                                                           | 67 |

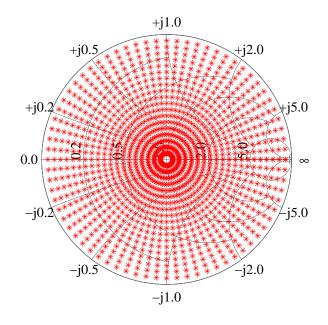

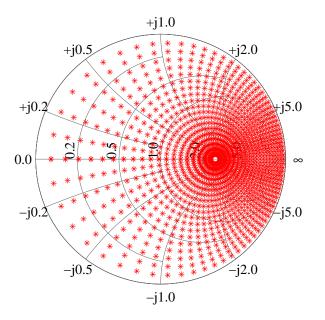

| 4.4  | Distribution of source-pull measurement points in a 50 – $\Omega$ environ-           |    |

|      | ment $(Z_0 = 50 \Omega)$                                                             | 67 |

| 4.5  | Distribution of source-pull measurement points in a 50 – $\Omega$ environ-           |    |

|      | ment $(Z_0 = 50\Omega)$ transformed by a $\lambda/4$ long $80 - \Omega$ line         | 68 |

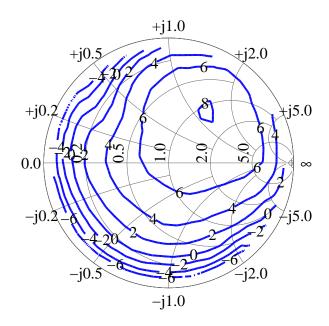

| 4.6  | Measured rectified power contours for $10\mathrm{dBm}$ input power. Optimal          |    |

|      | load $R_L = 460 \Omega$ at 1.96 GHz. The Smith chart is normalized to $120 \Omega$ . | 68 |

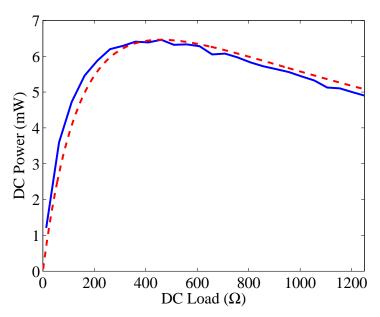

| 4.7  | Measured DC power for $10\mathrm{dBm}$ incident power at $1.96\mathrm{GHz}$ for op-        |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | timal RF impedance for each load (blue). Load sweep of a Thevenin                          |    |

|      | equivalent voltage source and resistor (red). The Thevenin values                          |    |

|      | were calculated using the data from the maximum output power                               |    |

|      | point on the measured curve.                                                               | 69 |

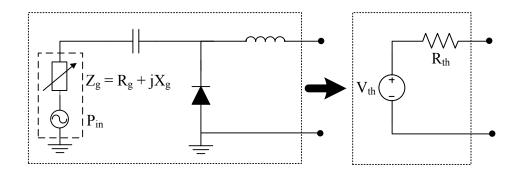

| 4.8  | Schematic circuit description of the Thevenin equivalent of the                            |    |

|      | rectifier circuit.                                                                         | 70 |

| 4.9  | Block diagram of Agilent ADS harmonic balance simulations corre-                           |    |

|      | sponding to the source-pull measurement of Fig. 4.1. Notice that in                        |    |

|      | this case, the DC load is in a transformed RF impedance environ-                           |    |

|      | ment, not 50 $\Omega$ environment as in Fig. 4.1. The location of the DC                   |    |

|      | load connection in not important, as long as the RF impedance it                           |    |

|      | presents is an open, the the RF impedance presented to the diode                           |    |

|      | is unchanged.                                                                              | 71 |

| 4.10 | Simulated constant rectified power contours at 2 dB increments                             |    |

|      | at 1.96 GHz for a 460 $\Omega$ DC load resistance. The results are for a                   |    |

|      | $10\mathrm{dBm}$ input power for a single Skyworks SMS7630-79 Schottky                     |    |

|      | diode connected to an $80\Omega$ input line. The maximal rectified power is                |    |

|      | $7.7\mathrm{dBm}.$ In this case, the RF-to-DC conversion efficiency is $58\%.\mathrm{The}$ |    |

|      | Smith chart is normalized to $120 \Omega$ .                                                | 72 |

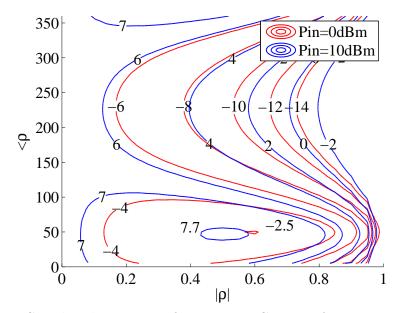

| 4.11 | Simulated contours of constant DC power for a range of magni-                              |    |

|      | tude and phase mismatch between diode impedance and reference                              |    |

|      | impedance, for two values of input power (red and blue traces).                            |    |

|      | The plot shows that the same rectified power can be obtained for                           |    |

|      | multiple values of diode impedance mismatch relative to a $120\Omega$                      |    |

|      | characteristic impedance                                                                   | 73 |

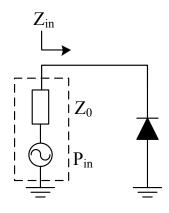

- 4.14 circuit used to simulate input impedance of the diode as a function of input power at 2.45 GHz. The harmonic balance technique using 25 harmonics is used to find the voltages and currents at every node. 78

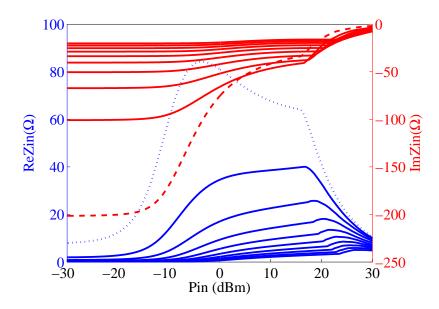

- 4.15 Simulated input impedance of the diode as a function of input power at 2.45 GHz. Blue real part of the diode impedance, dotted fundamental , solid harmonics. Blue imaginary part of the diode impedance, dashed fundamental , solid harmonics. Based on measurements, we trust the model on to 10 dBm.

79

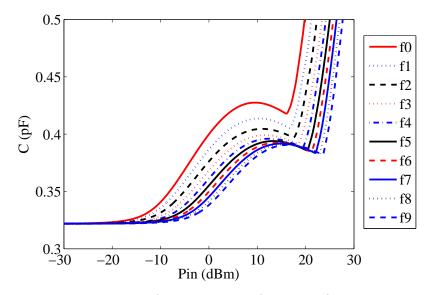

- 4.16 Input capacitance of the diode as a function of input power at2.45 GHz and the first nine harmonics. For each curve the circuit isexited by one frequency at a time over the range of powers. . . . . 79

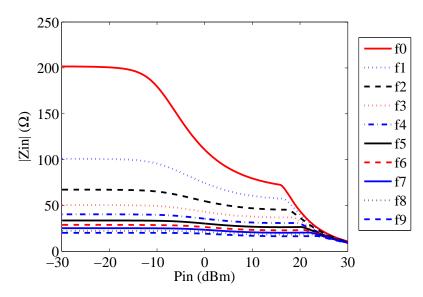

- 4.17 Magnitude of the input impedance of the diode as a function of input power at  $f_0 = 2.45$  GHz and the first ten harmonics. . . . . 80

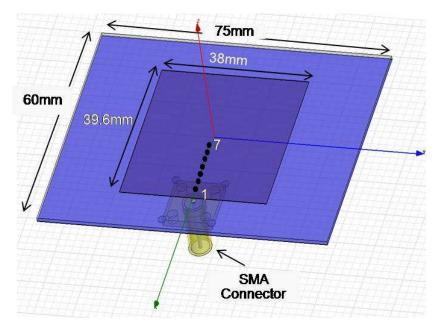

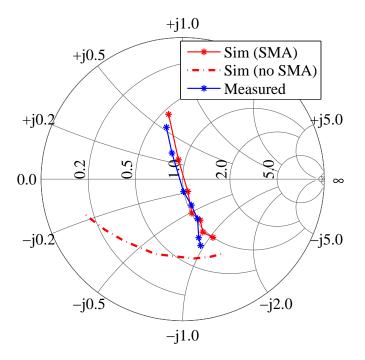

- 5.1 Geometry of patch antenna with 3D detailed SMA connector implemented in Ansoft HFSS. The antenna was simulated with 7 different feed point locations. For validation, the same geometry was fabricated. The feed points are located along the center axis that is parallel to the non-radiating edge of the antenna. Feed number 1 is at the radiating edge feed number 7 is 6 mm away from the center, the rest of the feed locations are evenly spaced between them.

- 5.2 Simulated and measured results of the antenna complex impedance. The dashed line shows the simulation without the full SMA connector implemented in HFSS. The Smith chart is normalized to  $120 \Omega$ .

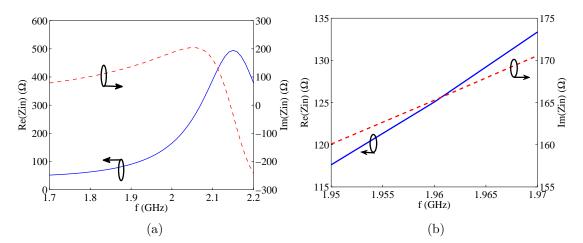

- 5.5 Real and imaginary parts of the input impedance at the diode plane(a) a close up of the same impedance data in the band of interest (b). 88

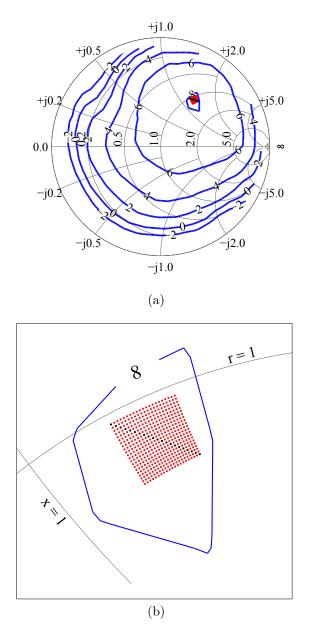

- 5.6 (a) Measured source pull contours at 1.96 GHz in blue for Skyworks SMS-7630-79 Schottky diode at an input power of 10 dBm. The black symbols are the complex impedances combinations from 1.7 GHz to 2.2 GHz shown in Fig. 5.5b and the Red are all possible combinations of each point of the real part of the impedance with each of the imaginary parts within that band. (b) a close up of the maximum DC power contour with the impedance combinations. The Smith chart is normalized to  $120 \Omega$ .

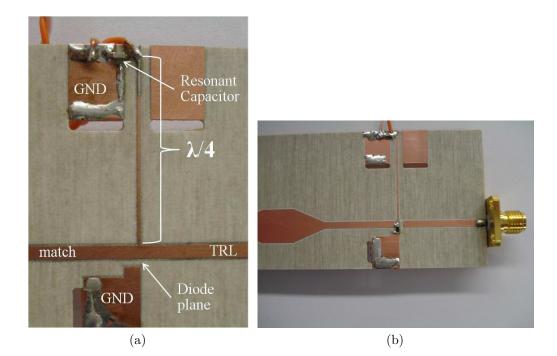

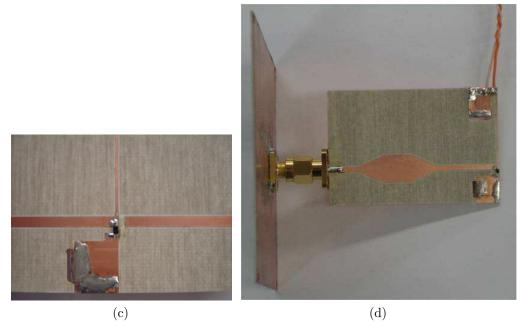

- 5.7 Photographs of the validation circuits for the antenna, matching,

DC collection circuit and full integrated rectifier antenna. (a) DC

collection circuit added to matching circuit. (b) TRL trace cut at

the reference plane for measuring the impedance presented to the

diode. (c) Closeup of the cut TRL line and the diode soldered in

place. (d) The full integrated rectifier antenna after trimming the

excess substrate from the validation portion of the circuit. . . . . 91

- 5.8 Layout of the matching circuit used to transform the antenna complex impedance to the optimal diode complex impedance. . . . . . 92

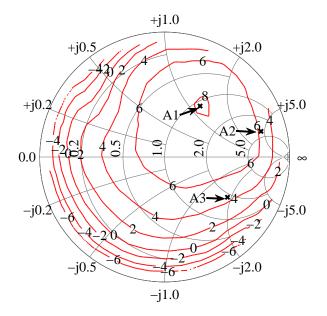

- 5.9 Measured diode load-pull contours for rectified DC power with superimposed impedances that antennas A1-A3 are matched to (black symbols). This data is for the optimal DC load for antenna A1, and sub-optimal load for A2 and A3. The Smith chart is normalized to 120 Ω.

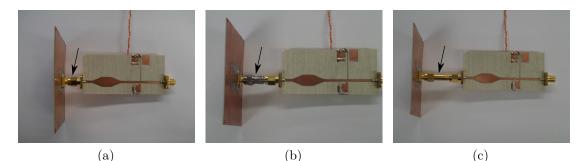

| 5.1 | 0 Photographs of the integrated rectifier antenna with three different                |     |

|-----|---------------------------------------------------------------------------------------|-----|

|     | matches. (a) integrated rectifier antenna A1, the diode is presented                  |     |

|     | with the optimal fundamental frequency impedance. (b) By adding                       |     |

|     | a line section between the antenna and matching circuit the diode                     |     |

|     | is presented with a sub-optimal impedance, A2 and (c) a longer                        |     |

|     | adaptors between the antenna and rectifying circuit moves the                         |     |

|     | impedance farther away from the optimal, A3                                           | 94  |

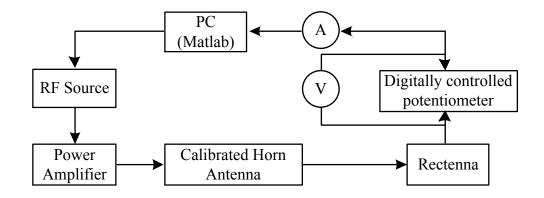

| 5.1 | 1 Block diagram of measurement setup for obtaining calibrated recti-                  |     |

|     | fied power levels and efficiencies over a range of normally incident                  |     |

|     | power densities and DC loads                                                          | 94  |

| 5.1 | 2 Photographs of the calibrated AEL H-1498 broadband horn $G(1.96GHz)$                | ) = |

|     | 3.7 dBi antenna mounted on wooden mount (a). the mount is                             |     |

|     | equipped with two step motors allowing rotation of the antenna                        |     |

|     | under test in to axis. After alignment, the mount and measuring                       |     |

|     | equipment are covered with RF absorber material (b), and the                          |     |

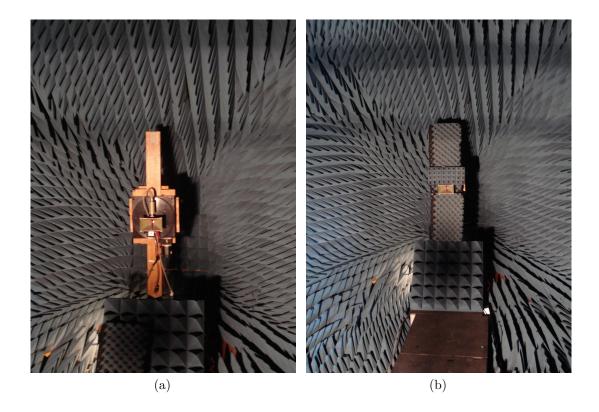

|     | antenna is ready for RF measurements                                                  | 95  |

| 5.1 | 3 Measured efficiency using $(5.3)$ -Blue, $(5.5)$ -Red and $(5.4)$ -Black. The       |     |

|     | RF power $in(5.5)$ is found by multiplying the power density by the                   |     |

|     | effective area of the antenna obtained from HFSS simulations with                     |     |

|     | a fixed 50 $\Omega$ port impedance. The input power in (5.4) is obtained              |     |

|     | from measured power from a reference patch antenna with same                          |     |

|     | geometry as the integrated rectifier antenna but matched to $50\Omega$                |     |

|     | and connected to a power meter. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 97  |

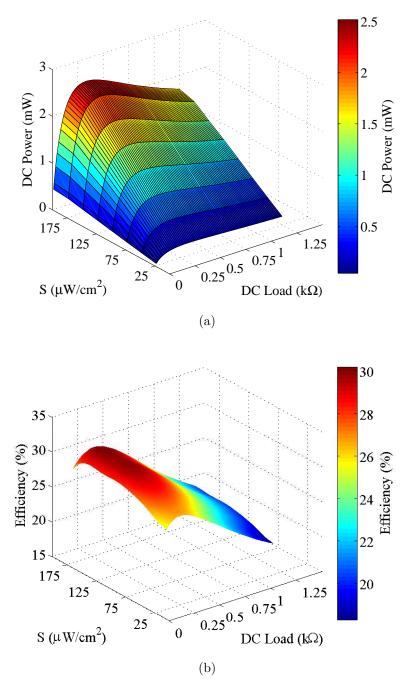

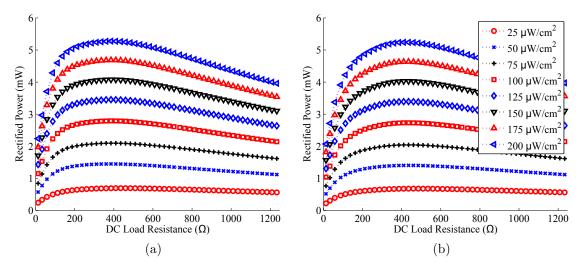

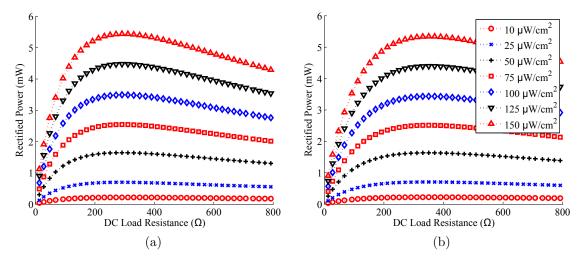

| 5.1 | 4 (a) Measured co-polarized rectified power for Antenna A1 at broad-                  |     |

|     | side for power densities 25 to $200\mu\mathrm{W/cm^2}.$ Every intersection of         |     |

|     | the black grid lines and black curves is a measured data point.(b)                    |     |

|     | RF to DC conversion efficiency calculated from measured data in (a).                  | 99  |

|                     | 5.15 (a) (a) Measured co-polarized rectified power for Antenna A2 at            |

|---------------------|---------------------------------------------------------------------------------|

|                     | broadside for power densities 25 to $200\mu\mathrm{W/cm^2}.$ Every intersection |

| 1                   | of the black grid lines and black curves is a measured data point.(b)           |

| ı) <mark>101</mark> | RF to DC conversion efficiency calculated from measured data in (a              |

5.16 (a) Measured co-polarized rectified power for Antenna A3 at broadside for power densities 25 to  $200 \,\mu W/cm^2$ . Every intersection of the black grid lines and black curves is a measured data point.(b) RF to DC conversion efficiency calculated from measured data in (a).102

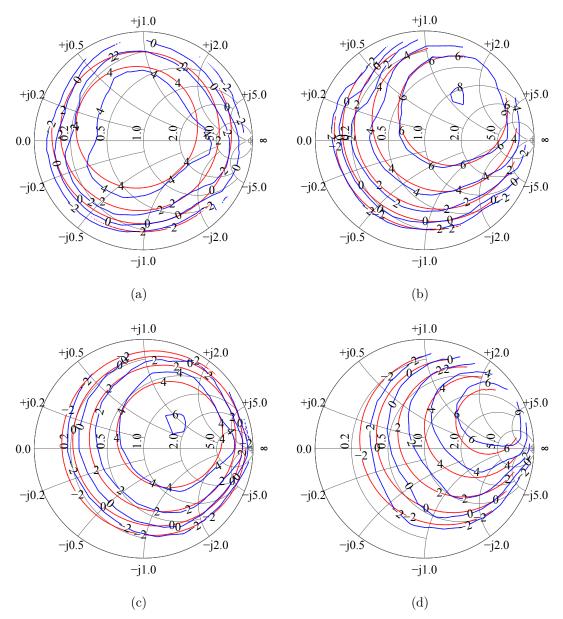

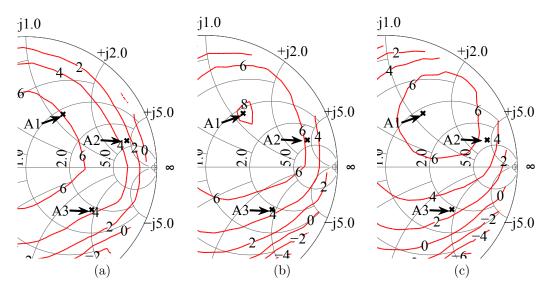

|     | 5.17 Source pull constant DC contours overlayed with the impedance of         |  |  |  |

|-----|-------------------------------------------------------------------------------|--|--|--|

|     | each of the test antennas A1 to A3 (a) A low DC load of $112\Omega.({\rm b})$ |  |  |  |

|     | Optimal DC load of 460 $\Omega.$ (c) High DC load of 1200 $\Omega.$ The Smith |  |  |  |

| 103 | chart is normalized to $120 \Omega$                                           |  |  |  |

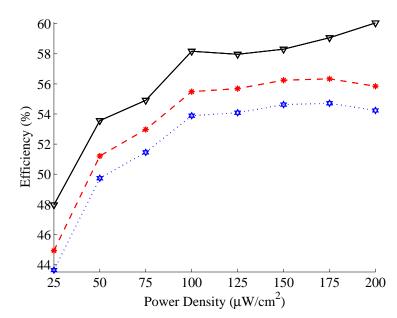

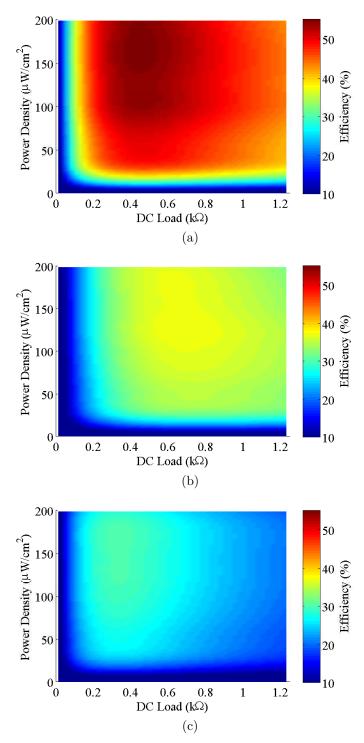

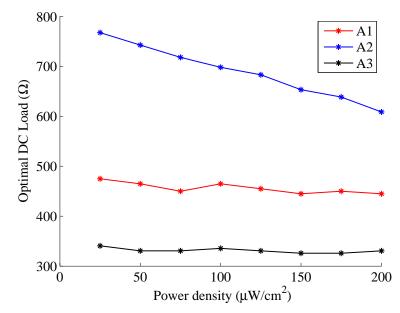

5.19 Measured efficiencies for the three test integrated rectifier antennas (A1 to A3) plotted on the same efficiency scale for power densities 25 to  $200 \,\mu W/cm^2$  at broadside. (a) Antenna A1 (b) Antenna A2 and (c) Antenna A3.

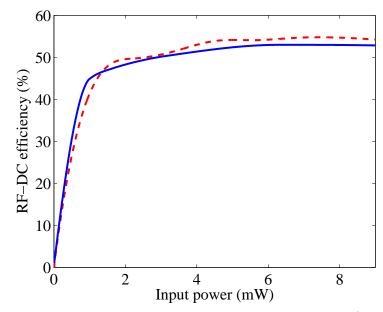

- 5.21 Measured integrated rectifier antenna efficiency (dashed red). ADS diode rectifier simulation efficiency multiplied by the HFSS simulated antenna radiation efficiency (blue).

108

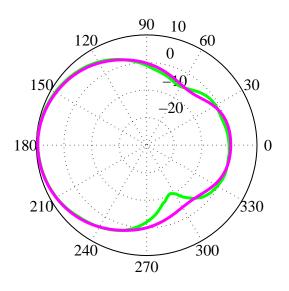

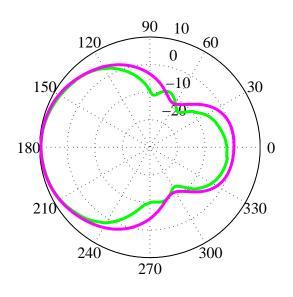

- 5.22 (a) E-plane normalized power pattern (b) H-plane normalized power pattern. For both (a) and (b) the green trace is measured pattern for a 50 $\Omega$  matched patch and the magenta is HFSS simulation. . . 109

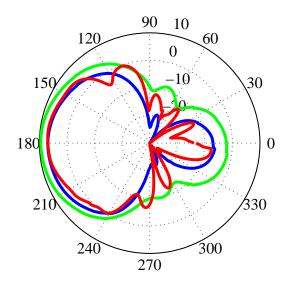

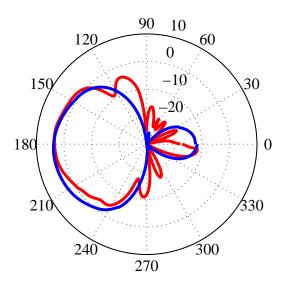

| 5.23 | Normalized measured 50 $\Omega$ patch antenna pattern (green). Predicted                                    |       |

|------|-------------------------------------------------------------------------------------------------------------|-------|

|      | DC power pattern for a power density of $200\mu\mathrm{W/cm^2}$ (blue). Mea-                                |       |

|      | sured rectifier-antenna pattern at power density of $200\mu\mathrm{W/cm^2}$                                 |       |

|      | (red)                                                                                                       | 110   |

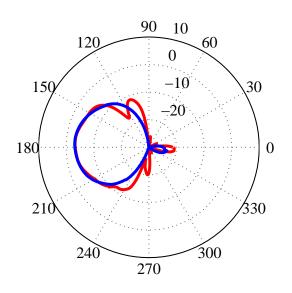

| 5.24 | DC power pattern for incident power densities of $100 \mu W/cm^2$ (a) and                                   |       |

|      | $25 \mu W/cm^2$ (b). Blue: Predicted DC power pattern. Red: Measured                                        |       |

|      | integrated rectifier-antenna DC power pattern                                                               | . 111 |

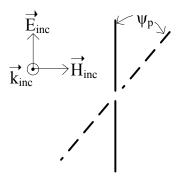

| 6.1  | PLF for transmitting and receiving linear wire antennas                                                     | 115   |

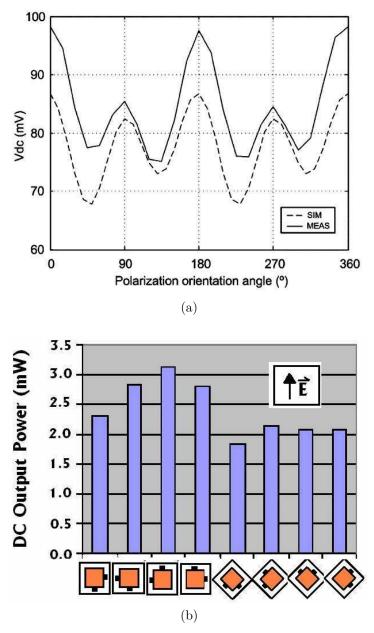

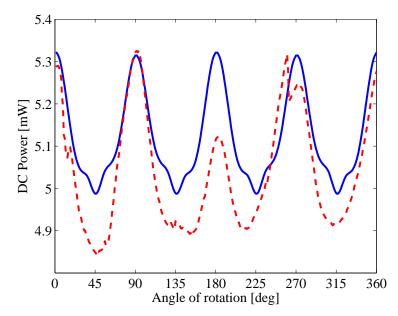

| 6.2  | Dc output voltage variation for different integrated rectifier antenna                                      |       |

|      | orientation angles relative to the input signal polarization ( $f =$                                        |       |

|      | $2.45\mathrm{GHz}, \mathrm{R_L} = 6.2\mathrm{k}\Omega).(\mathrm{a}).$ Measured histogram of DC power levels |       |

|      | for an incident power level of $170\mu\mathrm{W/cm^2}$ for different orientations                           |       |

|      | of the dual-polarized integrated rectifier antenna element, corre-                                          |       |

|      | sponding to different incident polarizations. The incident RF power                                         |       |

|      | is linearly polarized. (b)                                                                                  | 117   |

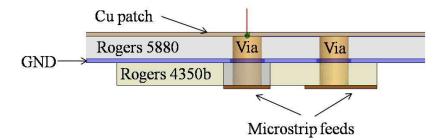

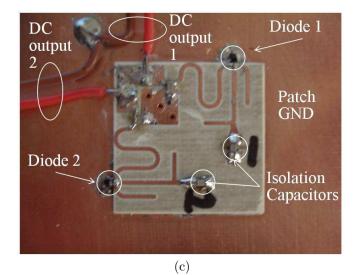

| 6.3  | Layer description of the substrate and copper stack-up used for a                                           |       |

|      | dual-polarized integrated rectifier antenna at $2.45\mathrm{GHz}.$                                          | 118   |

| 6.4  | Photograph of the dual rectifier circuit fabricated on Rogers 4350b.                                        |       |

|      | (1) via to antenna feed, $(2)$ diode location, $(3)$ quarter-wave long                                      |       |

|      | DC feed line. The line is meandered in order to make the overall                                            |       |

|      | dimensions of the circuit smaller (4), Resonant capacitor location,                                         |       |

|      | (5) DC output, (6) GND, (7) 3rd harmonic stub, (8) 5th harmonic                                             |       |

|      | stub. (6) and (5) are common to both rectifiers on the circuit. $\therefore$                                | 119   |

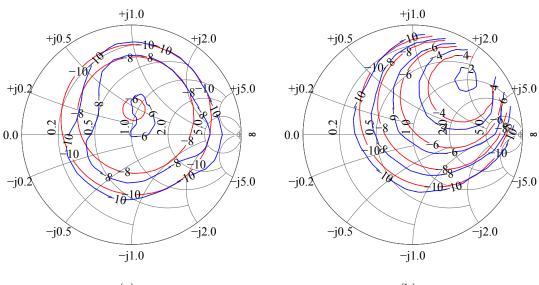

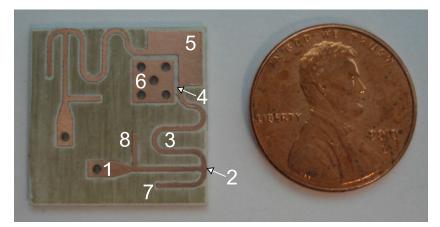

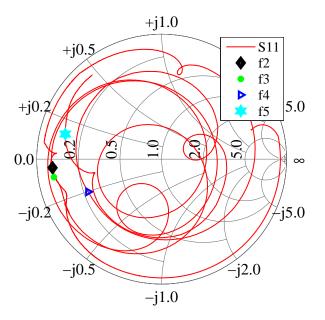

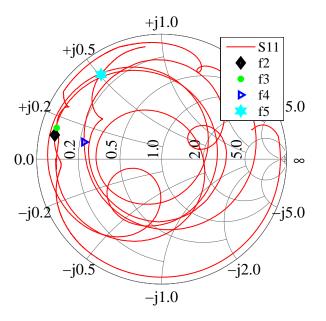

- 6.5 Simulated S<sub>11</sub> from 1 GHz to 12.25 GHz of a single rectifier circuit while the three ports are terminated with 50 Ω and port 1 is at the diode plane. The diamond markers are at the 2nd to 5th harmonics of the fundamental. The scattering parameters and the Smith chart is referenced to 50 Ω.

6.6 Measured S<sub>11</sub> from 2.45 GHz to 12.5 GHz of a single rectifier circuit

- 6.7 Measured S<sub>11</sub> including package inductance from 2.45 GHz to 12.5 GHz

of a single rectifier circuit while port 1 is at the diode plane port

2 is connected to the antenna feed and port 3 (The DC port) is

open. The diamond markers are at the 2nd to 5th harmonics of

the fundamental. The scattering parameters and the Smith chart is

referenced to 50 Ω.

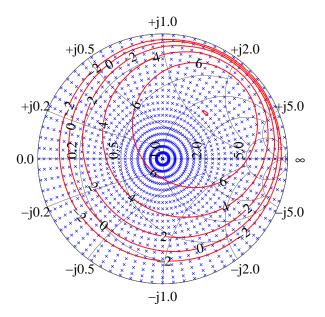

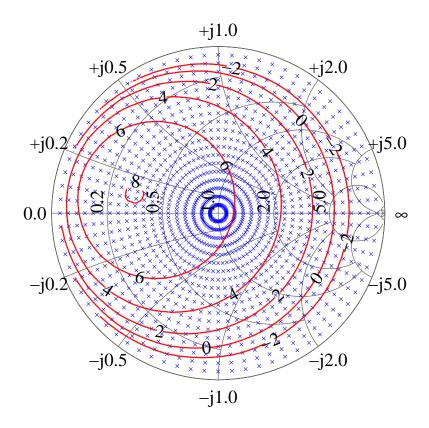

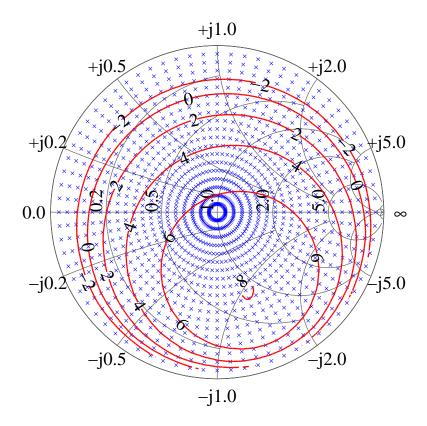

- 6.8 Simulated source-pull contours of constant DC power (in red) where the power is given in dBm. The input power to the rectifier is 10 dBm. The characteristic impedance of the chart is 50 Ω and the simulated tuner impedances are shown by blue x's.

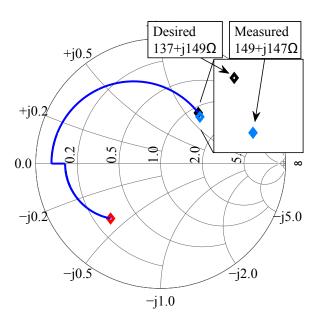

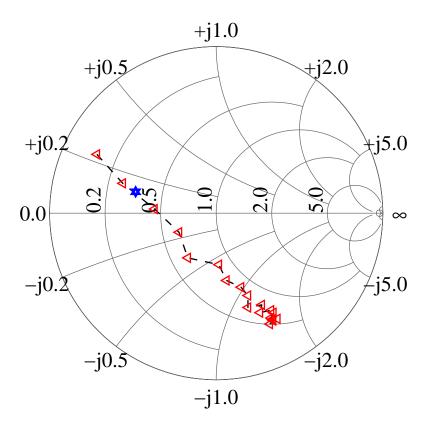

- 6.9 Input impedance at 2.45 GHz of a square patch antenna on a Rogers 5880 substrate, the patch size is  $40.3 \times 40.3$ . The red triangles are simulated points moving the feed away from the center of the patch from 2 mm to 20 mm at 1 mm intervals, The blue star is a measured impedance. The measurement was done using TRL calibration at 3.6 mm bringing the reference plane to the antenna feed. . . . . . 124

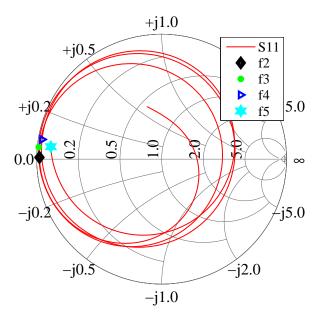

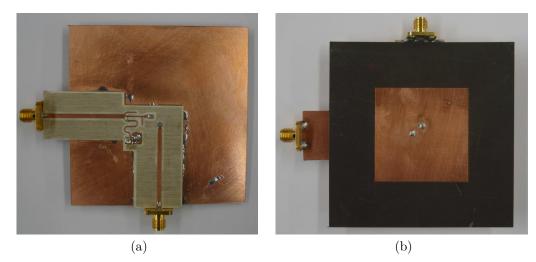

| 6.10 | (a) Photograph of the ground plane side of a patch antenna with                     |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | TRL calibration traces up to the via feed point (vertical trace) and                |     |

|      | an additional trace up to the diode plane of the rectifier loaded with              |     |

|      | the antenna (horizontal trace). Photograph of the front side of the                 |     |

|      | patch used for impedance verification (b).                                          | 125 |

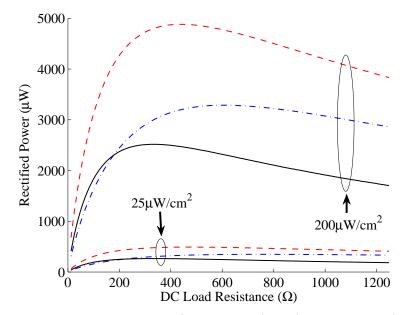

| 6.11 | Measured rectified power for eight incident power density levels                    |     |

|      | versus DC load for pol1 (a) and pol2 (b) co-polarized with the                      |     |

|      | linear-polarized transmitting antenna                                               | 125 |

| 6.12 | Estimated power contribution from each polarization on a $400\Omega$                |     |

|      | load. Blue solid is pol1 and dashed red is pol2                                     | 126 |

| 6.13 | Blue is total power of pol1 and pol2 estimation and red is the                      |     |

|      | measured power to a $400\Omega$ load at a power density of $200\mu\mathrm{W/cm^2}.$ | 127 |

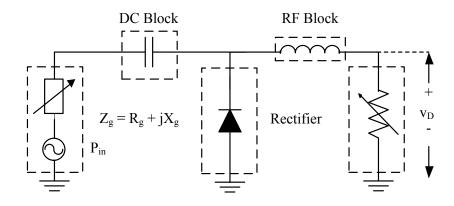

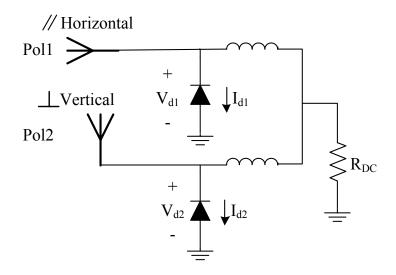

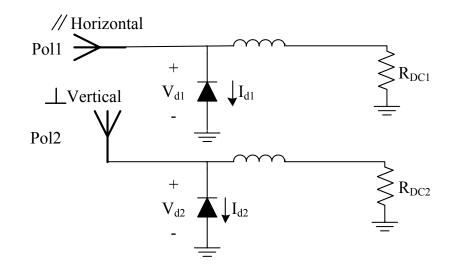

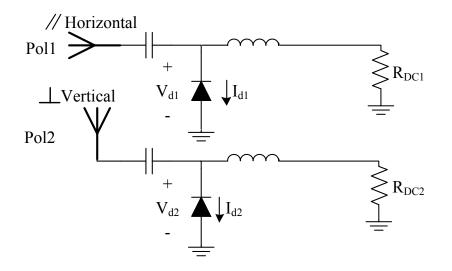

| 6.14 | Circuit description of a integrated patch antenna rectifier with a                  |     |

|      | common DC load for both polarizations                                               | 127 |

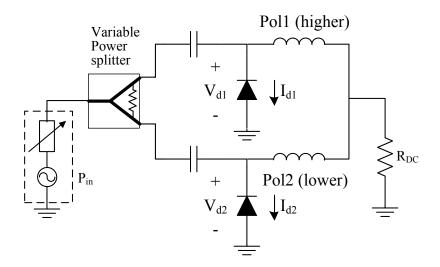

| 6.15 | Circuit schematic used in the harmonic balance simulation to simu-                  |     |

|      | late the time domain waveforms on the diodes in a dual polarization                 |     |

|      | rectifier antenna with a single DC load. The generator simulates                    |     |

|      | the dual polarized antenna and the variable power splitter simulates                |     |

|      | the polarization power split. The Pol1 branch is used to simulate                   |     |

|      | the rectifier receiving the higher power and Pol2 the lower power.                  | 129 |

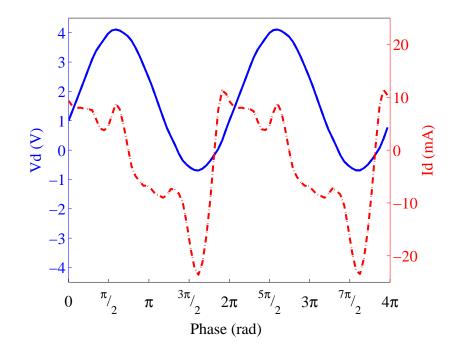

| 6.16 | Voltage (blue solid) and current (red dashed) waveforms across the                  |     |

|      | diodes. The voltage and current waveforms are identical on both                     |     |

|      | diodes, for $\psi_p = 45^{\circ}$ , i.e. pol1 = pol2                                | 130 |

|      |                                                                                     |     |

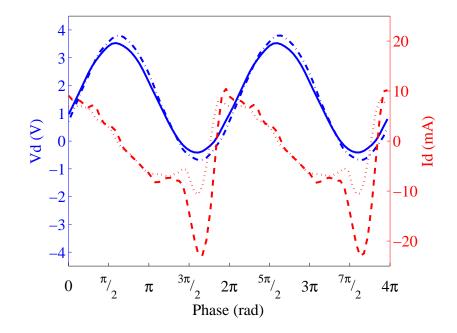

|       | 6.17 Simulated pol1 voltage (dashed blue) and current (red dashed), pol2 |  |

|-------|--------------------------------------------------------------------------|--|

|       | voltage (solid blue) and current (dotted red) waveforms across the       |  |

|       | diodes. The waveforms of pol1 are very similar to the expected           |  |

|       | reduced conduction angle rectifier waveform, indicating good RF-         |  |

|       | to-DC conversion efficiency through that branch of the circuit. On       |  |

|       | the other hand, the waveforms of Pol2 show the diode is not deep         |  |

|       | enough into forward bias, and the resulting RF-to-DC conversion          |  |

| . 131 | efficiency is reduced.                                                   |  |

|       | 6.18 Simulated pol1 voltage (dashed blue) and current (red dashed), pol2 |  |

|       | voltage (solid blue) and current (dotted red) waveforms across the       |  |

|       | diode. as in the previous simulated conditions, the rectifier that has   |  |

|       | the high power is operating with the expected reduced conduction         |  |

|       | angle intended for this rectifier. The second rectifier does not reach   |  |

|       | voltages that allow forward bias of the diode, reducing the RF-to-DC     |  |

| 132   | conversion efficiency.                                                   |  |

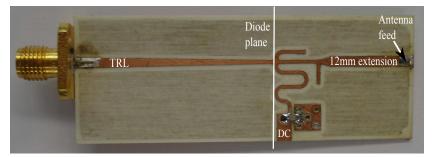

|       | 6.19 Photograph of the rectifier with the 12.5mm impedance matching      |  |

|       | length and a TRL trace for impedance measurement at the diode            |  |

| 132   | plane.                                                                   |  |

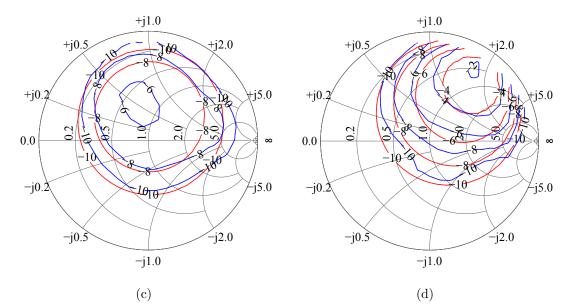

|       | 6.20 The Smith chart has all tuner impedances that were simulated        |  |

|       | labeled with blue X's and contours of constant DC power in red           |  |

|       | where the power is given in dBm. The input power to the rectifier        |  |

| 133   | is 10 dBm. The Smith chart is normalized to $50 \Omega$                  |  |

|       | 6.21 Circuit description of the separated DC loads of a integrated patch |  |

| 134   | antenna rectifier.                                                       |  |

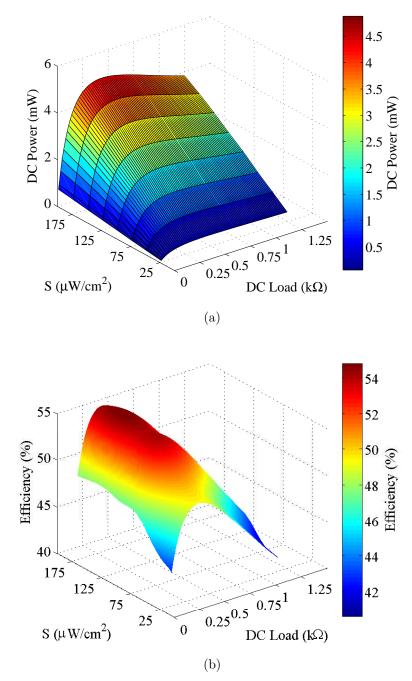

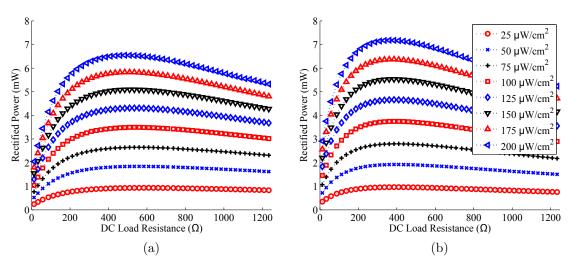

| 6.22 | Measured rectified power versus DC load at incident power densities                       |     |

|------|-------------------------------------------------------------------------------------------|-----|

|      | of 25 to $200\mu\mathrm{W/cm^2}$ for pol1 (a) and pol2 (b), both co-polarized             |     |

|      | with the transmitting antenna. Each of the measurements was taken                         |     |

|      | with the second DC port unloaded                                                          | 134 |

| 6.23 | Predicted power contribution from each polarization on a 400 $\Omega$ load.               |     |

|      | Blue solid pol1, and dashed red pol2                                                      | 135 |

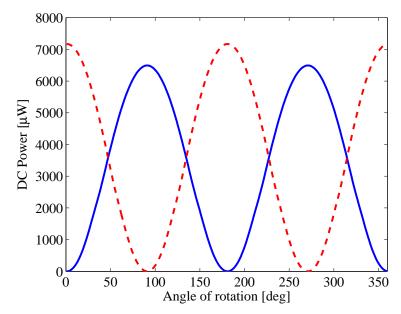

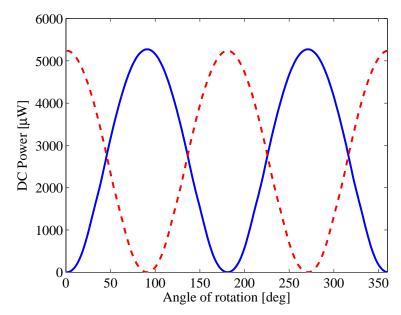

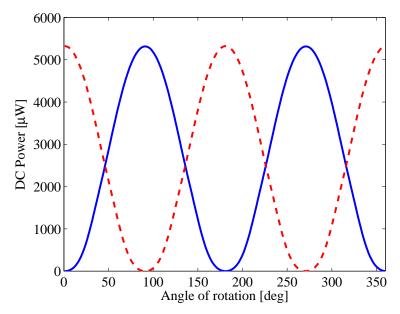

| 6.24 | Measured power on the two ports as the rectifier antenna is rotated                       |     |

|      | $360^\circ$ at a power density of $200\mu\mathrm{W/cm^2}$ (red). The predicted dependence |     |

|      | dence (blue) based on assumed DC-separated branches estimations                           |     |

|      | and red dashed is measured over the DC loads. $\ldots$                                    | 136 |

| 6.25 | Circuit description of the isolated DC path and separated DC loads                        |     |

|      | of a integrated patch antenna rectifier.                                                  | 137 |

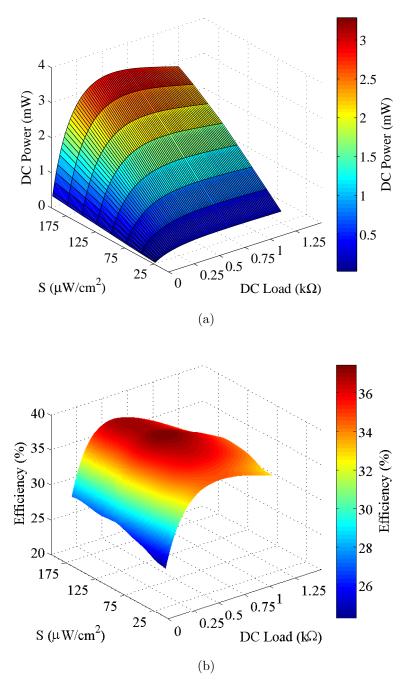

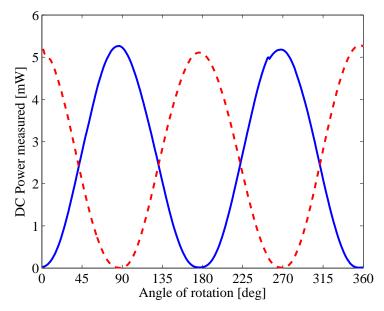

| 6.26 | Measured rectified power versus DC load at incident power densities                       |     |

|      | of 25 to $150\mu\mathrm{W/cm^2}$ for pol1 (a) and pol2 (b), both co-polarized             |     |

|      | with the transmitting antenna. Each of the measurements was taken                         |     |

|      | with the second DC port unloaded                                                          | 137 |

| 6.27 | Estimated power contribution from each polarization on a $400\Omega$ load                 |     |

|      | at a power density of $150\mu\mathrm{W/cm^2}.$ Blue solid is pol1 and dashed              |     |

|      | red is pol2                                                                               | 138 |

| 6.28 | Measured power contribution from each polarization on a $400\Omega$ load                  |     |

|      | at a power density of $150\mu\mathrm{W/cm^2}.$ Blue solid is pol1 and dashed              |     |

|      | red is pol2                                                                               | 139 |

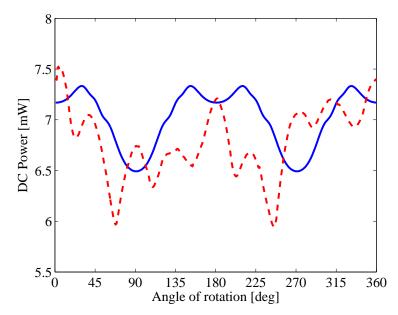

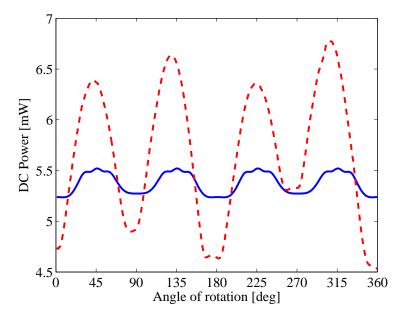

| 6.29 | Power on the two ports as the rectifier antenna is rotated by $360^\circ$                 |     |

|      | in a power density of $150\mu\mathrm{W/cm^2}.$ Blue estimated based on the                |     |

|      | separated co-polarized estimations and red dashed is measured over                        |     |

|      | the DC loads.                                                                             | 140 |

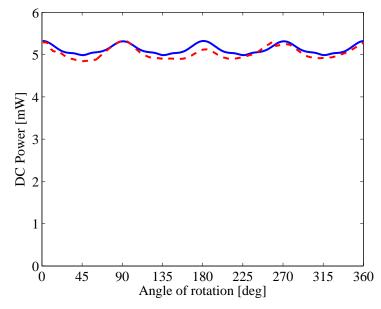

|      | in a power density of $150\mu\mathrm{W/cm^2}.$ Blue estimated based on the |     |

|------|----------------------------------------------------------------------------|-----|

|      | separated co-polarized estimations and red dashed is measured over         |     |

|      | the DC loads. The power scale has been changed to much finer in            |     |

|      | order to be able to see the small differences between the two traces.      | 141 |

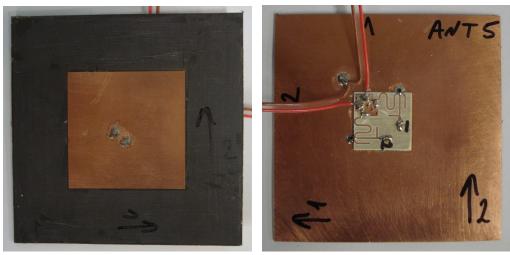

| 6.31 | Photographs of front side (a) ground plane and the two rectifiers          |     |

|      | (b) closeup of the two rectifiers(c), of the DC isolated dual polarized    |     |

|      | integrated rectifier antenna.                                              | 142 |

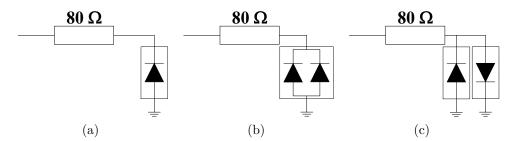

| 71   | Three diade rectifier topologies were measured and simulated using         |     |

6.30 Power on the two ports as the rectifier antenna is rotated by  $360^{\circ}$

- 7.1 Three diode rectifier topologies were measured and simulated using the same method: (a) single SMS-7630-79 Schottky diode, described in detail throughout the paper; (b) SMS-7621-74, two-diode package and (c) two anti-parallel SMS-7630-79 diodes.

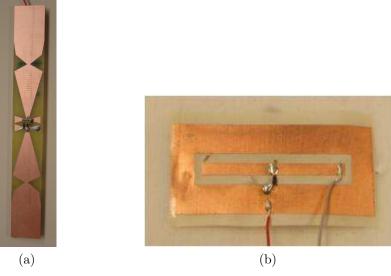

- 7.2 (a) 2.4 GHz dipole integrated directly with a diode. (b) Printed dipole at 915 MHz is reactively loaded to reduce the length to 100 mm, with a surface-mount inductor in the feed allowing for improved matching to the rectifier. (c) Printed 5.8 GHz folded slot on a flexible substrate and its measured rectified power. (d) Dual polarized patch antenna with Schottky diodes directly connected for small footprint at 5.8 GHz.

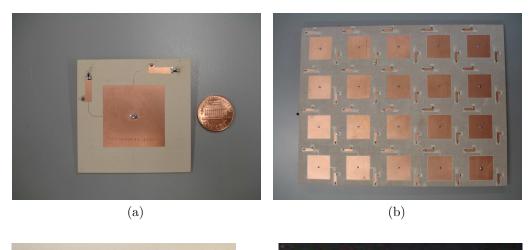

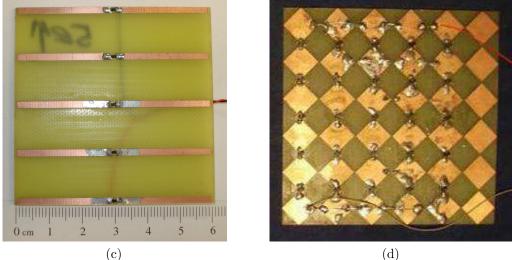

- 7.3 Single patch element 30 mil thick Rogers 4350b substrate at 1.96 GHz from the Sierra Nevada Corporation patch array (a). Patch array on 30 mil thick Rogers 4350b substrate used for Sierra Nevada Corporation Demo, size 300 mm × 240 mm at 1.96 GHz (b). Dipole array on 60 mil thick FR4 substrate used for Masco Demo, size 60 mm × 60 mm at 2.45 GHz, (c). Bow-tie integrated rectifier-antenna array. The squares are 1 cm on the side, and there are 16 Skyworks diodes in the array(d).

152

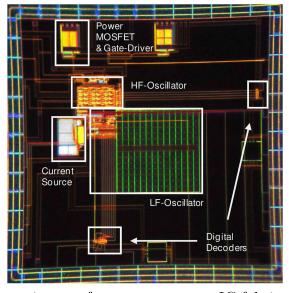

| 7. | 4 Microscope image of energy scavenger IC fabricated in 5 V, $0.35 \mu m$       |       |

|----|---------------------------------------------------------------------------------|-------|

|    | CMOS process. Various circuit components are labeled. The dimen-                |       |

|    | sions of the chip are $2 \text{ mm} \times 2 \text{ mm}$                        | 153   |

| 7. | 5 Photo of a 2.8 GHz patch antenna made from a battery and 60 mil               |       |

|    | FR4 substrate. Battery dimensions are $25\mathrm{mm}\times25\mathrm{mm}.$       | 155   |

| 7. | 6 Multi-sensor, multi-transmitter, general powering scenario                    | 156   |

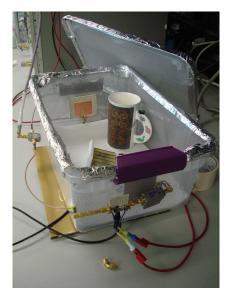

| 7. | 7 Photo of a charging box at 1.96 GHz, the box has two radiators                |       |

|    | oriented orthogonally to each other. The metal screening is used as             |       |

|    | a reflector that keeps all radiation within the box while the lid is            |       |

|    | closed. The reflections within the box make the orientation of the              |       |

|    | rectifier antenna irrelevant and power is harvested at all locations.           | 157   |

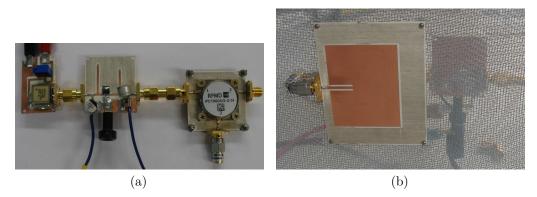

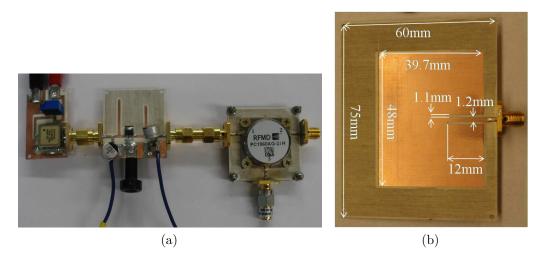

| 7. | 8 The powering chain composed of a VCO, amplifier and circulator                |       |

|    | (a). The patch antenna inside the charging box that connects to the             |       |

|    | powering chain (b)                                                              | 158   |

| 7. | 9 The powering chain composed of a VCO, amplifier and circulator                |       |

|    | (a) and patch antenna(b). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 178   |

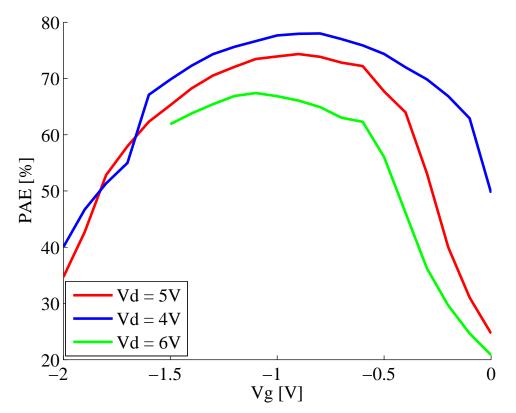

| 7. | 10 Measured Power added efficiency for the amplifier described above            |       |

|    | for different biasing voltages at $1.96$ GHz and input power of $18$ dBn        | n.179 |

## Chapter 1

### INTRODUCTION

Thought is a strenuous art - few practice it, and then only at rare times. —David Ben-Gurion

#### $C\,o\,{\rm N\,T\,E\,N\,T\,S}$

| 1.1 | MOTI  | IVATION                                     | 1 |

|-----|-------|---------------------------------------------|---|

|     | 1.1.1 | Introduction                                | 1 |

|     | 1.1.2 | Background Survey                           | 2 |

|     | 1.1.3 | Low-Power Non-Directional Wireless Powering | 5 |

|     | 1.1.4 | Thesis Outline                              | 9 |

#### 1.1 MOTIVATION

#### 1.1.1 INTRODUCTION

Many electronic devices operate in conditions where it is costly, inconvenient or impossible to replace a battery, or deliver wired power. As a result there has been an increased demand for wireless sensors for data gathering and transmission. Often the data is gathered at locations with accessibility issues, sensors need to be covert and where the sensor maintenance is not trivial. Some examples are implanted sensors for medical diagnostics and therapy [5], structural monitoring sensors [6], sensors inside hazardous manufacturing or other hazardous environments, sensors for health monitoring of patients or in assisted living environments [7], aircraft health monitoring [8], sensors for covert operations, etc. For any low power sensor that operates at a low duty cycle, and in an environment with low levels of light or vibration, RF wireless powering offers the potential for maintenance-free operation.

#### 1.1.2 BACKGROUND SURVEY

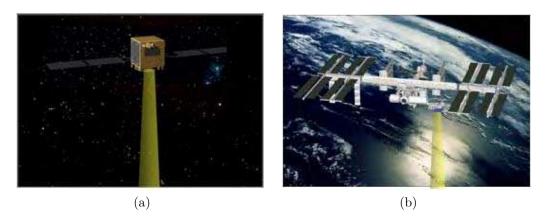

In the past, wireless power beaming with directive antennas has been demonstrated for various applications such as solar power satellite (SPS) where power would be collected on large solar panels and beamed to earth or power transfer from one part of a satellite to another as illustrated in Fig 1.1. [9, 10, 11, 12, 13]. In

Figure 1.1: Microwave power transmission experiment in space on a small satellite and on the International Space Station.

most of this work, directive antennas were used with high power densities, on the order of a few  $10^4 \mu W/cm^2$  with efficiencies ranging from 20% to 80%. In 1975 Jet Propulsion Laboratory (JPL) and Raytheon demonstrated power transfer on gourd to validate this concept [14]. In this experiment power was transferred over

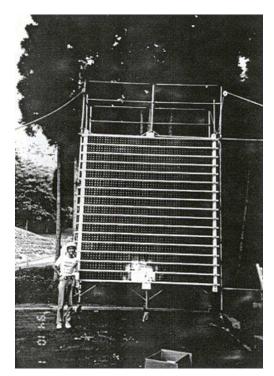

1.6 km. The transmitted power was 450 kW and the DC power recovered by a the rectifying antenna with an area of  $24 \text{ m}^2$  was 30 kW. The proposed SPS in [10], is a satellite placed in geostationary orbit and generating very high power levels, on the order of 5 GW. The power would be generated by solar cells and be transmitted at a frequency of 2.45 GHz to the rectifying antenna on the ground, a photograph of the proposed rectifying antenna is seen in Fig. 1.2. The rectifying antenna array is composed of 256 sub-arrays, each composed form 9 elements totaling at 2304 elements.

Figure 1.2: The rectifying antenna array used in Shinohara's field experiment at a frequency of 2.45 GHz. The size is  $3.2 \text{ m} \times 3.6 \text{ m}$ .

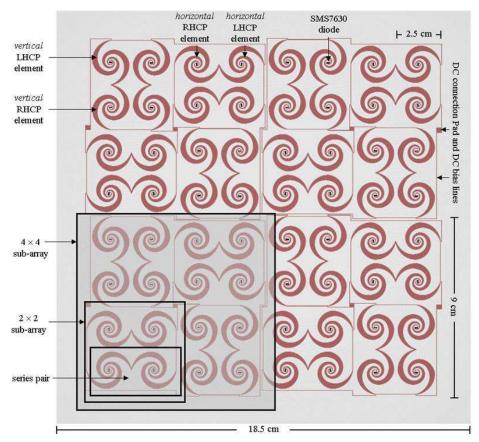

In [15], a large dipole array (8 by 6) with a  $5 \,\mu W/cm^2$  incident power density was coupled to a single rectifier with a corporate feed. This is the first low-power density rectifying antenna work reported in the literature, the power densities are a factor of 10000 times less than the previous work. Since a corporate feed is used, the incident power to the rectifying diode is the power collected by all array elements and is on the order of 20 mW. According to [15], that is the power level where efficiency is maximized for the diode used in that work. Combining the power from all elements of the array increases the power to the rectifier, but the non-directive properties of the single element rectifying antenna are lost. In [16], 64 spiral antenna elements with integrated Schottky diodes with connected DC lines, seen in Fig. 1.3, were used to receive and rectify very low power densities in the  $\mu$ W/cm<sup>2</sup> range. In this work, each antenna element is connected to a rectifying diode, keeping the non-directive properties of each element. In addition, the power is collected from any arbitrary polarization incident on the rectifying antenna array.

Figure 1.3: Layout of the 64-element array. Received RF power is rectified at each spiral locally and the combined dc power for all elements is extracted using two dc collection lines at the edges of the array (not shown).

Wirelessly powered devices include RFIDs, these devices are widely used for supply chain management and inventory control. The RFIDs are powered by the interrogating radio-frequency wave, typically in the UHF frequency range [17] [18]. Usually, the RFID distances are short and the device operates only when the interrogating wave delivers sufficient power density to the usually inefficient RFID antenna. Since the wavelength used for powering is larger or on the order of the powering range, the antennas on the power transmitter and RFID tag are in each other's near fields, and the energy is transferred via either capacitive or inductive coupling. In recent years, the field of active RFID has been evolving. Active RFID tags have a built in power supply, such as a battery, as well as electronics that perform specialized tasks independent of the interrogating signal. Since the tags have a power supply that needs charging, the fields of active RFID and far-field wireless powering are merging [19, 20]. However, the approach in this thesis differs from active RFID in that the powering is done independent from the interrogation signal.

In addition to RFIDs, other near-field powered RF devices include toothbrushes, implants [5], resonantly powered devices [21] and recently, different phone and tablet-computer chargers [22]. The principle of operation is of a power transformer, where by magnetic induction, the power is transferred form the primary coil to the secondary coil. In [22] the efficiency is increased by using resonant structured for the transmit and receive coils at the same frequency. A photograph of a 60 W light-bulb powered from a 2 m distance is shown in 1.4.

#### 1.1.3 LOW-POWER NON-DIRECTIONAL WIRELESS POWERING

In this work, we investigate single integrated antenna-rectifier elements with incident power densities in the 25-200  $\mu$ W/cm<sup>2</sup> range. This thesis focuses on a design methodology for low-power non-directional far-field wireless powering. In the block

Figure 1.4: 60 W light-bulb being lit from 2 m away. Note the "obstruction" in the center. The loop radius is 25 cm and the frequency is 9.9 MHz.

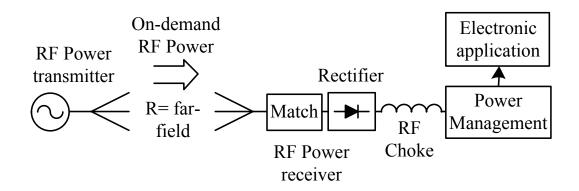

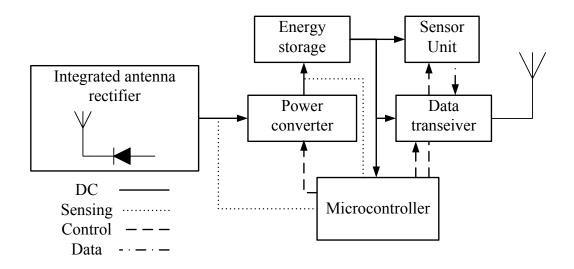

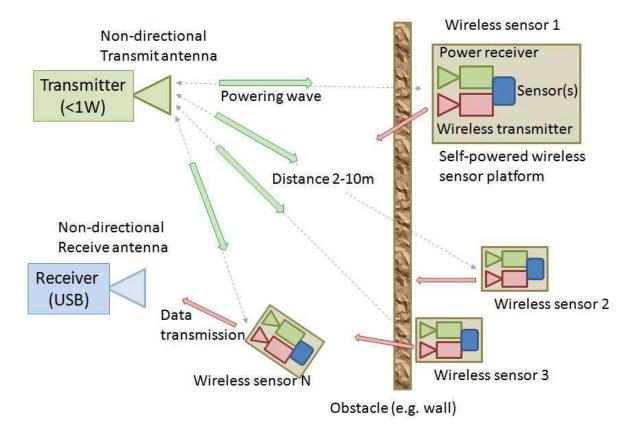

diagram in Fig. 1.5, the power receiver consists of one or more antennae which receive plane waves transmitted by the powering source, and deliver the RF power to a rectifying element. The resulting DC power is optimally transferred to the electronic application via a power management circuit. The powering is independent of the electronic application which can include wireless transmission of sensor data [7].

Table 1.1 gives an overview of example far-field power receiving devices described in the literature. It is important to note that the efficiencies are listed as reported in the papers, but they cannot be directly compared due to the different power levels and perhaps more critically, different efficiency definitions. For example, most work, does not include the antenna efficiency or coupling efficiency from antenna to the rectifier. The power incident on the rectifier is measured in a circuit with no antenna or estimated from simulation. In some cases, the incident power density is also provided. In [23, 24, 25, 26, 30] power levels incident on the diode are in 100mW range with 40% to 82% rectification efficiency. In [30], the rectifier was directly connected to a generator, with no antenna. In [27], the 42% efficiency is measured

Figure 1.5: Block diagram of a wireless powering system. An RF power transmitter transmits a plane wave incident on a rectenna element or array (RF power receiver). Following rectification is a DC stage with power management. In this paper, we consider a narrowband low power non directional power transmitter. The electronic application for this study is a wireless sensor platform. The power density at the receiver is between 25 to  $200\mu W/cm^2$ .

| Ref  | f (GHz) | $P_{RF,in}$                              | n Antenna                    |        |

|------|---------|------------------------------------------|------------------------------|--------|

| [23] | 5.8     | 50mW LP dipole omni-dir                  |                              | 82%    |

| [24] | 5.8     | 105mW LP dipole omni-dir                 |                              | 67%    |

| [25] | 2.45    | $316\mathrm{mW}$                         | 6mW LP 4 element patch array |        |