# Efficiency Enchancement Techniques for the Outphasing Power Amplifier

by

MICHAEL PHILIP LITCHFIELD B.S., University of New Hampshire, 2011 M.S., University of Colorado at Boulder, 2014

A thesis submitted to the

Faculty of the Graduate School of the

University of Colorado in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

May 2016

This thesis entitled:

Efficiency Enchancement Techniques for the Outphasing Power Amplifier

written by Michael Philip Litchfield

has been approved for the Department of Electrical and Computer Engineering

Zoya Popović

Dejan Filipović

Tibault Reveyrand

David Choi

Khurram Afridi

Taylor Barton

Date \_\_\_\_\_

The final copy of this thesis has been examined by the signatories, and we

find that both the content and the form meet acceptable presentation standards

of scholarly work in the above mentioned discipline.

Litchfield, Michael Philip (Ph.D., Electrical Engineering)

Efficiency Enchancement Techniques for the Outphasing Power Amplifier

Thesis directed by Professor Zoya Popović

Modern communication and radar signals increasingly utilize signals with high peak-to-average power ratios to achieve spectral efficiency. Three power amplifier architectures have been developed to efficiently amplify such signals one of which is outphasing. At high frequencies, such as X-band, outphasing requires enhancement in the form of discrete supply modulation or rectification to achieve performance competitive with alternatives such as Doherty and envelope tracking. This thesis focuses on the development, theoretically and experimentally, of the outphasing power amplifier, including enhanced modes of operation.

A novel quasi-MMIC outphasing PA and measurement setup are developed to enable the direct measurement of power waves internal to the PA architecture, yielding internal PA performance and load modulation. Due to the flexibility of the PA prototype and measurement setup, both isolated and non-isolated combiners are utilized with and without discrete supply modulation. Insight into the dynamic operation of five outphasing variations is gained.

Two enhanced outphasing PAs are fully integrated on GaN MMICs. A power recycling LINC PA makes use of the duality between a high efficiency PA and rectifier to recover power wasted in the isolated combiner. A multi-level Chireix outphasing PA utilizes discrete supply modulation to minimize DC power consumption, thereby improving efficiency at back-off. Realistic testing with a GaN discrete supply modulator MMIC shows particular promise for the novel multi-level Chireix outphasing architecture.

Finally, the importance of the gain of power amplifiers internal to the outphasing architecture is substantiated in simulation and measurement. Highly efficient multi-stage power amplifiers are optimized through the development of harmonically terminated interstage matching networks.

# DEDICATION

To my gracious God.

### ACKNOWLEDGMENTS

There are many people who are deserving of my gratitude for their support and contributions to this thesis. First, I would like to extend my gratitude to my adviser, Zoya Popović, whose support and guidance has been essential to the completion of this thesis. She is truly dedicated to her students, both in the classroom and the research lab, working extremely hard to take advantage of every opportunity for their development. I have benefited greatly the consistent funding, many guest lecturers, and generosity toward conference attendance that Zoya has provided.

I would also like to thank the rest of my committee members for their time and valuable feedback. I have learned a tremendous amount from Prof. Dejan Filipovic in several of his classes, and thoroughly enjoy his teaching style. Dr. David Choi has lent his expertise to help refine my research. I am indebted to Dr. Tibault Reveyrand for his aid in our joint outphasing measurements, and teaching some of his mastery of microwave measurements. Prof. Khurram Afridi has provided power electronics expertise. I have learned a lot from fellow outphasing researcher Prof. Taylor Barton through her widely presented work.

For financial support of the research in this thesis, I would like to thank DARPA for their forward looking research goals in RF transmitters, as well as Rockwell Collins, for their partnership on this program. Specifically, I would like to thank Andy Walker and Chenggang Xie for their feedback and collaboration. Futurewei has also funded the two-stage, base station PA research through a CoPEC fellowship.

I would like to express my deep gratitude to Dr. Charles Campbell, who has taught me so much about MMIC design during our MPC design reviews. Dr. David Sardin and Dr. Mike Roberg have also taken significant time to help me learn PA concepts and MMIC design at the beginning of my research. Dr. Asmita Dani has taught me how to use much of the lab equipment; a deed I have sought to pay forward. I would like

to thank Dr. Andrew Zai and Dr. Scott Schafer for their teamwork in our MMIC runs, for helping me refine my understanding of RF concepts, and for their assistance with the many problems that arise in research. I am grateful for Ignacio Ramos, Mike Coffey, Sushia Rahimizadeh, Parisa Momenroodaki, and all the others I have had the pleasure of overlapping with during my time in Zoya's group.

I am thankful for the community at Cornerstone church, who have treated my wife and I like family since our move to Boulder. I have been especially blessed by the support and brotherhood of David Reens, John Wanberg, and Matt Kreider, who have heavily invested their time and energy into my life.

Finally, I am extremely grateful for the love and support of my family. First, to my wife Kaitlin Litchfield, thank you for your constant support and encouragement. You have helped me keep a godly perspective throughout this journey. To my parents, Phil and Trayce Litchfield, thank you for your continual support and belief in me. To my sister, Jamie, thank you for leading the way for me; your example in school always motivated me to work hard. To my in-laws, George and Sandy Kwiecien, as well as Kristen, Kailee, and Connor, I am blessed that you have always supported me like one of your own. To our whole New Hampshire family, thank you for sharing us with Colorado for the past few years; we are excited to be coming home.

## Contents

| T | ABLE  | OF C         | ONTENTS                                       | vii  |

|---|-------|--------------|-----------------------------------------------|------|

| L | IST O | <b>б</b> Тав | LES                                           | xii  |

| L | ist o | f Figu       | JRES                                          | xiii |

| 1 | Int   | RODU         | CTION                                         | 1    |

|   | 1.1   | Васко        | ground and Motivation                         | 2    |

|   |       | 1.1.1        | Communication Signals                         | 2    |

|   |       | 1.1.2        | Radar Signals                                 | 5    |

|   |       | 1.1.3        | High Efficiency Power Amplifiers              | 6    |

|   |       |              | 1.1.3A Efficiency Definitions                 | 7    |

|   |       | 1.1.4        | High Efficiency Power Amplifier Architectures | 8    |

|   |       | 1.1.5        | DARPA Microscale Power Conversion Program     | 11   |

|   | 1.2   | THESIS       | S Organization                                | 12   |

| 2 | Сн    | IREIX        | Outphasing                                    | 14   |

|   | 2.1   | Chire        | ix Outphasing Theory                          | 16   |

|   | 2.2   | Нідн I       | Efficiency GaN MMIC PA Design                 | 26   |

|   |       | 2.2.1        | Qorvo 0.15 μm GaN Process                     | 28   |

|   |       | 2.2.2        | MMIC Design                                   | 29   |

|   |       |              | 2.2.2A GATE BIAS TEE                          | 29   |

|   |       |              | 2.2.2b Input Matching Network                 | 31   |

|   |     |        | 2.2.2c Output Matching Network                                                                                                              | 33 |

|---|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |     |        | 2.2.2d Final Simulations                                                                                                                    | 34 |

|   |     | 2.2.3  | Measurement Setup and Calibration                                                                                                           | 36 |

|   |     | 2.2.4  | MMIC Measurements                                                                                                                           | 39 |

|   | 2.3 | Chirei | Combiner Design                                                                                                                             | 41 |

|   | 2.4 | Intern | L PA Performance and Load Modulation Measurements                                                                                           | 44 |

|   |     | 2.4.1  | Measurement Setup and Calibration                                                                                                           | 44 |

|   |     | 2.4.2  | Measurement Results                                                                                                                         | 46 |

|   |     | 2.4.3  | Linearity Issues and Indicators                                                                                                             | 49 |

|   | 2.5 | Concl  | SION                                                                                                                                        | 51 |

| 3 | LIN | JC     | 5                                                                                                                                           | 53 |

|   | 3.1 | LINC ' | HEORY                                                                                                                                       | 54 |

|   | 3.2 | Intern | L PA Performance and Load Modulation Measurements                                                                                           | 59 |

|   |     | 3.2.1  | Rat-Race Combiner                                                                                                                           | 59 |

|   |     | 3.2.2  | Measurement Results                                                                                                                         | 61 |

|   |     | 3.2.3  | Linearity Indicators                                                                                                                        | 63 |

|   | 3.3 | Concl  | $SION \ldots \ldots$ | 64 |

| Λ | Sur | N v Ia | DDULATED LINC                                                                                                                               | 66 |

| 4 |     |        |                                                                                                                                             |    |

|   | 4.1 |        |                                                                                                                                             | 68 |

|   | 4.2 | Asymn  | TRIC MULTILEVEL OUTPHASING THEORY                                                                                                           | 69 |

|   | 4.3 | Intern | L PA Performance and Load Modulation Measurements                                                                                           | 73 |

|   |     | 4.3.1  | ML-LINC Measurement Results                                                                                                                 | 73 |

|   |     | 4.3.2  | AMO Measurement Results                                                                                                                     | 76 |

|   |     | 4.3.3  | Linearity Indicators                                                                                                                        | 79 |

|   | 4.4 | Concl  | sion                                                                                                                                        | 82 |

| 5 | Mu  | lti-Li | evel Chireix Outphasing                                     | 83 |

|---|-----|--------|-------------------------------------------------------------|----|

|   | 5.1 | Multi  | -Level Chireix Outphasing Theory                            | 84 |

|   | 5.2 | Intern | NAL PA Performance and Load Modulation Measurements         | 86 |

|   |     | 5.2.1  | ML-CO Combiner Design                                       | 86 |

|   |     | 5.2.2  | Measurement Results                                         | 88 |

|   |     | 5.2.3  | Linearity Indicators                                        | 92 |

|   |     | 5.2.4  | Prediction of Load Modulation Distortion                    | 93 |

|   | 5.3 | Multi  | -Level Chireix Outphasing GaN MMIC PA                       | 95 |

|   |     | 5.3.1  | ML-CO MMIC Design                                           | 96 |

|   |     |        | 5.3.1a Output Harmonic Terminations                         | 96 |

|   |     |        | 5.3.1b Input Matching Network                               | 02 |

|   |     |        | 5.3.1c Combiner Design                                      | 04 |

|   |     | 5.3.2  | Measurement Setup                                           | 08 |

|   |     |        | 5.3.2A GAN POWER-DAC MMIC                                   | 12 |

|   |     | 5.3.3  | ML-CO Measurement Results                                   | 14 |

|   | 5.4 | Concl  | usion                                                       | 19 |

| 6 | Pov | ver R  | ECYCLING LINC 1                                             | 21 |

|   | 6.1 | Power  | Recycling LINC Theory                                       | 22 |

|   | 6.2 | Micro  | wave Rectifiers                                             | 26 |

|   | 6.3 | Time F | Reversal Duality of Power Amplifiers                        | 27 |

|   | 6.4 | X-Ban  | D GAN MMIC PA and Rectifier Measurements                    | 28 |

|   |     | 6.4.1  | Power Amplifier Measurements                                | 29 |

|   |     | 6.4.2  | Rectifier Measurements                                      | 30 |

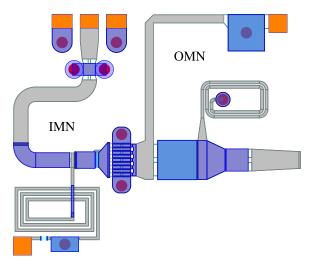

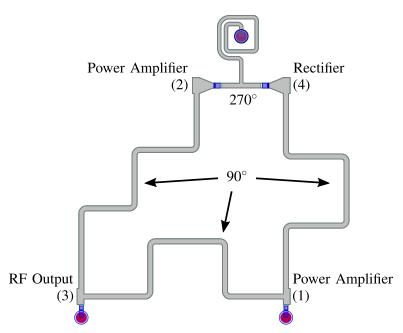

|   | 6.5 | Power  | RECYCLING LINC GAN MMIC PA                                  | 37 |

|   |     | 6.5.1  | MMIC Design                                                 | 38 |

|   |     |        | 6.5.1 A INTERNAL POWER AMPLIFIER & RECTIFIER CIRCUIT DESIGN | 38 |

|   |     |        | 6.5.1b Combiner Design                           |

|---|-----|--------|--------------------------------------------------|

|   |     |        | 6.5.1c Final Simulations                         |

|   |     | 6.5.2  | Measurement Setup and Method                     |

|   |     | 6.5.3  | Outphasing Measurement Results                   |

|   | 6.6 | Concl  | JSION                                            |

| 7 | HA  | RMON   | CALLY TERMINATED INTERSTAGE MATCHING NETWORK 154 |

|   | 7.1 | Casca  | Ded Efficiency Analysis                          |

|   |     | 7.1.1  | Cascaded Drain Efficiency                        |

|   |     | 7.1.2  | Cascaded Power-Added Efficiency                  |

|   | 7.2 | Bi-Dif | ectional Matching                                |

|   |     | 7.2.1  | Change of Reference Impedance                    |

|   |     | 7.2.2  | Conjugate Match Example                          |

|   |     | 7.2.3  | Intentional Mismatch Example                     |

|   | 7.3 | Harm   | NICALLY TERMINATED INTERSTAGE MATCHING NETWORKS  |

|   |     | 7.3.1  | Lumped Element ISMNs                             |

|   |     |        | 7.3.1a Class-F                                   |

|   |     |        | 7.3.1b Inverse Class-F                           |

|   |     | 7.3.2  | TRANSMISSION LINE ISMNs                          |

|   |     |        | 7.3.2a Class-F                                   |

|   |     |        | 7.3.2b Inverse Class-F                           |

|   |     |        | 7.3.2c Arbitrary Phase Harmonic Terminations     |

|   |     | 7.3.3  | DISCUSSION                                       |

|   | 7.4 | ISMN   | Design Example                                   |

|   | 7.5 | Concl  | JSION                                            |

| 8 | Cor | NCLUS  | on and Future Work 190                           |

|   | 8.1 | Summ   | ry                                               |

|   | 8.2   | Futur  | e Work                                                | 191 |

|---|-------|--------|-------------------------------------------------------|-----|

|   | 8.3   | Contr  | IBUTIONS                                              | 193 |

| B | IBLIC | OGRAP  | НҮ                                                    | 197 |

| A | Off   | -Reso  | DNANCE LUMPED ELEMENT RESONATOR EQUIVALENT COMPONENTS | 215 |

|   | A.1   | Series | Resonator                                             | 215 |

|   |       | A.1.1  | Below Resonance $(x < 1)$                             | 216 |

|   |       | A.1.2  | Above Resonance $(x > 1)$                             | 216 |

|   | A.2   | PARAL  | LEL RESONATOR                                         | 217 |

|   |       | A.2.1  | Below Resonance $(x < 1)$                             | 217 |

|   |       | A.2.2  | Above Resonance $(x > 1)$                             | 217 |

| A | PPEN  | IDICES |                                                       |     |

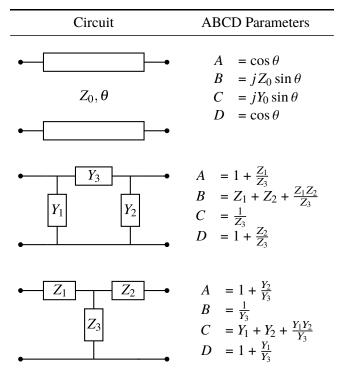

| В | TRANSMISSION LINE EQUIVALENT NETWORKS | 218 |

|---|---------------------------------------|-----|

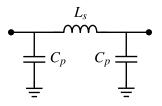

|   | B.1 Low-Pass Equivalent Networks      | 219 |

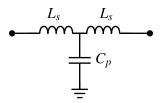

|   | B.2 High-Pass Equivalent Networks     | 221 |

# LIST OF TABLES

| 2.1         | Chireix outphasing PA Performance                                            |

|-------------|------------------------------------------------------------------------------|

| 2.2         | Measured gain and phase imbalance                                            |

| 3.1         | Comparison of Chireix outphasing and LINC system performance                 |

| 3.2         | Comparison of measured gain and phase imbalance                              |

| 4.1         | Measured system performance of supply modulated LINC PAs                     |

| 4.2         | Measured gain and phase imbalance in supply modulated LINC PAs               |

| 5.1         | Measured system performance of supply modulated outphasing PAs               |

| 5.2         | Measured gain and phase imbalance in supply modulated outphasing PAs         |

| 5.3         | Average total efficiency with restricted supply levels                       |

| 6.1         | Comparison of power amplifier and rectifier operation                        |

| 7.1         | Optimal ISMN harmonic impedances                                             |

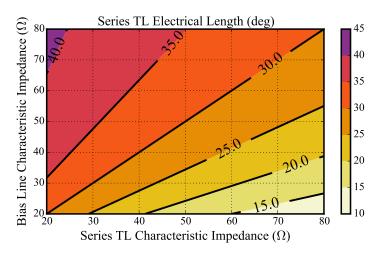

| 7.2         | ISMN series TL electrical lengths constrained by harmonic termination phases |

| <b>B</b> .1 | ABCD Parameters for Networks                                                 |

# LIST OF FIGURES

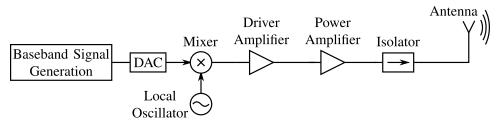

| 1.1 | Wireless transmitter block diagram. The modulated signal is generated digitally at baseband            |   |

|-----|--------------------------------------------------------------------------------------------------------|---|

|     | for the desired application, before being converted to the analog domain. After it is upcon-           |   |

|     | verted to the carrier frequency, it is amplified by several linear gain stages and finally, the        |   |

|     | power amplifier, before it is converted to a free-space traveling wave by the antenna                  | 2 |

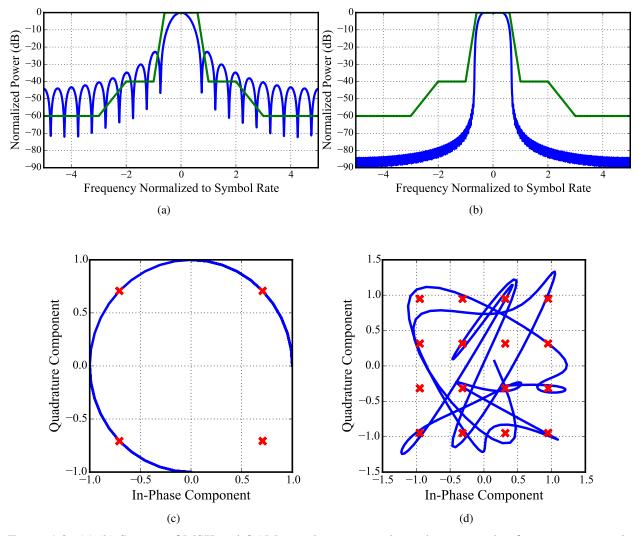

| 1.2 | (a),(b) Spectra of MSK and QAM signals, respectively, with an example of an emission                   |   |

|     | mask. (c), (d) Constellation diagrams (red x's) corresponding to 10 symbol MSK and QAM                 |   |

|     | signals, respectively. The blue line represents a time $\Delta t$ of the continuously received signals |   |

|     | corresponding to 20 symbols                                                                            | 3 |

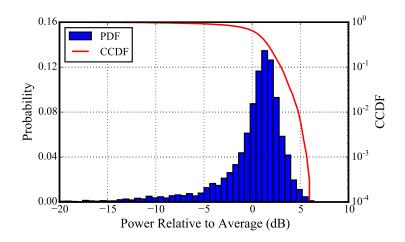

| 1.3 | PDF and CCDF of a 4-QAM signal, demonstrating a 6 dB peak-to-average ratio                             | 4 |

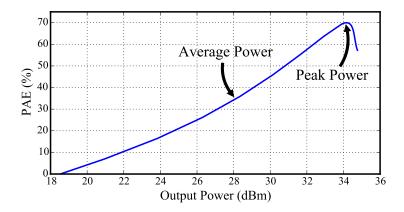

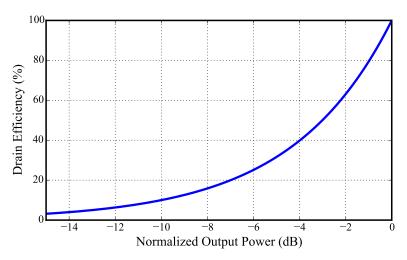

| 1.4 | Non-ideal class-B GaN MMIC PA efficiency as a function of output power, demonstrating                  |   |

|     | poor efficiency roll-off with output power typical of single ended PAs                                 | 5 |

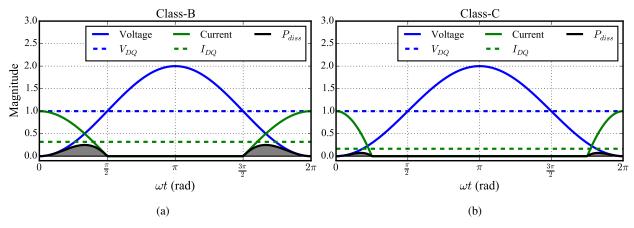

| 1.5 | Intrinsic drain voltage and current waveforms, along with dissipated power for (a) class-B,            |   |

|     | and (b) class-C operation.                                                                             | 7 |

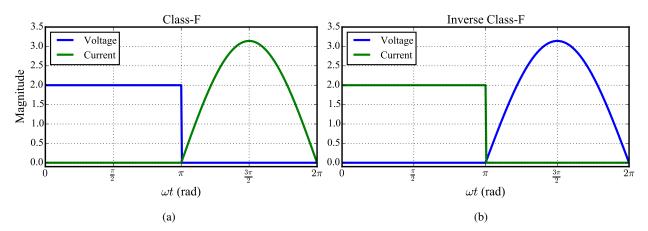

| 1.6 | Intrinsic drain voltage and current waveforms for (a) class-F, and (b) inverse class-F operation.      | 7 |

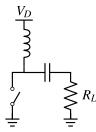

| 1.7 | Simplified circuit for saturated power amplifier.                                                      | 9 |

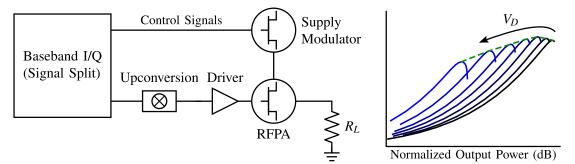

| 1.8 | Supply modulation block diagram and efficiency. In this architecture, the modulated signal             |   |

|     | is split into high and low frequency paths. At low frequency (modulation bandwidth), the               |   |

|     | supply modulator varies the supply for the high frequency PA, to maintain efficient operation.         | 9 |

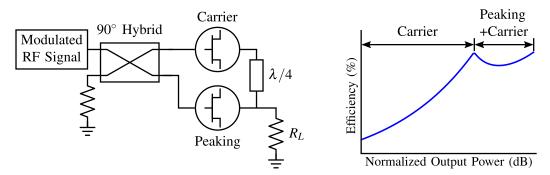

| 1.9  | Doherty bock diagram and efficiency. This architecture combines two, asymmetric PAs.                    |    |

|------|---------------------------------------------------------------------------------------------------------|----|

|      | At low input powers, the peaking amplifier is off, and the carrier amplifier operates. As               |    |

|      | input power increases, the peaking amplifier turns on, modulating the loads of both PAs to              |    |

|      | maintain saturation and high efficiency.                                                                | 10 |

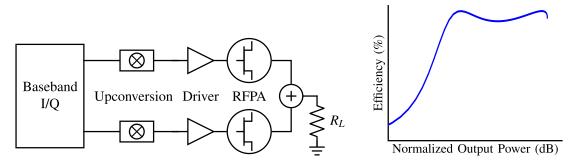

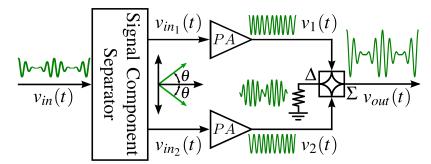

| 1.10 | Outphasing block diagram. In this architecture, two symmetric high-frequency PAs interact               |    |

|      | through a non-isolated combiner. Differential phase modulation at the input controls the                |    |

|      | output power through the interaction between PAs.                                                       | 11 |

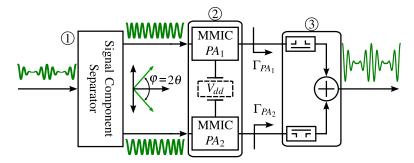

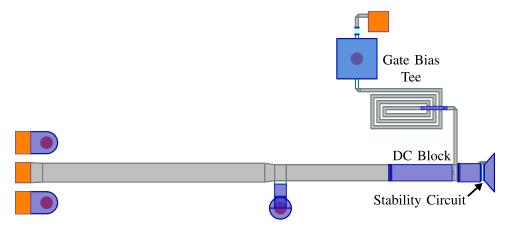

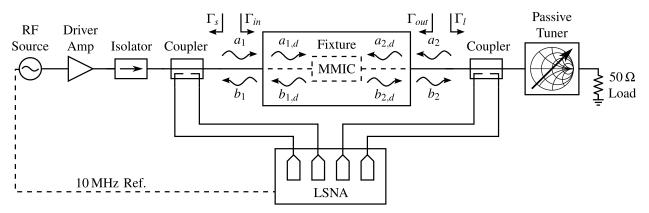

| 2.1  | Flexible, MMIC-based outphasing block diagram with off-chip combiners that include bi-                  |    |

|      | directional couplers for the direct measurement of power waves, enabling internal PA per-               |    |

|      | formance and load modulation measurement.                                                               | 16 |

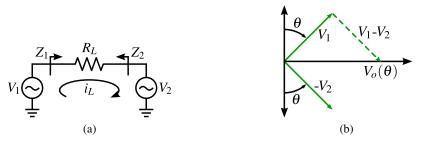

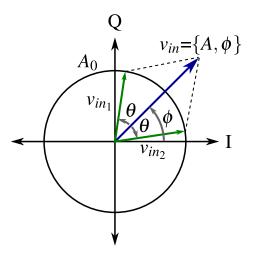

| 2.2  | (a) Simple outphasing circuit diagram, and (b) vector representation of idealized voltage               |    |

|      | sources                                                                                                 | 17 |

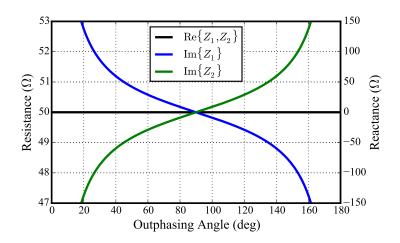

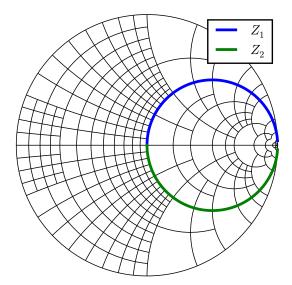

| 2.3  | Load modulation for simple outphasing operation with $R_L$ set to $100 \Omega$                          | 18 |

| 2.4  | Load modulation for simple outphasing operation with $R_L$ set to 100 $\Omega$ , demonstrating          |    |

|      | conjugate reactive loading. Smith chart normalized to $50 \Omega$ .                                     | 18 |

| 2.5  | Equivalent shunt circuits demonstrating load modulation presented to (a) $V_1$ , with an inductive      |    |

|      | shunt susceptance, and (b) $V_2$ , with an capacitive shunt susceptance                                 | 19 |

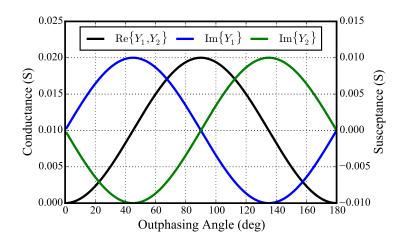

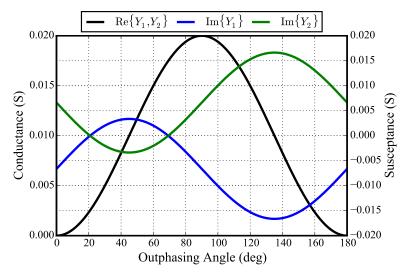

| 2.6  | Load modulation in terms of admittance for simple outphasing operation with $R_L$ set to 100 $\Omega$ . | 20 |

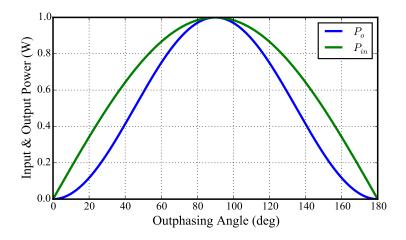

| 2.7  | Input and output power as a function of outphasing angle, demonstrating the system effect               |    |

|      | of load modulation in simple outphasing                                                                 | 21 |

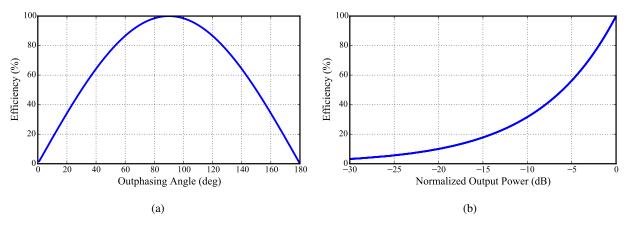

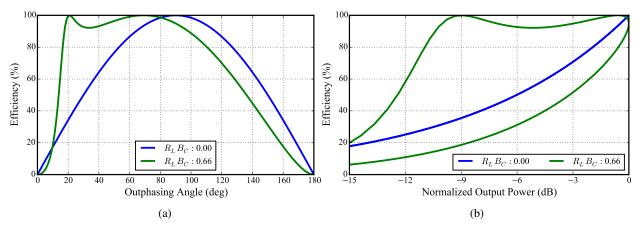

| 2.8  | Efficiency of simple outphasing as a function of (a) outphasing angle, and (b) normalized               |    |

|      | output power.                                                                                           | 21 |

| 2.9  | Equivalent shunt circuits with (a) capacitive and (b) inductive compensation, canceling the             |    |

|      | reactive part of the load at a single output power in addition to peak output power                     | 22 |

| 2.10 | Compensated load modulation under outphasing operation with $R_L$ set to $100 \Omega$ for $R_L B_C$     |    |

|      | = 0.66                                                                                                  | 24 |

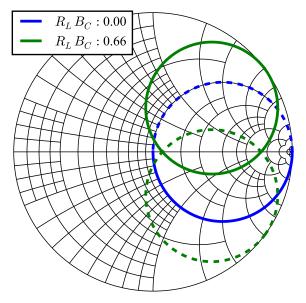

| 2.11 | Load modulation comparison with $R_L$ set to $100 \Omega$ for $R_L B_C = 0, 0.66$ . Dashed and solid     |    |

|------|----------------------------------------------------------------------------------------------------------|----|

|      | lines are the loading presented to $V_1$ and $V_2$ respectively. Smith chart normalized to 50 $\Omega$ . | 24 |

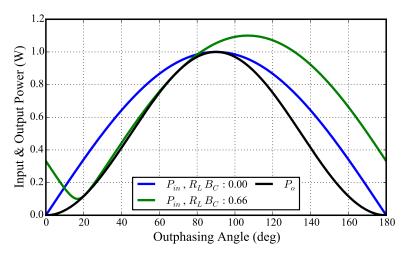

| 2.12 | Input and output power as a function of outphasing angle for $R_L B_C = 0$ and 0.66. Asym-               |    |

|      | metry has been introduced to the input power of the compensated circuit due to its loading               |    |

|      | conditions, moving it closer to the output power, and therefore improving efficiency                     | 25 |

| 2.13 | Efficiency as a function of (a) outphasing angle, and (b) normalized output power for $R_L B_C$          |    |

|      | = 0 and 0.66, demonstrating significant improvement with compensation. $\dots \dots \dots$               | 25 |

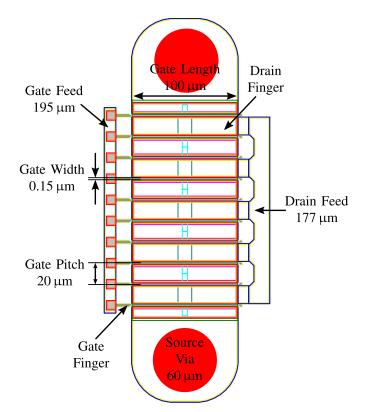

| 2.14 | Layout of a pHEMT from Qorvo's 0.15 $\mu$ m GaN process                                                  | 27 |

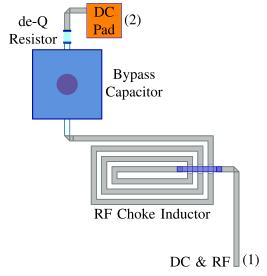

| 2.15 | Layout of gate bias tee.                                                                                 | 30 |

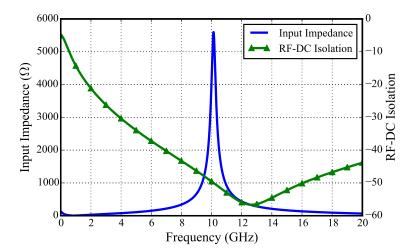

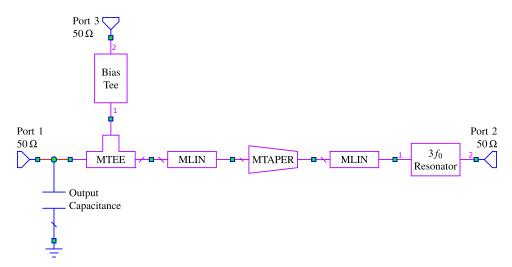

| 2.16 | Simulation of gate bias tee, demonstrating high input impedance and isolation                            | 30 |

| 2.17 | Layout of input matching network.                                                                        | 31 |

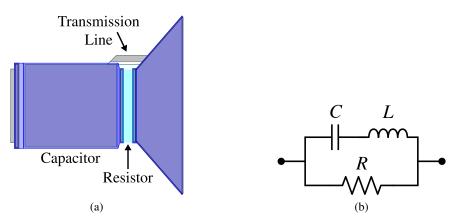

| 2.18 | (a) Layout and (b) equivalent circuit for stability circuit at the input of the transistor               | 32 |

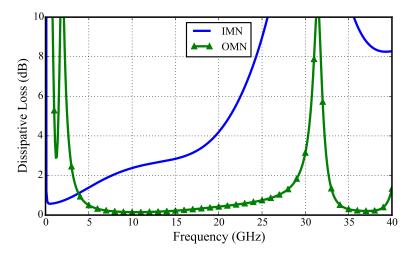

| 2.19 | Simulated dissipative loss in the input and output matching networks.                                    | 32 |

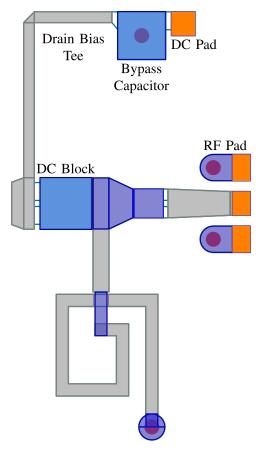

| 2.20 | Layout of output matching network.                                                                       | 33 |

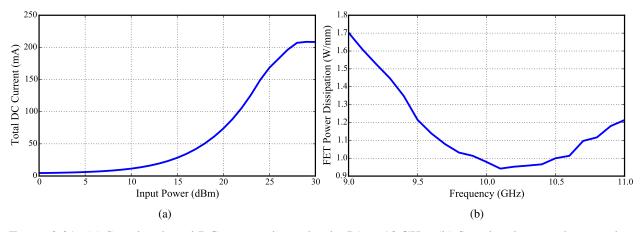

| 2.21 | (a) Simulated total DC current drawn by the PA at 10 GHz. (b) Simulated power dissipated                 |    |

|      | in the transistor under saturation.                                                                      | 34 |

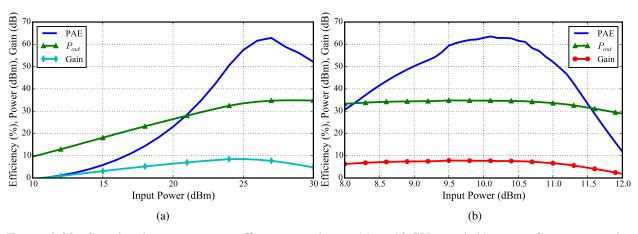

| 2.22 | Simulated output power, efficiency, and gain (a) at 10 GHz, and (b) across frequency under               |    |

|      | saturation.                                                                                              | 35 |

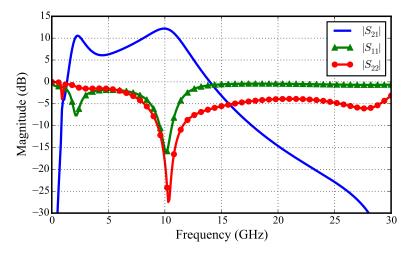

| 2.23 | Simulated power amplifier S-parameters across frequency.                                                 | 35 |

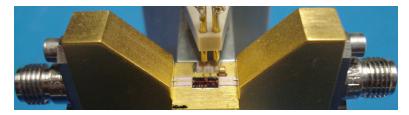

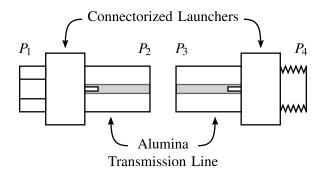

| 2.24 | Photograph of fixtured MMIC PA.                                                                          | 36 |

| 2.25 | Load-pull measurement setup utilizing a LSNA and single frequency mechanical tuner                       | 36 |

| 2.26 | Test fixture with connectorized launchers landing on alumina transmission lines which are                |    |

|      | bonded to the MMIC, placed in between ports 2 and 3. Two-port S-parameters of each side                  |    |

|      | of the fixture are measured using the TRL calibration method, which designates these two                 |    |

|      | networks as the error boxes for calibration                                                              | 38 |

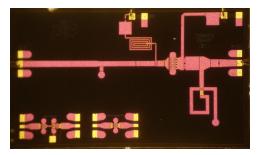

| 2.27 | Photograph of MMIC PA, which is $3.8 \times 2.3 \text{ mm}^2$ . Test devices fill the empty space        | 40 |

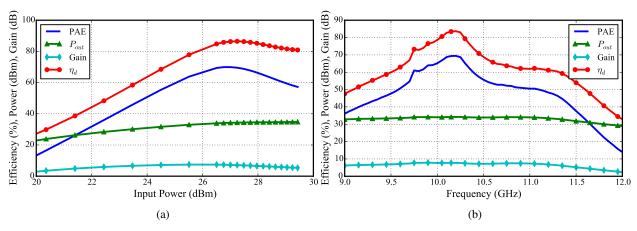

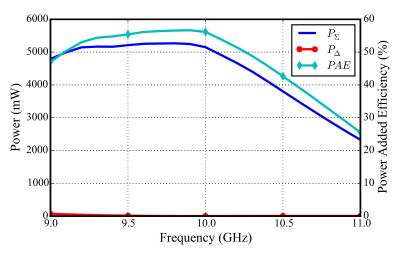

| 2.28 | Measured output power, efficiency, and gain (a) at 10.2 GHz, and (b) across frequency under            |    |

|------|--------------------------------------------------------------------------------------------------------|----|

|      | saturation                                                                                             | 40 |

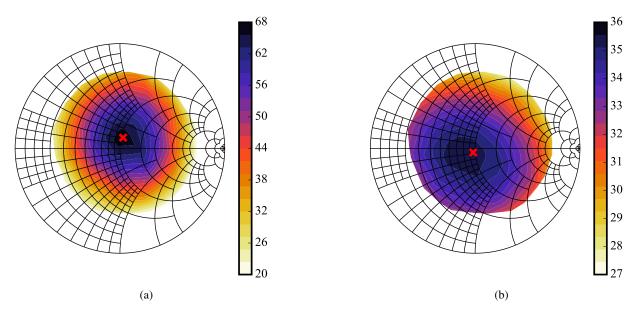

| 2.29 | Measured load-pull contours for (a) PAE, and (b) output power                                          | 40 |

| 2.30 | Detail of PA-combiner assembly. All internal measurements are de-embedded to the MMIC                  |    |

|      | bond wire reference plane. The microstrip circuit is designed to provide load modulation               | 42 |

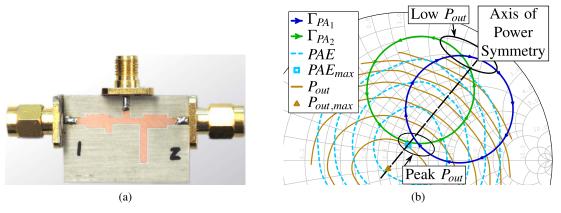

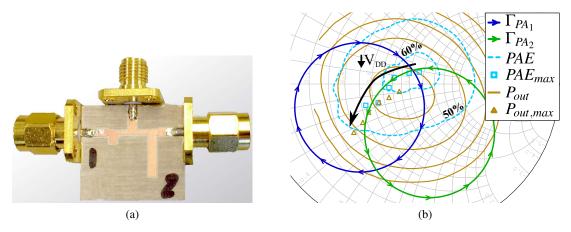

| 2.31 | (a) Photograph of Chireix combiner fabricated on 30 mil Ro4350B substrate. (b) $P_{out}$ and           |    |

|      | PAE load-pull contours measured at 10.1 GHz, with the axis of power symmetry shown for                 |    |

|      | design, and load modulation predicted by (2.66), (2.67). PAE contours are shown from $30\%$            |    |

|      | to 60% in 10 point increments and $P_{out}$ contours are traced from 28 to 35 dBm in 1 dB steps.       |    |

|      | Smith chart is normalized to $50 \Omega$ .                                                             | 43 |

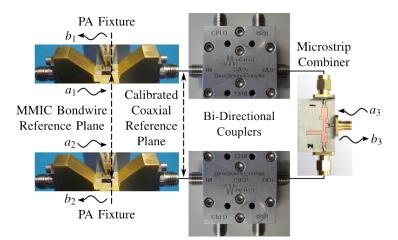

| 2.32 | (a) Photo and (b) diagram of the measurement setup, based on a 4-port LSNA. The two output             |    |

|      | couplers are included in the combiner, enabling measurement of internal load modulation and            |    |

|      | internal PA performance. A phase shifter sweeps the differential phase ( $\varphi$ ), while the source |    |

|      | for that branch varies amplitude to maintain a balanced input power level which saturates              |    |

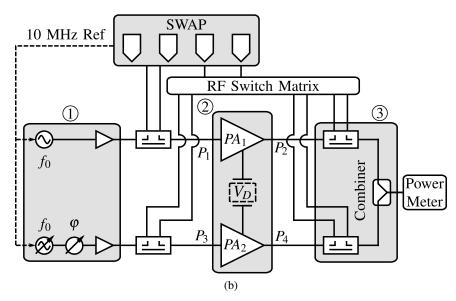

|      | both PAs                                                                                               | 45 |

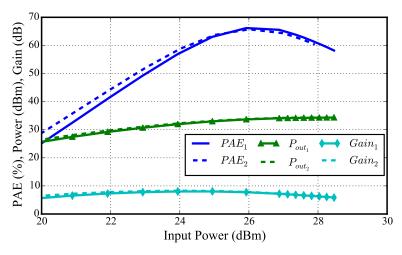

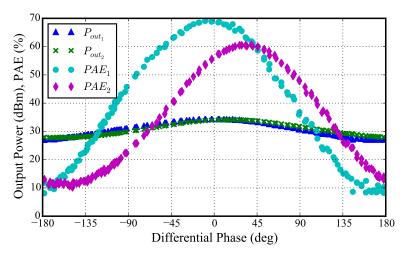

| 2.33 | Performance comparison of the two internal MMIC PAs at 10.1 GHz, -4.2 V gate bias, and                 |    |

|      | 20 V drain supply.                                                                                     | 46 |

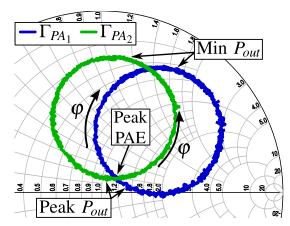

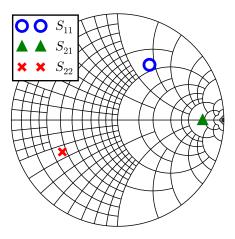

| 2.34 | Measurement of load modulation presented to internal PAs (MMIC bond wire plane) when                   |    |

|      | loaded with the non-isolated combiner from Fig. 2.31a.                                                 | 47 |

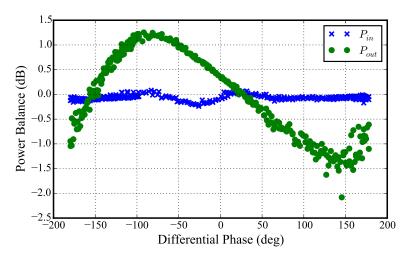

| 2.35 | Measured power balance at the input and output of the internal MMIC PAs                                | 47 |

| 2.36 | Measured internal PA output powers and efficiencies at 10.1 GHz with 26.5 dB input power               |    |

|      | and 20 V supply.                                                                                       | 48 |

| 2.37 | Measured system output power and efficiency.                                                           | 48 |

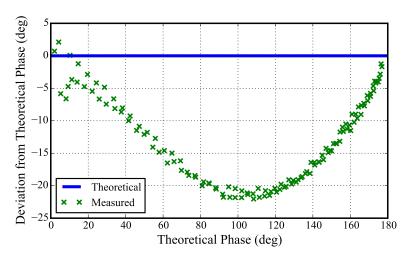

| 2.38 | Measured system efficiency as a function of normalized output power.                                   | 49 |

| 2.39 | Measured differential phase deviation, showing up to $25^\circ$ deviation from ideal operation         | 51 |

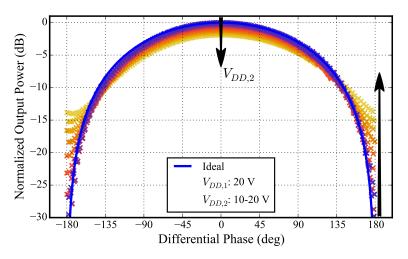

| 2.40 | Measured output power with respect to differential phase, showing up to 2.7 dB deviation               |    |

|      | from ideal operation.                                                                                  | 51 |

| 3.1  | Block diagram of LINC power amplifier architecture.                                                  | 54 |

|------|------------------------------------------------------------------------------------------------------|----|

| 3.2  | LINC vector diagram of input voltages as defined in Fig. 3.1                                         | 55 |

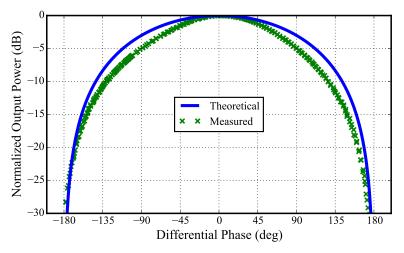

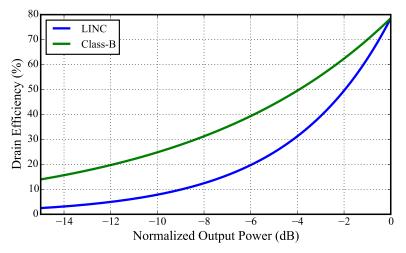

| 3.3  | Theoretical efficiency of the LINC PA with the internal PA efficiencies set to 100%                  | 58 |

| 3.4  | Comparison between the theoretical efficiencies of a LINC PA with optimum class-B internal           |    |

|      | amplifiers operating and a single-ended class-B PA                                                   | 58 |

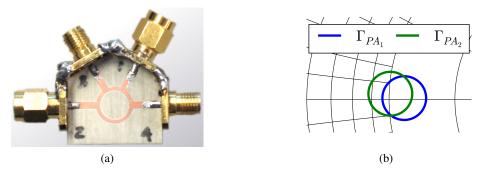

| 3.5  | (a) Photograph of rat-race combiner fabricated on 30 mil Rogers 4350B substrate for operation        |    |

|      | centered at 10.1 GHz. (b) Load modulation predicted by (2.66), (2.67) utilizing measured             |    |

|      | rat-race S-parameters. The Smith chart is normalized to 50 $\Omega$ and shown for 0.6 < $r_L$ < 1.4. | 59 |

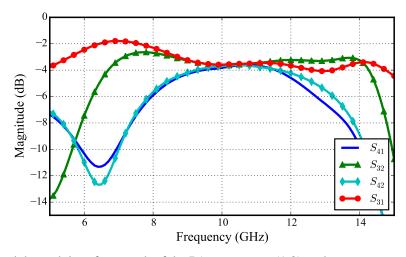

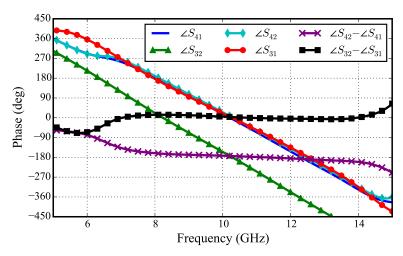

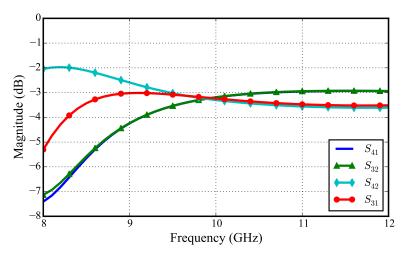

| 3.6  | Measured through loss from each of the PA input ports $(1,2)$ to the output port $(3)$ and the       |    |

|      | isolated port (4)                                                                                    | 60 |

| 3.7  | Measured phase between the input and output ports, and the difference between those paths.           | 60 |

| 3.8  | Measured input match and isolation between inputs                                                    | 60 |

| 3.9  | Measurement of load modulation presented to internal PAs (MMIC bond wire plane) when                 |    |

|      | loaded with the isolated combiner from Fig. 3.5a.                                                    | 61 |

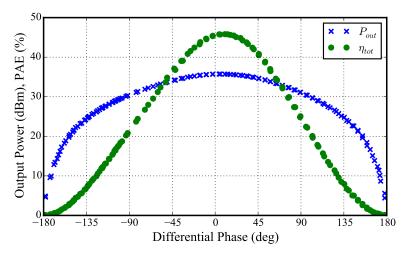

| 3.10 | Measured internal PA output powers and efficiencies at 10.1 GHz with 26.5 dB input power             |    |

|      | and 20 V supply                                                                                      | 62 |

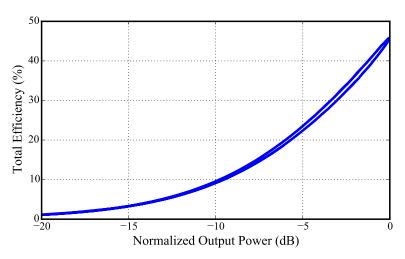

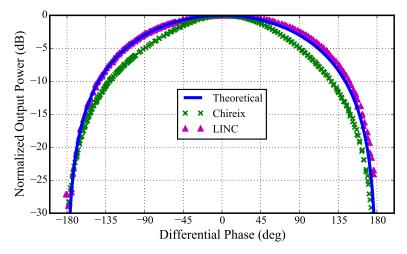

| 3.11 | Measured system output power and efficiency.                                                         | 62 |

| 3.12 | Comparison of measured system efficiency as a function of normalized output power, demon-            |    |

|      | strating the improvement of Chireix outphasing.                                                      | 63 |

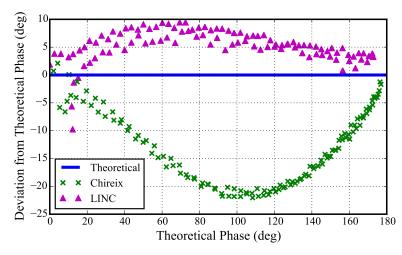

| 3.13 | Comparison of measured differential phase deviation, showing only up to $8^\circ$ deviation from     |    |

|      | ideal operation for the LINC PA.                                                                     | 64 |

| 3.14 | Comparison of measured output power with respect to differential phase, showing negligible           |    |

|      | deviation for the LINC PA.                                                                           | 65 |

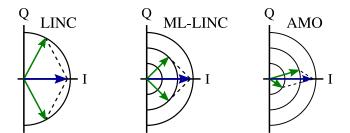

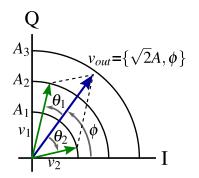

| 4.1  | LINC, ML-LINC, and AMO vector diagram.                                                               | 67 |

| 4.2  | Theoretical efficiency of the ideal, four level ML-LINC PA, demonstrating improvement for            |    |

|      | the optimal trajectory.                                                                              | 68 |

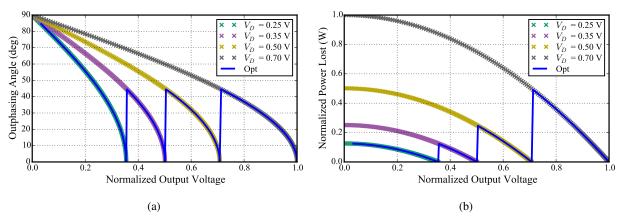

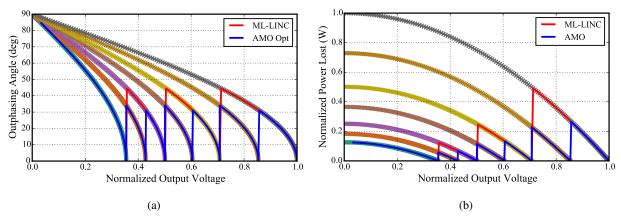

| 4.3  | (a) Theoretical outphasing angle for the ideal, four level ML-LINC PA, demonstrating a                             |    |

|------|--------------------------------------------------------------------------------------------------------------------|----|

|      | decrease for the optimal trajectory. (b) Theoretical RF power dissipated in the isolated                           |    |

|      | combiner, with decreases corresponding to those in the outphasing angle                                            | 69 |

| 4.4  | Detailed AMO vector diagram.                                                                                       | 70 |

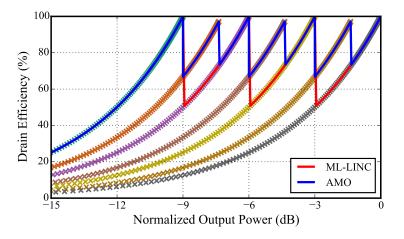

| 4.5  | Theoretical efficiency of the ideal, four level AMO PA, demonstrating improvement for the                          |    |

|      | optimal trajectory beyond that of ML-LINC                                                                          | 72 |

| 4.6  | (a) Theoretical outphasing angle for the ideal, four level AMO PA, demonstrating a decrease                        |    |

|      | for the optimal trajectory. (b) Theoretical RF power dissipated in the isolated combiner, with                     |    |

|      | decreases corresponding to those in the outphasing angle. In both cases, greater reduction is                      |    |

|      | achieved by AMO than ML-LINC.                                                                                      | 73 |

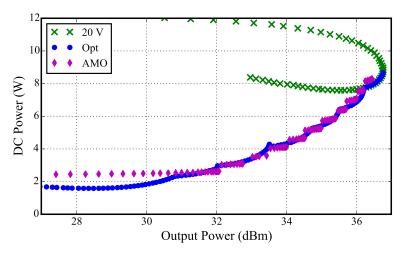

| 4.7  | Measured system total efficiency of the ML-LINC PA for swept differential phase at drain                           |    |

|      | voltages of 10, 12, 14, 16, 18, and 20 V demonstrating advantageous new peaks                                      | 74 |

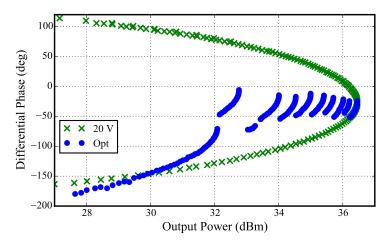

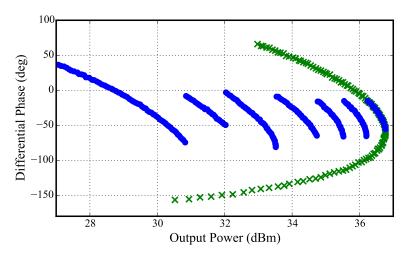

| 4.8  | Comparison of measured differential phase between constant 20 V and optimal ML-LINC                                |    |

|      | operation, demonstrating a reduction for ML-LINC.                                                                  | 75 |

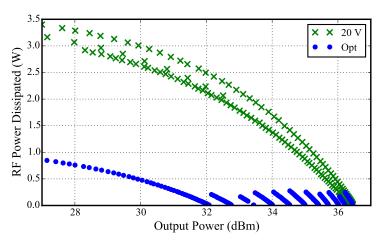

| 4.9  | Comparison of measured RF power dissipated in the isolated combiner between constant                               |    |

|      | $20\mathrm{V}$ and optimal ML-LINC operation, which remains below $0.92\mathrm{W}$ up to $6.5\mathrm{dB}$ back-off |    |

|      | for ML-LINC.                                                                                                       | 75 |

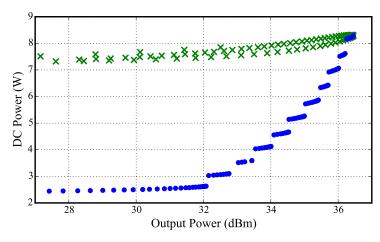

| 4.10 | Comparison of measured DC power consumption between constant 20 V and optimal ML-                                  |    |

|      | LINC operation, demonstrating power savings of up to 6.6 W by ML-LINC                                              | 75 |

| 4.11 | Measured system total efficiency of the AMO PA for swept differential phase at drain voltages                      |    |

|      | of 10, 12, 14, 16, 18, and 20 V and combinations of adjacent levels, demonstrating nearly                          |    |

|      | twice as many peaks as ML-LINC.                                                                                    | 76 |

| 4.12 | Comparison of measured differential phase between constant 20 V and optimal AMO oper-                              |    |

|      | ation, demonstrating a reduction for AMO                                                                           | 77 |

| 4.13 | Comparison of measured DC power consumption between constant 20 V and optimal AMO                                  |    |

|      | operation, demonstrating power savings of up to 4.9 W by AMO                                                       | 77 |

| 4.14 | Comparison of measured RF power dissipated in the isolated combiner between constant                               |    |

|------|--------------------------------------------------------------------------------------------------------------------|----|

|      | $20\mathrm{V}$ and optimal AMO operation, which remains below $0.48\mathrm{W}$ up to $6.5\mathrm{dB}$ back-off for |    |

|      | AMO                                                                                                                | 77 |

| 4.15 | Measured (a) load modulation, and (b) internal PA and system PAE for the AMO PA                                    |    |

|      | with varying separation between supply levels $[V_{D_1}, V_{D_2}]$ . Large supply separation shows                 |    |

|      | significant load modulation, causing both internal PA and system efficiency degradation                            | 78 |

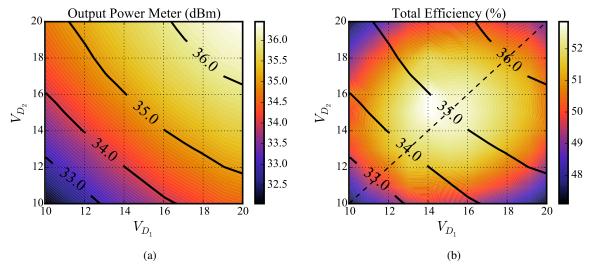

| 4.16 | (a) Output power and (b) total efficiency for all combinations of drain voltages from 10 V to                      |    |

|      | 20  V in 1 V steps with the dashed black line demonstrating supply level symmetry. For each                        |    |

|      | output power, symmetric supplies maximizes efficiency.                                                             | 79 |

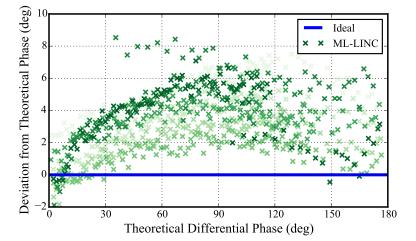

| 4.17 | Measured differential phase deviation in ML-LINC, showing up to $8^{\circ}$ deviation from ideal                   |    |

|      | operation                                                                                                          | 80 |

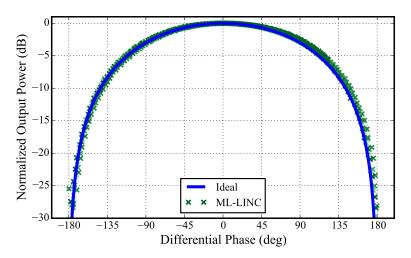

| 4.18 | Measured output power with respect to differential phase in ML-LINC, showing negligible                            |    |

|      | deviation.                                                                                                         | 80 |

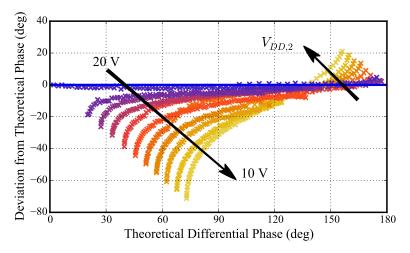

| 4.19 | Measured differential phase deviation for the AMO PA. $V_{D_1}$ is 20 V, and $V_{D_2}$ is varied from              |    |

|      | 10V to $20V$ in $1V$ steps. The phase deviation increases substantially with the difference                        |    |

|      | between supply levels                                                                                              | 81 |

| 4.20 | Measured output power with respect to differential phase for the AMO PA. $V_{D_1}$ is 20 V,                        |    |

|      | and $V_{D_2}$ is varied from 10 V to 20 V in 1 V steps. As the supply level difference increases,                  |    |

|      | significant output power distortion occurs.                                                                        | 81 |

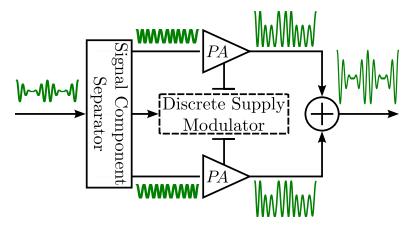

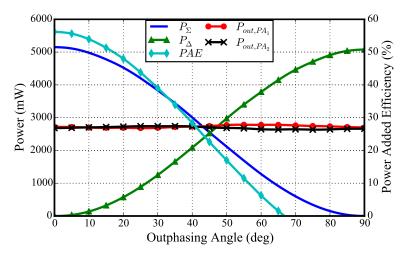

| 5.1  | Block diagram of multi-level Chireix outphasing.                                                                   | 84 |

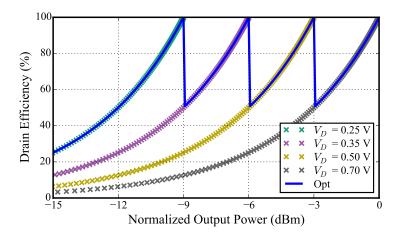

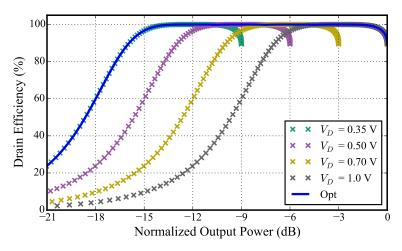

| 5.2  | Theoretical efficiency of the ideal, four level ML-CO PA, demonstrating improvement for                            |    |

|      | the optimal trajectory. The normalized supply levels of 0.355, 0.5, 0.708, and 1.0 V set the                       |    |

|      | maximum output powers at 9, 6, 3, and 0 dB back-off                                                                | 85 |

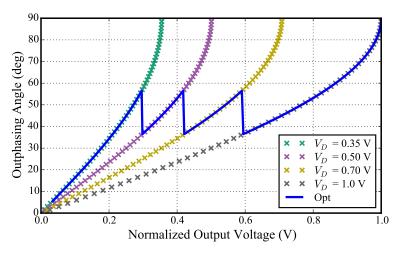

| 5.3  | Theoretical outphasing angle for the ideal, four level ML-CO PA. Normalized supply voltages                        |    |

|      | are 0.355, 0.5, 0.708, and 1.0 V                                                                                   | 86 |

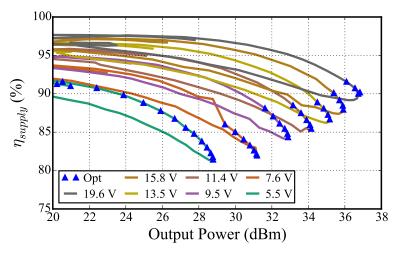

| 5.4  | (a) Photograph of Chireix combiner designed for ML-LINC measurements at 10.1 GHz and          |    |

|------|-----------------------------------------------------------------------------------------------|----|

|      | fabricated on 30 mil Ro4350B substrate. (b) Measured load-pull contours at drain voltages     |    |

|      | of 10, 12, 14, 16, 18, and 20 V. Output power contours are traced from 29 to 34 dBm (with     |    |

|      | 1 dB step) for a 20 V supply to aid output power balancing. PAE contours for all voltages     |    |

|      | are combined into regions designating PAE $>$ 50% and 60%, showing expansion of high          |    |

|      | efficiency impedances. The predicted load modulation follows the movement of the PAE and      |    |

|      | output power maxima with drain voltage. Smith chart is normalized to $50\Omega$               | 87 |

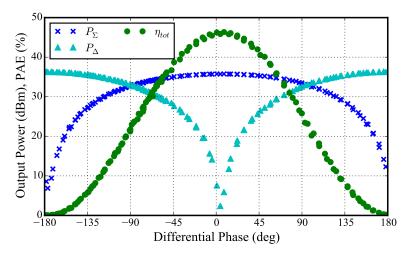

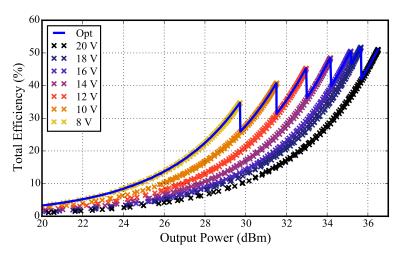

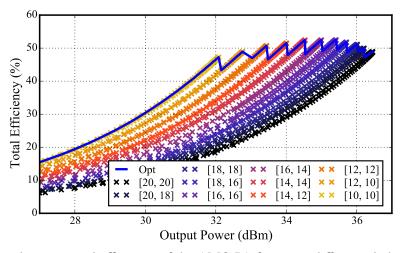

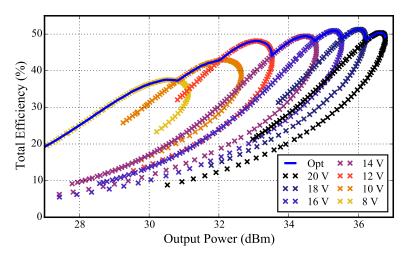

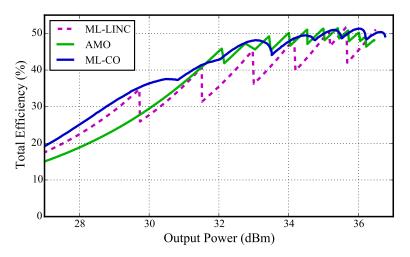

| 5.5  | Measured system total efficiency of ML-CO PA for swept differential phase for drain voltages  |    |

|      | from 8 to 20 V in 2 V steps. Optimal operation, selected for peak total efficiency at each    |    |

|      | output power, takes advantage of load modulation hysteresis to maintain high efficiency       | 88 |

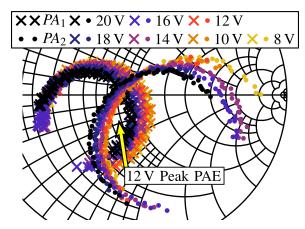

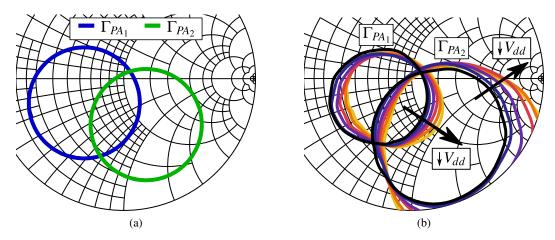

| 5.6  | Measured internal load modulation in the ML-CO PA. Imbalance in impedance loci radii          |    |

|      | exposes the difficulty in maintaining internal PA $P_{out}$ balance, but is mitigated through |    |

|      | reduced differential phase requirements and balanced supply levels                            | 89 |

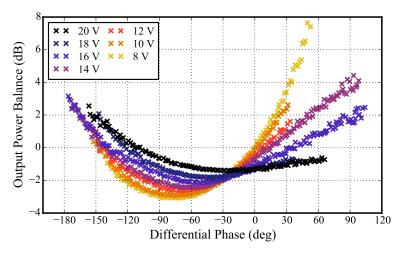

| 5.7  | Measured power imbalance at the output of the internal PAs, demonstrating a the effects of    |    |

|      | imbalanced loading conditions which worsen with reduced supply voltage                        | 89 |

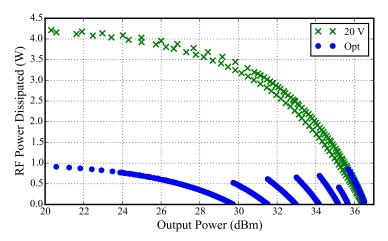

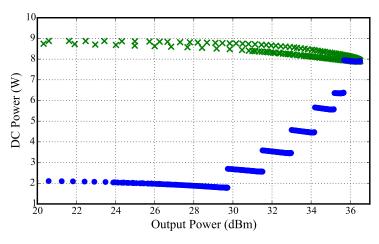

| 5.8  | Comparison of measured DC power consumption between constant 20 V, optimal AMO, and           |    |

|      | optimal ML-CO operation, demonstrating commensurate power savings between ML-CO               |    |

|      | and AMO                                                                                       | 90 |

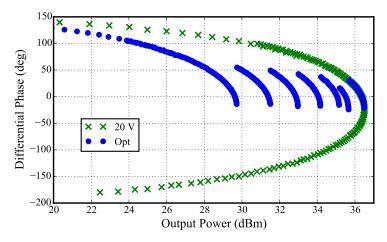

| 5.9  | Comparison of measured differential phase between constant 20 V and optimal ML-CO             |    |

|      | operation, demonstrating a significant reduction. The optimal trajectory utilizes supply      |    |

|      | voltages from 8 V to 20 V in 2 V steps.                                                       | 91 |

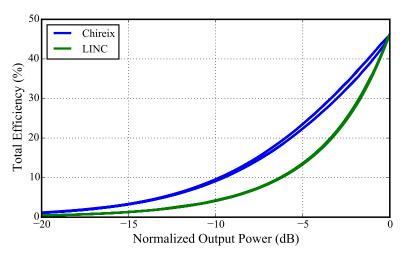

| 5.10 | ) Comparison of efficiency for optimal ML-LINC, AMO, and ML-CO operation.                     | 91 |

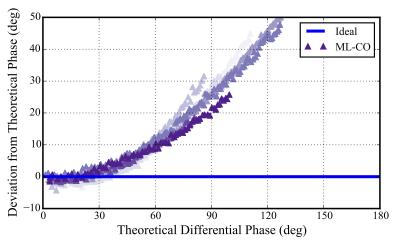

| 5.11 | Measured differential phase deviation in ML-CO, showing up to 50° deviation from ideal        |    |

|      | operation. The shades of purple designate the supply voltage, the lightest and darkest        |    |

|      | corresponding to 10 V and 20 V, respectively.                                                 | 92 |

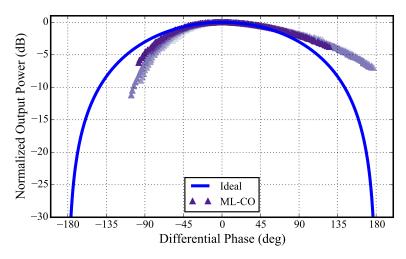

| 5.12 | 2 Measured output power with respect to differential phase in ML-CO, showing up to 7.5 dB     |    |

|      | deviation from ideal operation.                                                               | 93 |

| 5.13 | (a) Simulation predicting the load modulation of a measured combiner based on (2.66) and                         |

|------|------------------------------------------------------------------------------------------------------------------|

|      | (2.67) with $x=1$ and internal PAs are biased at 20 V. (b) Simulated predicted load modulation                   |

|      | using feedback to account for internal PA output power imbalance at supply levels between                        |

|      | 10 V and 20 V in 2 V steps                                                                                       |

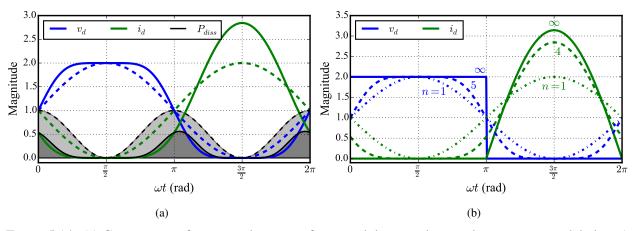

| 5.14 | (a) Comparison of intrinsic drain waveforms and dissipated power between sinusoidal class-                       |

|      | A operation (dashed, light gray) and class-F with five harmonic terminations (solid, dark                        |

|      | gray). (b) Evolution of intrinsic drain voltage and current waveforms for increasing number                      |

|      | of class-F terminated harmonics                                                                                  |

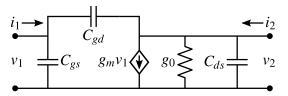

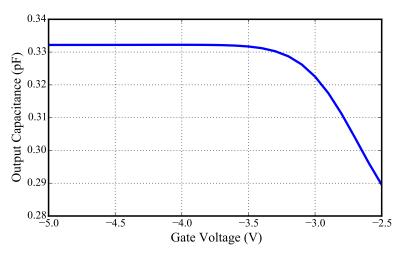

| 5.15 | Simplified small signal model for capacitance extraction using Y-parameter analysis 97                           |

| 5.16 | Extracted output capacitance of a $10 \times 100 \mu m$ pHEMT in Qorvo's 0.15 $\mu m$ GaN process as             |

|      | a function of bias voltage                                                                                       |

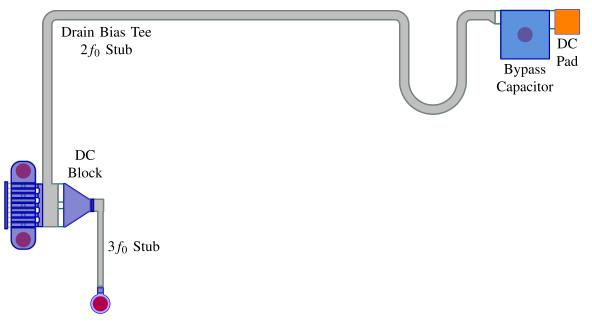

| 5.17 | Layout of second and third harmonic terminations at the output of the transistor 99                              |

| 5.18 | Simulation of gate bias tee, demonstrating high input impedance and isolation at $f_0$ , low                     |

|      | impedance at $2f_0$ , and high impedance at $3f_0$                                                               |

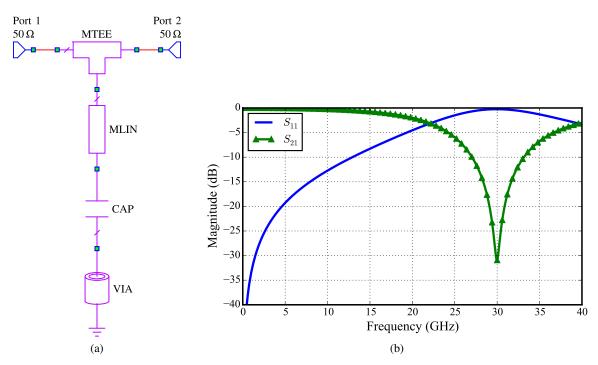

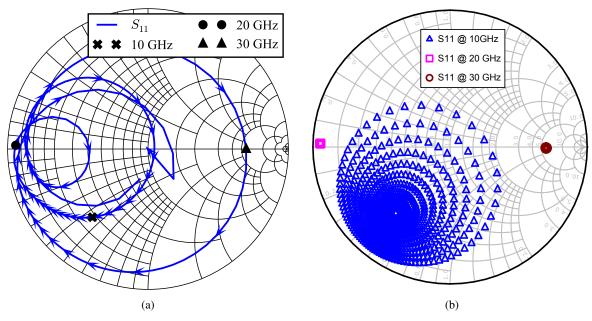

| 5.19 | (a) Schematic of simulated third harmonic termination circuit. (b) Simulated S-parameters                        |

|      | of third harmonic termination                                                                                    |

| 5.20 | Schematic of simulated second and third harmonic terminations at the intrinsic drain 101                         |

| 5.21 | (a) Simulated impedance presented to the transistor at the intrinsic drain. (b) Simulated tuning                 |

|      | range at harmonic frequencies, demonstrating tunability at the fundamental frequency, but                        |

|      | not at harmonics, which are terminated                                                                           |

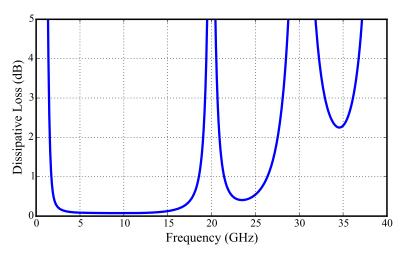

| 5.22 | Dissipative loss in the harmonic termination network with 50 $\Omega$ load. Fundamental frequency                |

|      | matching is not performed yet                                                                                    |

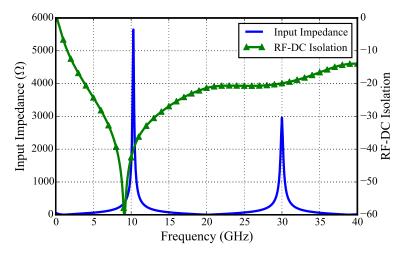

| 5.23 | Layout of input matching network                                                                                 |

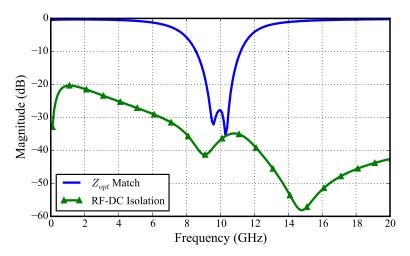

| 5.24 | Simulation of input matching network match and RF-DC isolation                                                   |

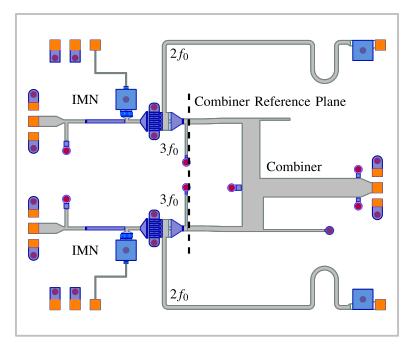

| 5.25 | Layout of full ML-CO MMIC PA, defining the combiner and its design reference plane 104                           |

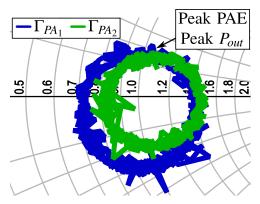

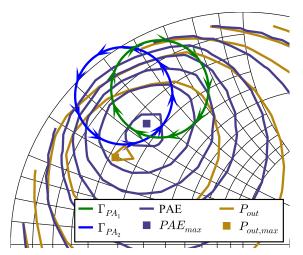

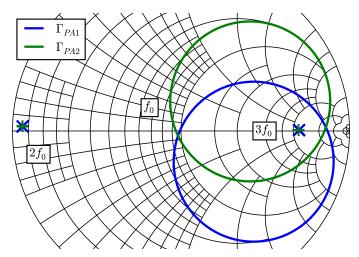

| 5.26 | Load modulation of each PA, $\Gamma_{PA_1}$ and $\Gamma_{PA_2}$ , overlaid on the PAE and output power load-pull |

|      | contours at the combiner reference plane. Smith chart is normalized to $50 \Omega$                               |

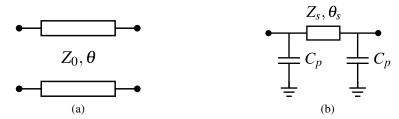

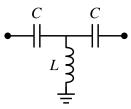

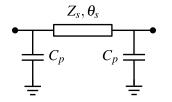

| 5.27 | (a) Ideal transmission line. (b) Ideal TL- $\pi$ equivalent network                                           |

|------|---------------------------------------------------------------------------------------------------------------|

| 5.28 | Simulated load modulation at the intrinsic drain of each PA during outphasing. The harmonic                   |

|      | terminations do not change with fundamental load modulation due to the high quality factor                    |

|      | of the resonators                                                                                             |

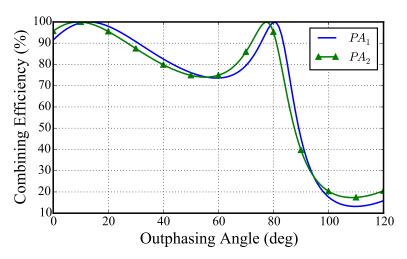

| 5.29 | Simulated combining efficiency of the microstrip combiner (referenced to the intrinsic drain)                 |

|      | is maintained above 70 % over 85° of outphasing range                                                         |

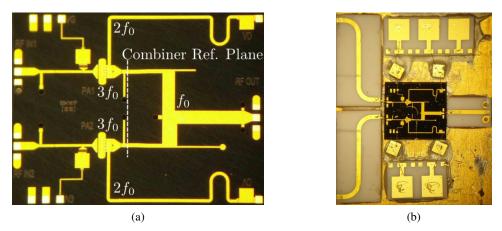

| 5.30 | Photographs of (a) ML-CO GaN MMIC PA, with a size of $3.8 \times 3.2 \text{ mm}^2$ , and (b) MMIC             |

|      | mounted in fixture as detailed in subsection 2.2.3                                                            |

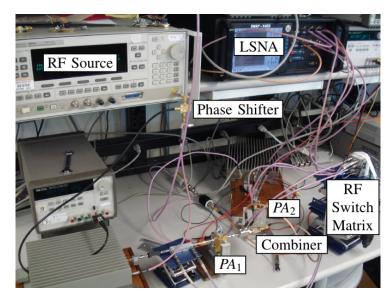

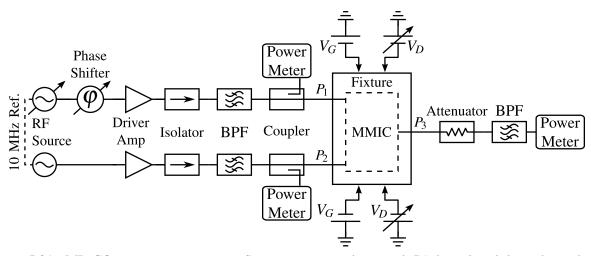

| 5.31 | ML-CO measurement setup. Separate sources drive each PA branch, while a phase shifter                         |

|      | sweeps the differential phase. The source driving the phase shifter adjusts its amplitude to                  |

|      | maintain constant available input power to within 0.1 dB                                                      |

| 5.32 | AWR schematic of de-embedding straight alumina line simulation from the measured fixture                      |

|      | input transition, before embedding the curved alumina line simulation                                         |

| 5.33 | (a) Circuit diagram of the power-DAC architecture. (b) Photograph of the fabricated GaN                       |

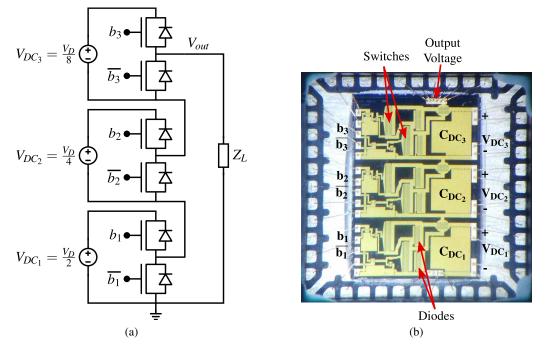

|      | implementation, with a size of $3.8 \times 5.4 \text{ mm}^2$ 112                                              |

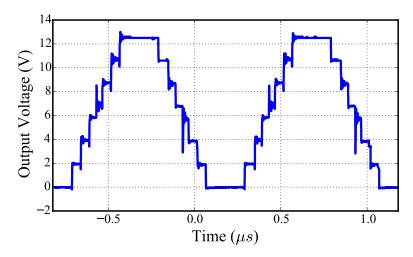

| 5.34 | GaN power-DAC MMIC output voltage approximate of 1 MHz sinusoid across a fixed resis-                         |

|      | tive load                                                                                                     |

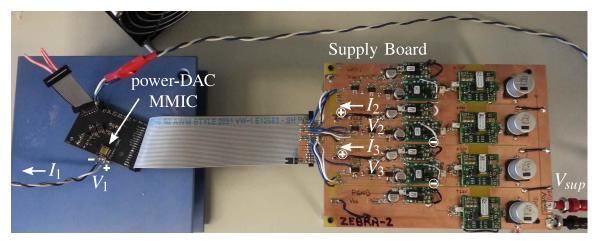

| 5.35 | Detail of power-DAC portion of overall measurement setup. Three isolated DC voltages are                      |

|      | produced by the supply board on the right, while the power-DAC board on the left interfaces                   |

|      | digital control signals and DC voltages with the MMIC, which is mounted in a QFN package. 114                 |

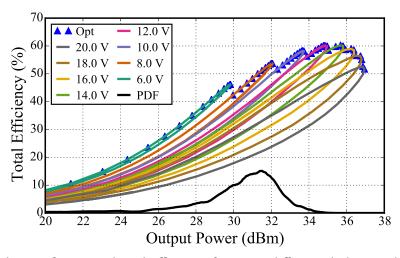

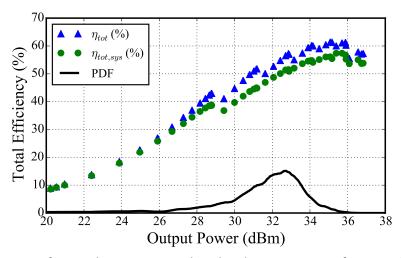

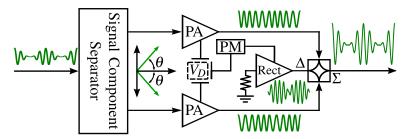

| 5.36 | Compilation of measured total efficiency for swept differential phase and supply levels from                  |

|      | 6 V to 20 V in 2 V increments at 9.7 GHz. The optimal trajectory is selected to maximize                      |

|      | $\eta_{tot}$ . In black is the PDF of a 6 dB PAPR QPSK signal used to calculate average total efficiency. 115 |

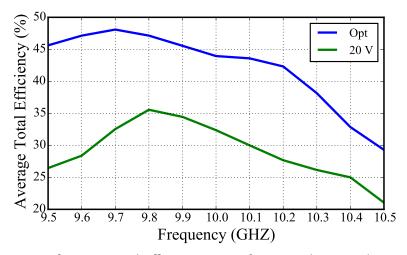

| 5.37 | Comparison of average total efficiency across frequency between the optimal trajectory and                    |

|      | 20  V supply, showing improvements between 8 and 19 points. Optimal operation achieves                        |

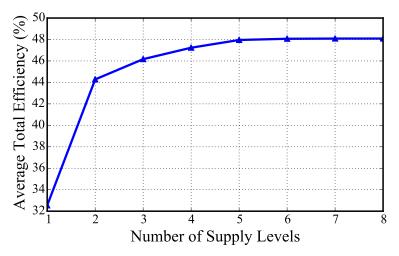

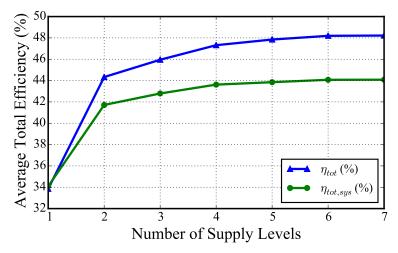

|      | 400 MHz of bandwdith with $\eta_{tot,avg}$ > 45%                                                              |

| 5.38 | Average total efficiency for a 6 dB PAR QPSK signal with restricted supply levels, showing                 |

|------|------------------------------------------------------------------------------------------------------------|

|      | diminishing returns for increasing number of levels                                                        |

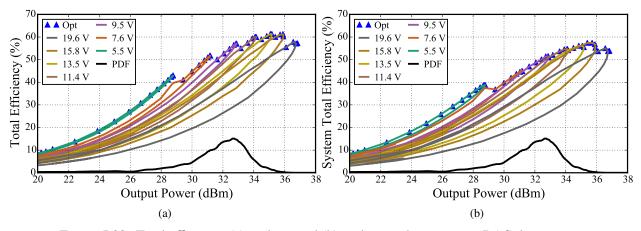

| 5.39 | Total efficiency (a) without and (b) with considering power-DAC dissipation                                |

| 5.40 | Comparison of optimal trajectories with and without accounting for power-DAC consumption.118               |

| 5.41 | Efficiency of the power-DAC, showing the operating points of the optimal trajectory 119                    |

| 5.42 | Comparison of the average total efficiency for a 6 dB PAR QPSK signal with restricted supply               |

|      | levels, with and without considering the power-DAC efficiency                                              |

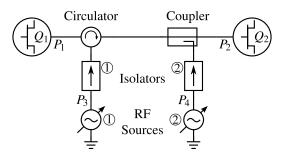

| 6.1  | Block diagram of a LINC PA with power recycling                                                            |

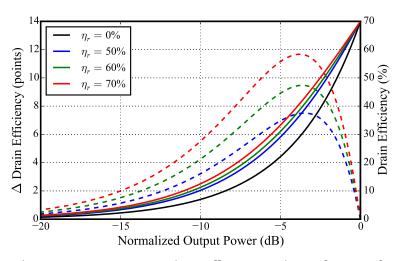

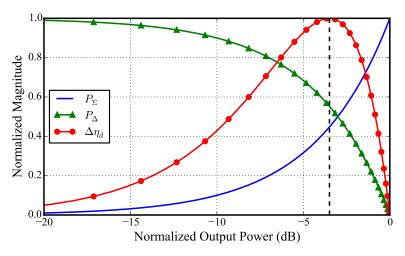

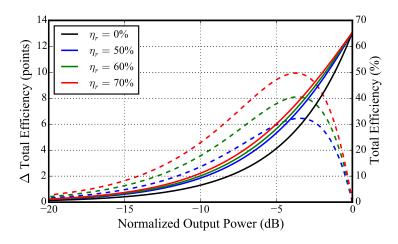

| 6.2  | Theoretical improvement in system drain efficiency with rectification of power on the isolated             |

|      | port. The internal PAs are assumed to be 70% efficiency ( $\eta_{d,PA} = 70\%$ ), while the rectifier      |

|      | efficiency is set to 50%, 60%, and 70%                                                                     |

| 6.3  | Theoretical improvement in system drain efficiency with rectification of power on the isolated             |

|      | port. $\eta_{d,PA} = 70\%$ , and $\eta_r$ is set to 50%, 60%, and 70%                                      |

| 6.4  | Theoretical improvement in system total efficiency with rectification of power on the isolated             |

|      | port. $\eta_{d,PA} = 70\%$ , and $\eta_r$ is set to 50%, 60%, and 70%                                      |

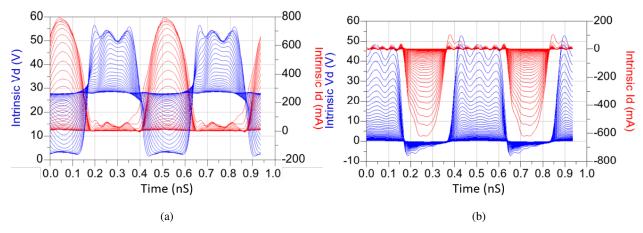

| 6.5  | Simulated time-domain intrinsic drain voltage (blue) and current (red) waveforms for varying               |

|      | RF power at drain for (a) PA and (b) rectifier operation. For PA operation, $V_{DS} = 28$ V 127            |

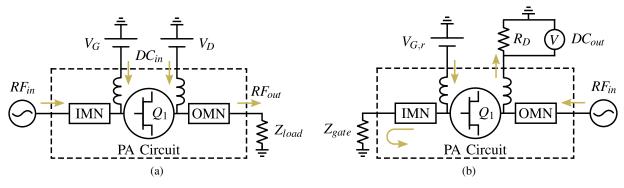

| 6.6  | PA circuit operating as (a) power amplifier and (b) rectifier                                              |

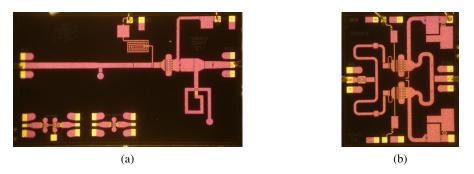

| 6.7  | X-Band MMIC power amplifiers tested as rectifiers. (a) Circuit-A: single-stage PA, at a                    |

|      | size of $3.8 \times 2.3 \text{ mm}^2$ . (b) Circuit-B: single-stage power combined PA, with a footprint of |

|      | $2.0 \times 2.3 \text{ mm}^2$                                                                              |

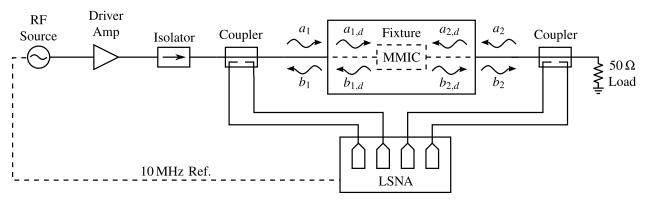

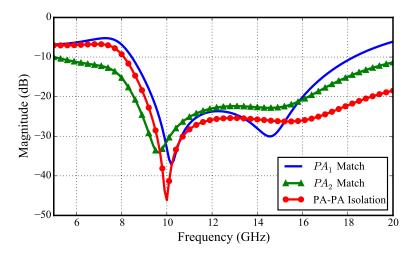

| 6.8  | Power amplifier measurement setup, utilizing an LSNA. Measurement reference planes are                     |

|      | de-embedded to the MMIC bond wire within the test-fixture                                                  |

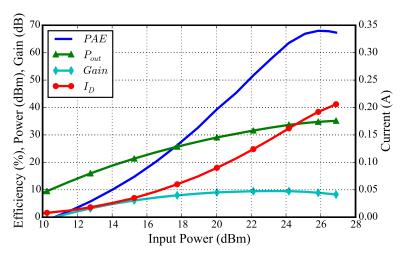

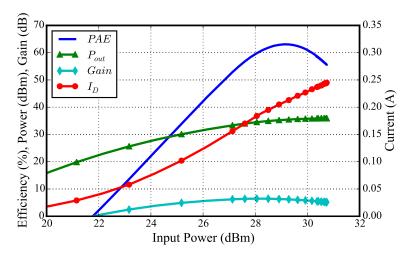

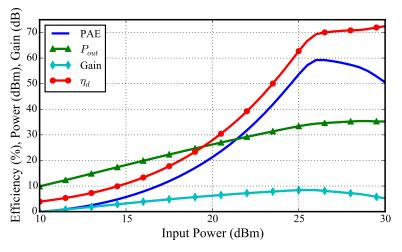

| 6.9  | Circuit-A power swept amplifier measurement at 10.1 GHz with $V_G = -4.0$ V and $V_D = 20$ V,              |

|      | demonstrating a peak PAE of $68.0\%$ at an output power of $34.8dBm$ and $192mA$ of DC                     |

|      | drain current drawn                                                                                        |

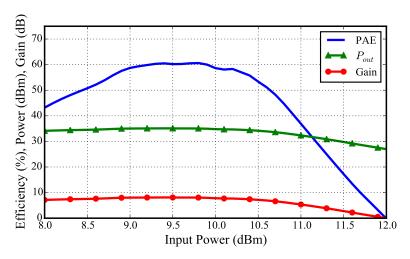

| 6.10 Circuit-B power swept amplifier measurement at 10.1 GHz with $V_G = -4.0$ V and $V_D = 20$ V,            |

|---------------------------------------------------------------------------------------------------------------|

| demonstrating a peak PAE of 63.1% at an output power of 35.4 dBm and 225 mA of DC                             |

| drain current drawn                                                                                           |

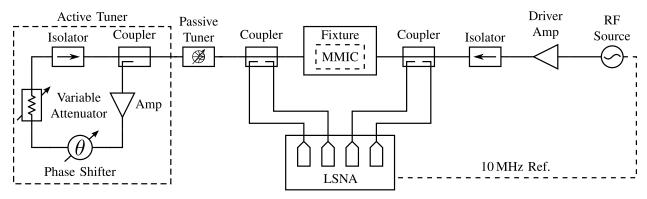

| 6.11 Rectifier measurement setup, utilizing LSNA and active tuning on the RF gate. The active                 |

| tuning loop is used to overcome the losses in the passive tuner and extend the reflection                     |

| coefficient magnitude achievable. When using active tuning, the passive tuner is set to                       |

| appear as a 50 $\Omega$ transmission line                                                                     |

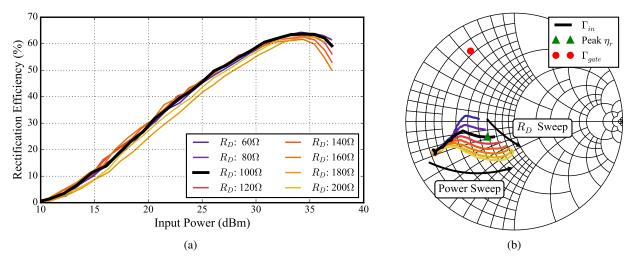

| 6.12 Circuit-A (a) rectification efficiency and (b) input impedance as a function of input power              |

| and DC drain load. An insignificant 2.7 point fluctuation occurs in the efficiency with load                  |

| variation, while the input impedance shows more significant variation                                         |

| 6.13 Circuit-B (a) rectification efficiency and (b) input impedance as a function of input power              |

| and DC drain load. The efficiency ranges by only 2.6 points with variations in the load, while                |

| the input impedance shows more significant variation                                                          |

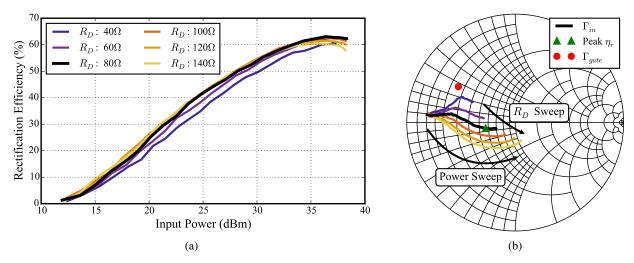

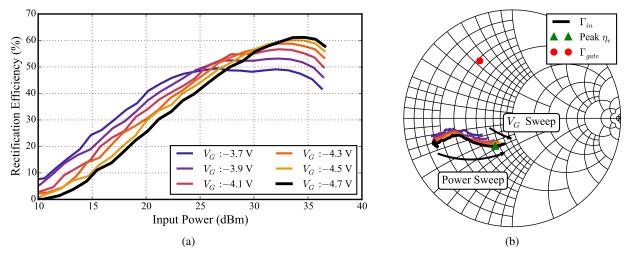

| 6.14 Circuit-A (a) rectification efficiency and (b) input impedance of the rectifier under gate bias          |

| voltage and input power sweeps. The gate bias voltage is swept from -3.7 V to -4.7 V in 0.2 V                 |

| increments. Deep pinch-off improves the efficiency by 12 points, but has little effect on the                 |

| input impedance                                                                                               |

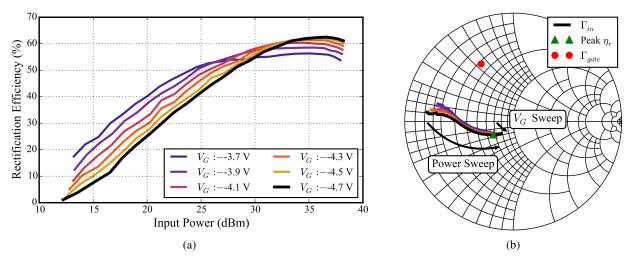

| 6.15 Circuit-B (a) rectification efficiency and (b) input impedance of the rectifier under gate bias          |

| voltage and input power sweeps. The gate bias voltage is swept from -3.7 V to -4.7 V in 0.2 V                 |

| increments. Deep pinch-off improves the efficiency by 6.2 points, but has little effect on the                |

| input impedance                                                                                               |

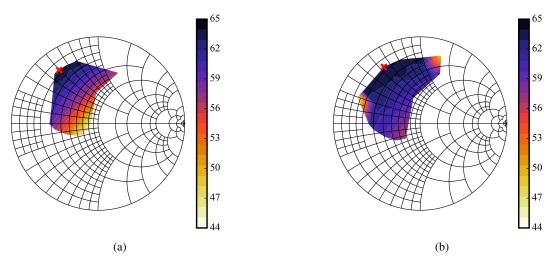

| 6.16 Gate termination load-pull contours combining passive tuner and active loop data for (a)                 |

| circuit-A, and (b) circuit-B                                                                                  |

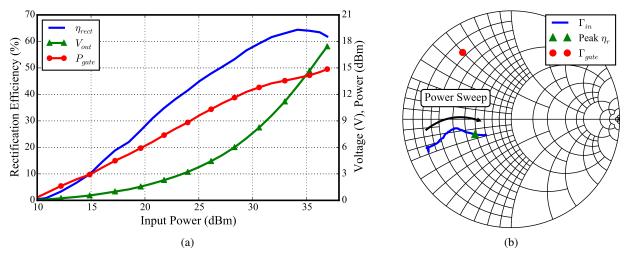

| 6.17 Optimal circuit-A (a) rectification performance and (b) input impedance for swept input power            |

| at 10.1 GHz with $V_G = -4.7$ V, $R_D = 100 \Omega$ , and $Z_{gate} = 8.47 + j24.88 \Omega$ , demonstrating a |

| peak efficiency of 64.4%                                                                                      |

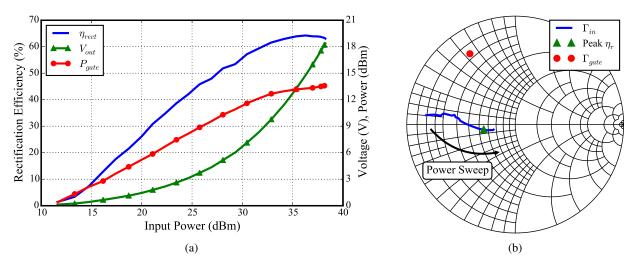

| 6.18                                                          | $Optimal \ circuit-B\ (a)\ rectification\ performance\ and\ (b)\ input\ impedance\ for\ swept\ input\ power$                                                                                                                         |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                               | at 10.1 GHz with $V_G = -4.7$ V, $R_D = 800 \Omega$ , and $Z_{gate} = 8.18 + j26.8 \Omega$ , demonstrating a                                                                                                                         |

|                                                               | peak efficiency of 62.5%                                                                                                                                                                                                             |

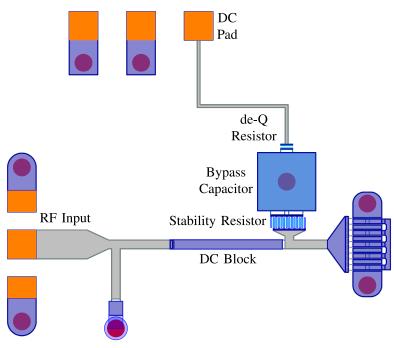

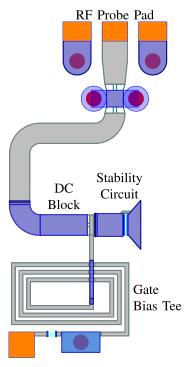

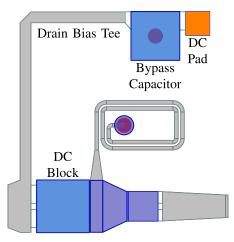

| 6.19                                                          | Layout of the input matching network for the internal PA and rectifier circuits. Meandering                                                                                                                                          |

|                                                               | the input line is used to reduce the circuit area and utilize previously empty vertical space. 138                                                                                                                                   |

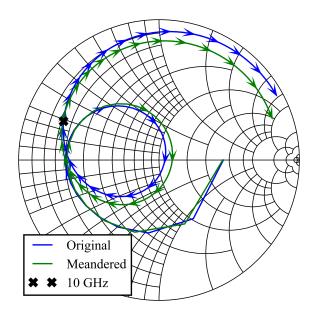

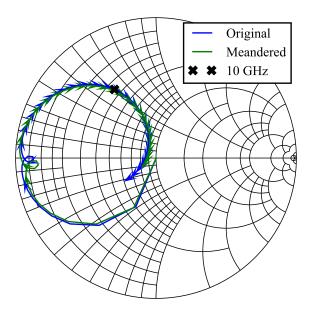

| 6.20                                                          | Input match ( $S_{22}$ of IMN) comparison between the original MMIC design and the new                                                                                                                                               |

|                                                               | compact layout. The layout changes do not significantly affect the impedance presented to                                                                                                                                            |

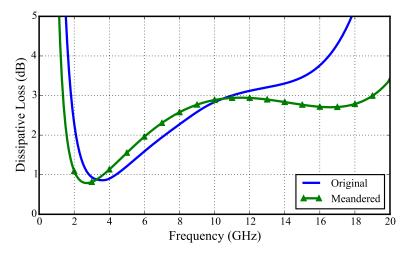

|                                                               | the gate of the transistor                                                                                                                                                                                                           |

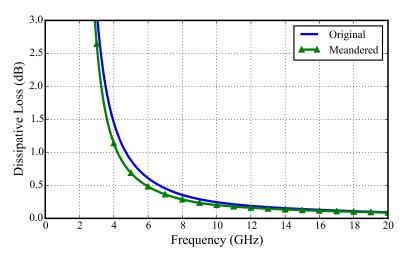

| 6.21                                                          | Input matching dissipative loss comparison between the original MMIC design and the new                                                                                                                                              |

|                                                               | compact layout. The meandering of the IMN has increased the loss by $0.052  dB. \ldots 139$                                                                                                                                          |

| 6.22                                                          | Layout of the output matching network for the internal PA and rectifier circuits. The inductor                                                                                                                                       |

|                                                               | has been shrunk and moved to conserve vertical space                                                                                                                                                                                 |

| 6.23                                                          | Output match ( $S_{11}$ of OMN) comparison between the original MMIC design and the new                                                                                                                                              |

|                                                               | compact layout. The layout changes do not significantly affect the impedance presented to                                                                                                                                            |

|                                                               | the drain of the transistor                                                                                                                                                                                                          |

|                                                               |                                                                                                                                                                                                                                      |

| 6.24                                                          | Output matching dissipative loss comparison between the original MMIC design and the                                                                                                                                                 |

| 6.24                                                          | Output matching dissipative loss comparison between the original MMIC design and the new compact layout. Adjustments to the inductor have actually decreased the loss by 0.044 dB.141                                                |

|                                                               |                                                                                                                                                                                                                                      |

|                                                               | new compact layout. Adjustments to the inductor have actually decreased the loss by 0.044 dB.141                                                                                                                                     |

| 6.25                                                          | new compact layout. Adjustments to the inductor have actually decreased the loss by 0.044 dB.141 Layout of power amplifier circuit, which is also used as the rectifier circuit, appearing three                                     |

| 6.25                                                          | new compact layout. Adjustments to the inductor have actually decreased the loss by 0.044 dB.141<br>Layout of power amplifier circuit, which is also used as the rectifier circuit, appearing three<br>times in the full MMIC layout |

| 6.25<br>6.26                                                  | new compact layout. Adjustments to the inductor have actually decreased the loss by 0.044 dB.141<br>Layout of power amplifier circuit, which is also used as the rectifier circuit, appearing three<br>times in the full MMIC layout |

| 6.25<br>6.26                                                  | new compact layout. Adjustments to the inductor have actually decreased the loss by 0.044 dB.141<br>Layout of power amplifier circuit, which is also used as the rectifier circuit, appearing three<br>times in the full MMIC layout |

| <ul><li>6.25</li><li>6.26</li><li>6.27</li></ul>              | new compact layout. Adjustments to the inductor have actually decreased the loss by 0.044 dB.141<br>Layout of power amplifier circuit, which is also used as the rectifier circuit, appearing three<br>times in the full MMIC layout |

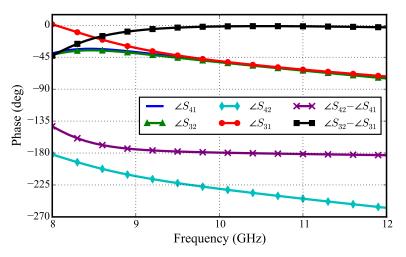

| <ul><li>6.25</li><li>6.26</li><li>6.27</li><li>6.28</li></ul> | new compact layout. Adjustments to the inductor have actually decreased the loss by 0.044 dB.141<br>Layout of power amplifier circuit, which is also used as the rectifier circuit, appearing three<br>times in the full MMIC layout |

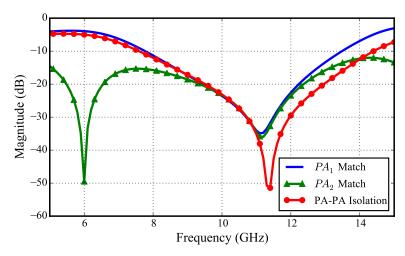

| 6.30 Simulated through loss from each of the PA input ports $(1,2)$ to the output port $(3)$ and the               |

|--------------------------------------------------------------------------------------------------------------------|

| rectifier port (4)                                                                                                 |

| 6.31 Simulated phase between the input and output ports, and the difference between those baths. 145               |

| 6.32 Simulated input match and isolation between inputs                                                            |

| 6.33 Swept outphasing angle simulation of the final MMIC, excluding the rectifier. A peak PAE                      |

| of 56.3% is achieved with 5.2 W of output power                                                                    |

| 6.34 Swept frequency simulation of the final MMIC, excluding the rectifier. A peak PAE of $56.3%$                  |

| is achieved at 10 GHz, while PAE remains above 50% for a little over 1 GHz of bandwidth. $.147$                    |

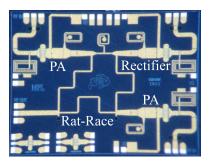

| 6.35 Photograph of the outphasing GaN MMIC PA with integrated rectifier. The internal PAs                          |

| and rectifier utilize $10 \times 100 \mu m$ pHEMTs. A shrunken $180^{\circ}$ rat-race provides isolation and       |

| combining                                                                                                          |

| 6.36 Photograph of fixtured GaN MMIC PA. The chip is mounted on a CuMo tab and bonded to                           |

| alumina transmission lines, on which connectorized launchers land. DC pads are bonded to                           |

| off-chip bypass capacitors and pads on which to land spring loaded DC pins                                         |

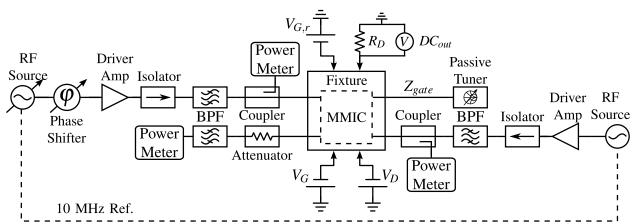

| 6.37 Measurement setup sweeps differential phase while maintaining balanced available power                        |

| (<0.1 dB). The rectifier parameters ( $R_D$ , $V_{G,r}$ , and $Z_{gate}$ ), and PA parameters (Freq, $P_{avail}$ , |

| $V_G, V_D$ ) are tunable                                                                                           |

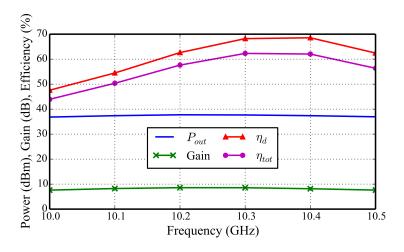

| 6.38 Power, gain and efficiency across frequency with in-phase drive. $\eta_{tot} > 50\%$ and $P_{out} >$          |

| 5 W achieved over at least 400 MHz bandwidth                                                                       |

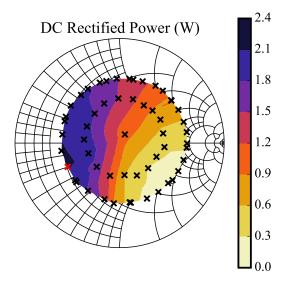

| 6.39 Rectifier load-pull ( $Z_{gate}$ ) for DC rectified power reaches a sensitive peak of 2.24 W. Because         |

| $ \Gamma $ is limited to 0.6, optimal rectified power and efficiency cannot be achieved. Smith chart               |

| is normalized to $50 \Omega$                                                                                       |

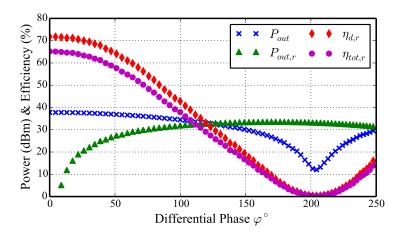

| 6.40 RF output power, DC rectified power, $\eta_{d,r}$ , and $\eta_{tot,r}$ with optimal PA and rectifier parame-  |

| ters. A peak $\eta_{tot}$ of 62.5% is achieved with 6 W of RF output power at 10.35 GHz 151                        |

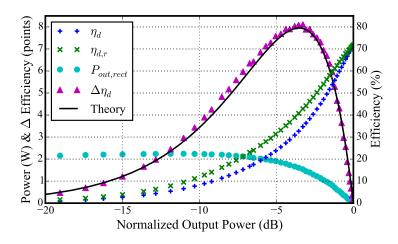

| 6.41 | Measured $\eta_d$ , $\eta_{d,r}$ , DC rectified power, $\Delta \eta_{d,r}$ , and theoretical $\Delta \eta_{d,r}$ demonstrating efficiency |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|

|      | improvement through power recycling as envelope amplitude is decreased. Up to 2.24 W of                                                   |

|      | rectified power improves the system drain efficiency by up to 8.1 points at 3.5 dB back-off,                                              |

|      | matching theory                                                                                                                           |

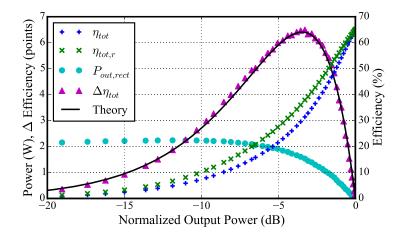

| 6.42 | Measured $\eta_{tot}$ , $\eta_{tot,r}$ , DC rectified power, $\Delta \eta_{tot,r}$ , and theoretical $\Delta \eta_{tot,r}$ demonstrating  |

|      | efficiency improvement through power recycling as envelope amplitude is decreased. Up to                                                  |

|      | 2.24 W of rectified power improves the system total efficiency by up to 6.5 points at 3.5 dB                                              |

|      | back-off, matching theory                                                                                                                 |

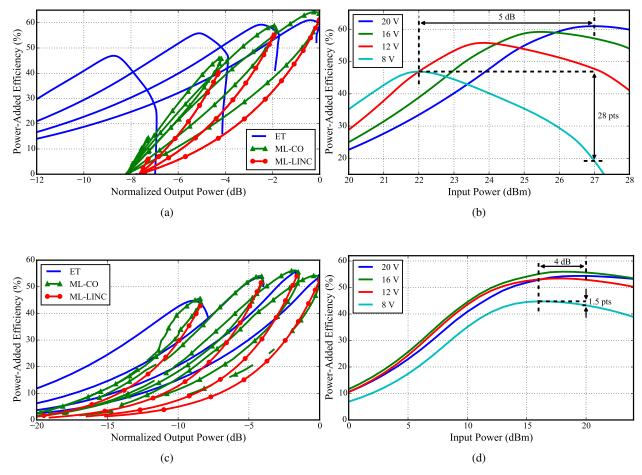

| 7.1  | (a), (c) PAE comparison between ET, ML-CO, and ML-LINC for single-stage and two-stage                                                     |

|      | PAs, respectively. (b), (d) ET characteristic as a function of input power for single-stage and                                           |

|      | two-stage PAs, respectively                                                                                                               |

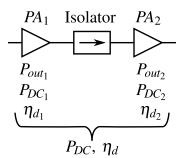

| 7.2  | Two-stage PA analysis diagram                                                                                                             |

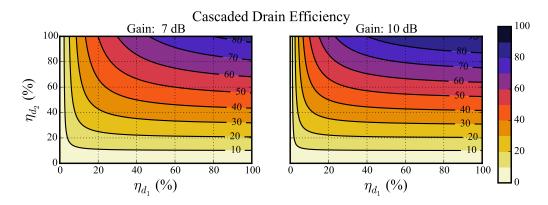

| 7.3  | Cascaded drain efficiency of the circuit in Fig. 7.2 as a function of the efficiency of each                                              |

|      | stage, shown for output stage gains of 7 and 10 dB                                                                                        |

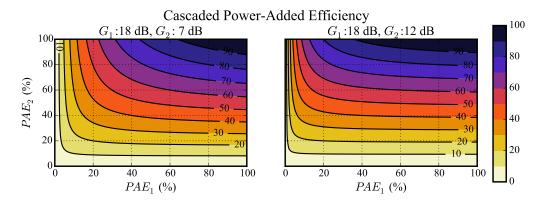

| 7.4  | Cascaded PAE of the circuit in Fig. 7.2 as a function of the PAE of each stage, shown for                                                 |

|      | 18 dB driver stage gain with 7 and 12 dB output stage gains                                                                               |

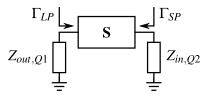

| 7.5  | High efficiency interstage matching network circuit. $Z_{out,Q1}$ and $Z_{in,Q2}$ are the output and                                      |

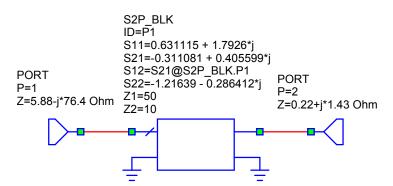

|      | input impedances of the driver and power transistors, respectively                                                                        |

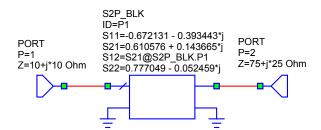

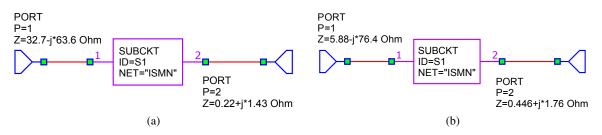

| 7.6  | AWR simulation setup demonstrating validity of derived 50 $\Omega$ S-parameters for achieving                                             |

|      | desired complex conjugate match                                                                                                           |

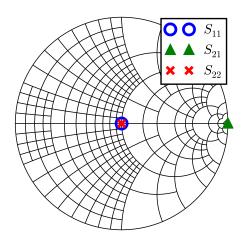

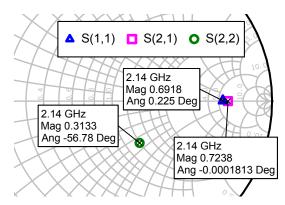

| 7.7  | AWR simulation results demonstrating validity of derived 50 $\Omega$ S-parameters for achieving                                           |

|      | desired complex conjugate match                                                                                                           |

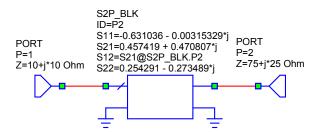

| 7.8  | AWR simulation setup demonstrating validity of derived 50 $\Omega$ S-parameters for achieving                                             |

|      | desired mismatch                                                                                                                          |

| 7.9  | AWR simulation results demonstrating validity of derived 50 $\Omega$ S-parameters for achieving                                           |

|      | desired mismatch                                                                                                                          |

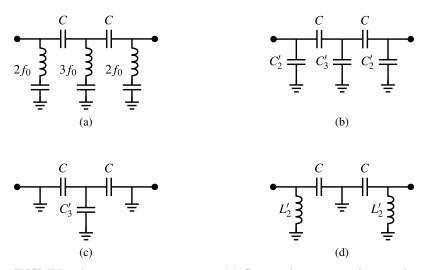

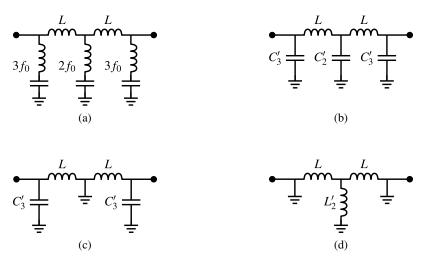

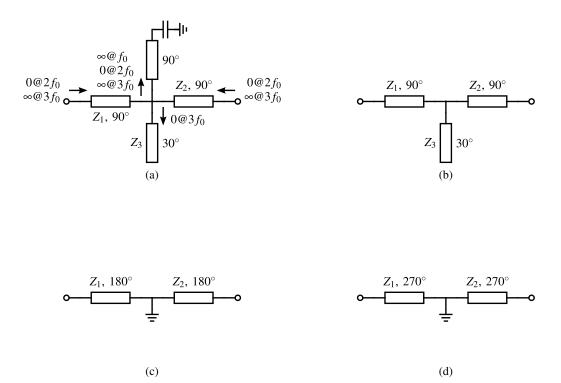

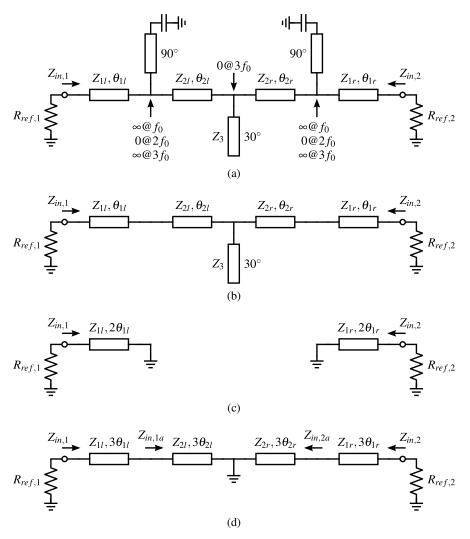

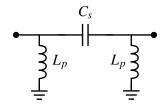

| 7.10 | Class-F ISMN utilizing series resonators. (a) Circuit diagram, and equivalent circuits at (b)                  |

|------|----------------------------------------------------------------------------------------------------------------|

|      | $f_0$ , (c) $2f_0$ , and (d) $3f_0$                                                                            |

| 7.11 | Class-F ISMN utilizing parallel resonators (a) Circuit diagram, and equivalent circuits at (b)                 |

|      | $f_0$ , (c) $2f_0$ , and (d) $3f_0$                                                                            |

| 7.12 | Class-F ISMN utilizing both series and parallel resonators. (a) Circuit diagram. Equivalent                    |

|      | circuits at (b) $f_0$ , (c) $2f_0$ , and (d) $3f_0$                                                            |

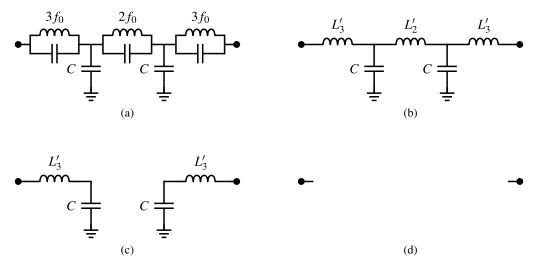

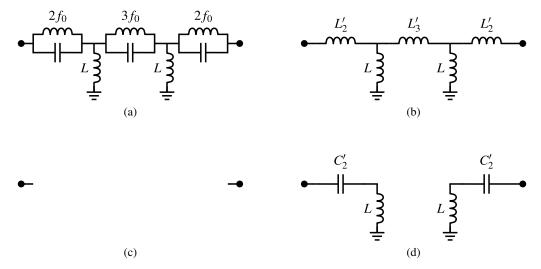

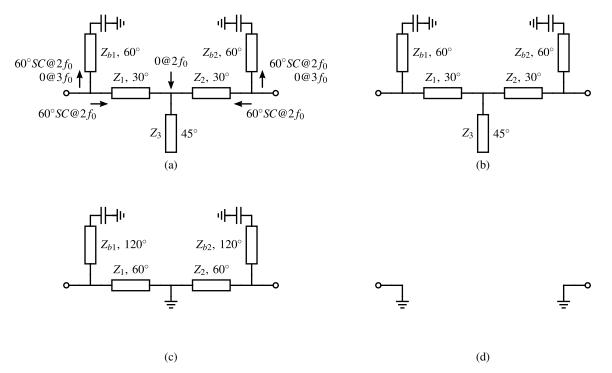

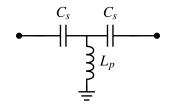

| 7.13 | Inverse class-F ISMN utilizing series resonators. (a) Circuit diagram, and equivalent circuits                 |

|      | at (b) $f_0$ , (c) $2f_0$ , and (d) $3f_0$                                                                     |

| 7.14 | Inverse class-F ISMN utilizing parallel resonators. (a) Circuit diagram, and quivalent circuits                |

|      | at (b) $f_0$ , (c) $2f_0$ , and (d) $3f_0$                                                                     |

| 7.15 | Inverse class-F ISMN utilizing both series and parallel resonators. (a) Circuit diagram, and                   |

|      | equivalent circuits at (b) $f_0$ , (c) $2f_0$ , and (d) $3f_0$                                                 |

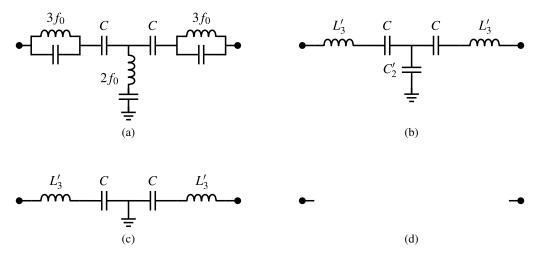

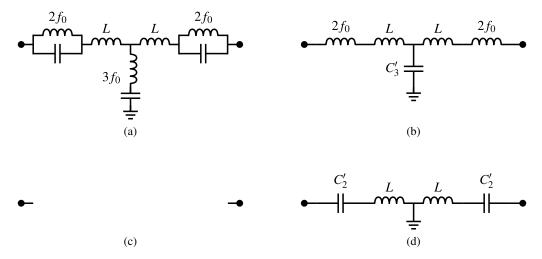

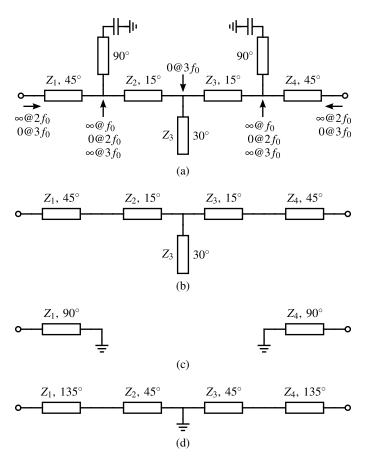

| 7.16 | (a) Class-F ISMN circuit diagram. Equivalent circuits at (b) $f_0$ , (c) $2f_0$ , and (d) $3f_0$ 176           |

| 7.17 | (a) Class-F ISMN circuit diagram. Equivalent circuits at (b) $f_0$ , (c) $2f_0$ , and (d) $3f_0$ 177           |

| 7.18 | (a) Inverse class-F ISMN circuit diagram. Equivalent circuits at (b) $f_0$ , (c) $2f_0$ , and (d) $3f_0$ . 178 |

| 7.19 | Required relationship for second harmonic open circuit termination for first inverse class-F                   |

|      | ISMN                                                                                                           |

| 7.20 | (a) Inverse class-F ISMN circuit diagram. Equivalent circuits at (b) $f_0$ , (c) $2f_0$ , and (d) $3f_0$ . 180 |

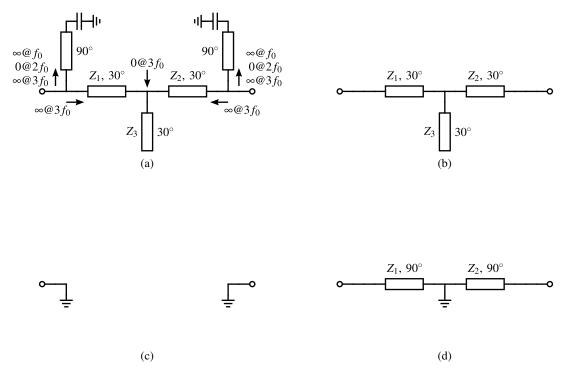

| 7.21 | (a) Arbitrary phase harmonic termination ISMN circuit diagram. Equivalent circuits at (b)                      |

|      | $f_0$ , (c) $2f_0$ , and (d) $3f_0$                                                                            |

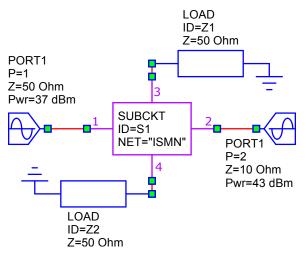

| 7.22 | AWR simulation setup to confirm ISMN S-parameters                                                              |

| 7.23 | Simulation of ISMN S-parameters showing desired results                                                        |

| 7.24 | AWR simulation setup for the optimization of the ISMN at the fundamental frequency,                            |

|      | considering the transistors as generators                                                                      |

| 7.25 | AWR simulation setup to optimize the ISMN performance passively for (a) the driver stage                       |

|      | load, and (b) the power stage load                                                                             |

| 8.1         | Active interstage load-pull network |

|-------------|-------------------------------------|

| A.1         | Series LC resonator                 |

| A.2         | Parallel LC resonator               |

|             |                                     |

| <b>B</b> .1 | Low-pass $\pi$ -network             |

| B.2         | Low-pass T-network                  |

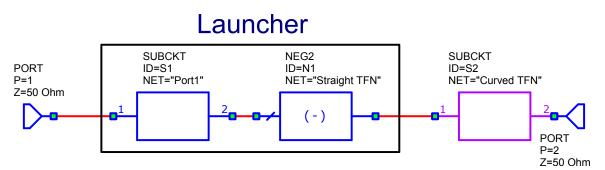

| B.3         | Low-pass TL- $\pi$ -Network         |