# Advanced electrified automotive powertrain with composite DC-DC converter

by

## Hua Chen

B.Eng., The Chinese University of Hong Kong, 2010M.S., University of Colorado Boulder, 2014

A thesis submitted to the Faculty of the Graduate School of the University of Colorado in partial fulfillment of the requirements for the degree of Doctor of Philosophy Department of Electrical, Computer, and Energy Engineering

2016

This thesis entitled: Advanced electrified automotive powertrain with composite DC-DC converter written by Hua Chen has been approved for the Department of Electrical, Computer, and Energy Engineering

Prof. Robert Erickson

Prof. Dragan Maksimovic

Date \_\_\_\_\_

The final copy of this thesis has been examined by the signatories, and we find that both the content and the form meet acceptable presentation standards of scholarly work in the above mentioned discipline.

#### Chen, Hua (Ph.D., ECEE)

Advanced electrified automotive powertrain

with composite DC-DC converter

Thesis directed by Prof. Robert Erickson

In an electric vehicle powertrain, a boost dc-dc converter enables size reduction of the electric machine and optimization of the battery system. Design of the powertrain boost converter is challenging because the converter must be rated at high peak power, while efficiency at medium to light load is critical for the vehicle system performance. The previously proposed efficiency improvement approaches only offer limited improvements in size, cost and efficiency trade-offs.

In this work, the concept of composite converter architectures is proposed. By emphasizing the direct / indirect power path explicitly, this approach addresses all dominant loss mechanisms, resulting in fundamental efficiency improvements over wide ranges of operating conditions. The key component of composite converter approach, the DC Transformer (DCX) converter, is extensively discussed in this work, and important improvements are proposed. It enhances the DCX efficiency over full power range, and more than ten times loss reduction is achieved at the no load condition.

Several composite converter prototypes are presented, ranging from 10 kW to 60 kW rated power. They validate the concept of composite converter, as well as demonstrate the scalability of this approach. With peak efficiency of 98.5% to 98.7% recorded, the prototypes show superior efficiency over a wide operation range. Comparing with the conventional approach, it is found that the composite converter results in a decrease in the total loss by a factor of two to four for typical drive cycles. Furthermore, the total system capacitor power rating and energy rating are substantially reduced, which implies potentials for significant reductions in system size and cost.

A novel control algorithm is proposed in this work as well, which proves the controllability of the composite converter approach. Dedication

To my father

#### Acknowledgements

The author would like to acknowledge the assistance, guidance, and support from my supervisors Professors Robert Erickson and Dragan Maksimovic. There knowledge in power electronics is unparalleled, and I have learnt invaluable lessons from their style of organizing and presenting technical materials. Without their supervision and encouragement, the completion of this thesis would not be possible.

I would also like to acknowledge the assistance from my committee members, Professors Khurram Afridi, David Jones, and Daniel Costinett, and thank them for agreeing to take their precious time to serve as my thesis committee.

In addition, I would like to thank Professor Alex Leung from the Chinese University of Hong Kong, who first introduced me into the world of electronics, and gave me useful professional advices throughout my career. I would like to thank Dr. Yanqi Zheng from Sun Yat-sen University, who led me to the wonderful field of power electronics. I would also like to thank Professor Lucy Pao from University of Colorado Boulder, who gave me the chance to explore different fields of engineering.

I would like to thank my colleagues in Colorado power electronics center (CoPEC) for their inspiring discussions. I would like to thank Mr. Kamal Sabi and Mr. Tadakazu Harada for their assistance at different stages of my research. I am especially grateful to the assistance from Mr. Hyeokjin Kim, whose diligence sometimes makes me abashed.

Finally, I would like to acknowledge both the financial and emotional support from my family. Especially I would like to thank the support and understanding from my wife Qian Jia throughout the years.

## Contents

# Chapter

| 1        | Elec | trified A | Automotive Powertrain Overview                     | 1  |

|----------|------|-----------|----------------------------------------------------|----|

|          | 1.1  | Power     | train architecture overview                        | 2  |

|          |      | 1.1.1     | Battery Electric Vehicle (BEV)                     | 3  |

|          |      | 1.1.2     | Hybrid Electric Vehicle (HEV)                      | 5  |

|          |      | 1.1.3     | Fuel Cell Electric Vehicle (FCEV)                  | 7  |

|          | 1.2  | Power     | electronics in electrified powertrain              | 8  |

|          | 1.3  | Power     | train application characteristics                  | 10 |

|          | 1.4  | Model     | ing of electrified traction systems                | 12 |

|          |      | 1.4.1     | Vehicle model                                      | 12 |

|          |      | 1.4.2     | Electric machine model                             | 14 |

|          |      | 1.4.3     | Motor drive and dc bus voltage control             | 16 |

|          |      | 1.4.4     | Electrified traction system simulation             | 17 |

| <b>2</b> | Boo  | st DC-I   | DC Converter Technology Overview                   | 22 |

|          | 2.1  | Conve     | ntional boost converter                            | 22 |

|          |      | 2.1.1     | Conventional boost converter operation             | 22 |

|          |      | 2.1.2     | Boost converter loss model                         | 24 |

|          |      | 2.1.3     | Conventional boost converter efficiency prediction | 28 |

|          | 2.2  | Soft sv   | witching techniques                                | 31 |

|   |     | 2.2.1   | Operation of SAZZ converter                                                                                                                                      | 32 |

|---|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |     | 2.2.2   | SAZZ converter efficiency prediction                                                                                                                             | 33 |

|   | 2.3 | Couple  | ed inductor approach                                                                                                                                             | 34 |

|   |     | 2.3.1   | Coupled inductor boost converter operation                                                                                                                       | 36 |

|   |     | 2.3.2   | Coupled inductor boost converter efficiency prediction                                                                                                           | 38 |

|   | 2.4 | Three-  | level converter                                                                                                                                                  | 40 |

|   |     | 2.4.1   | Three-level converter operation                                                                                                                                  | 41 |

|   |     | 2.4.2   | Three-level converter efficiency prediction                                                                                                                      | 43 |

|   | 2.5 | Imped   | ance-source inverter                                                                                                                                             | 45 |

|   |     | 2.5.1   | Impedance-source inverter operation                                                                                                                              | 46 |

| 3 | Con | nposite | DC-DC Converter Concept                                                                                                                                          | 50 |

|   | 3.1 | Direct  | / indirect power and power loss $\ldots \ldots $ | 50 |

|   | 3.2 | Comp    | osite converter architecture A                                                                                                                                   | 56 |

|   | 3.3 | Comp    | osite converter architecture B                                                                                                                                   | 59 |

|   | 3.4 | Comp    | osite converter architecture C                                                                                                                                   | 61 |

|   | 3.5 | Comp    | osite converter architecture D                                                                                                                                   | 63 |

|   | 3.6 | Compa   | arison of converter approaches                                                                                                                                   | 66 |

|   |     | 3.6.1   | Generic comparison                                                                                                                                               | 66 |

|   |     | 3.6.2   | Composite converter comparisons                                                                                                                                  | 70 |

|   |     | 3.6.3   | Comparison with efficiencies of prior approaches                                                                                                                 | 71 |

|   |     | 3.6.4   | Comparison of average efficiency over standard driving test cycles                                                                                               | 73 |

|   |     | 3.6.5   | Converter size comparison                                                                                                                                        | 74 |

| 4 | DC  | Transfo | rmer and Efficiency-Enhanced Dual Active Bridge                                                                                                                  | 77 |

|   | 4.1 | DCX o   | operation and simplified model                                                                                                                                   | 78 |

|   |     | 4.1.1   | Ideal active rectification                                                                                                                                       | 79 |

|   |     | 4.1.2   | Passive rectification                                                                                                                                            | 80 |

|          | 4.2         | DCX soft switching analysis                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |             | 4.2.1 Ideal resonance analysis                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |             | 4.2.2 Nonlinear capacitance treatment                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          | 4.3         | DCX loss model                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |             | 4.3.1 Semiconductor loss                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |             | 4.3.2 Magnetic loss                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|          |             | 4.3.3 Loss model and measurement comparison                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          | 4.4         | DCX light load efficiency improvement                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          |             | 4.4.1 Conventional approaches                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          |             | 4.4.2 Extended $LLCC$ resonant transition $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                        |

|          |             | 4.4.3 Experimental validation                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          | 4.5         | DCX heavy load efficiency improvement                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          | 4.6         | Efficiency-enhanced Dual Active Bridge control                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <b>5</b> | Imp         | ementation Examples of Composite DC-DC Converter 131                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5        | Imp]<br>5.1 | ementation Examples of Composite DC-DC Converter       131         10 kW silicon-device-based prototype       131                                                                                                                                                                                                                                                                                                                                                       |

| 5        | -           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5        | -           | 10 kW silicon-device-based prototype                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5        | -           | 10 kW silicon-device-based prototype       131         5.1.1       Design optimization       132                                                                                                                                                                                                                                                                                                                                                                        |

| 5        | -           | 10 kW silicon-device-based prototype       131         5.1.1 Design optimization       132         5.1.2 Comparison with Conventional Boost Converter       134                                                                                                                                                                                                                                                                                                         |

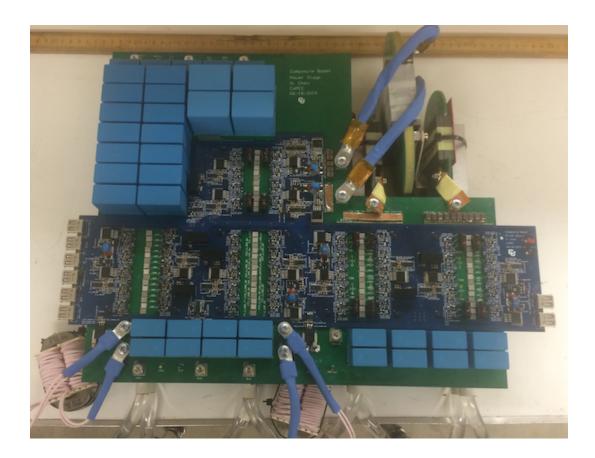

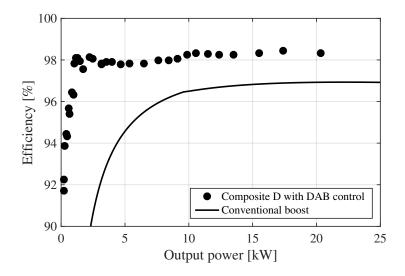

| 5        | 5.1         | 10 kW silicon-device-based prototype       131         5.1.1 Design optimization       132         5.1.2 Comparison with Conventional Boost Converter       134         5.1.3 Experimental Results       139                                                                                                                                                                                                                                                            |

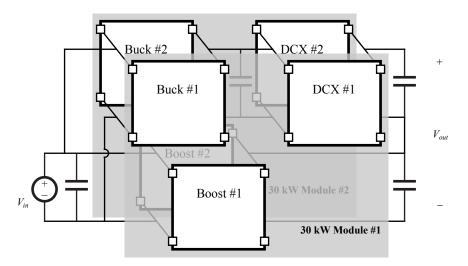

| 5        | 5.1         | 10 kW silicon-device-based prototype       131         5.1.1 Design optimization       132         5.1.2 Comparison with Conventional Boost Converter       134         5.1.3 Experimental Results       139         30 kW silicon-device-based prototype       142                                                                                                                                                                                                     |

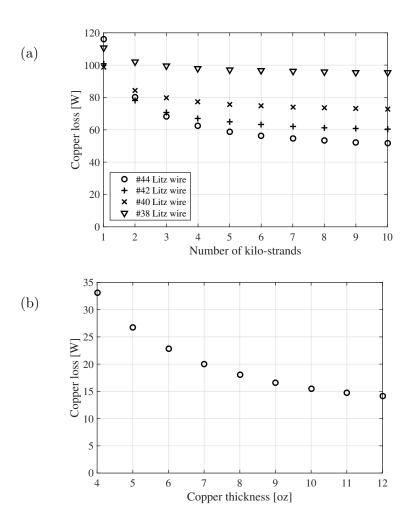

| 5        | 5.1         | 10 kW silicon-device-based prototype       131         5.1.1 Design optimization       132         5.1.2 Comparison with Conventional Boost Converter       134         5.1.3 Experimental Results       139         30 kW silicon-device-based prototype       142         5.2.1 Magnetics design       144                                                                                                                                                            |

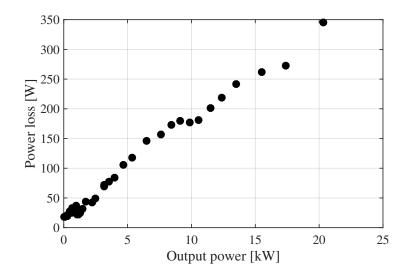

| 5        | 5.1         | 10 kW silicon-device-based prototype       131         5.1.1 Design optimization       132         5.1.2 Comparison with Conventional Boost Converter       134         5.1.3 Experimental Results       139         30 kW silicon-device-based prototype       142         5.2.1 Magnetics design       144         5.2.2 Measurement results       155                                                                                                                |

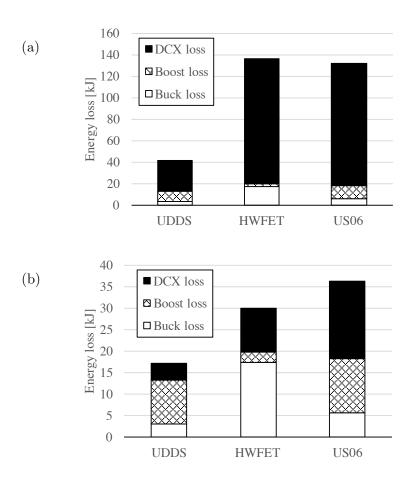

| 5        | 5.1         | 10 kW silicon-device-based prototype       131         5.1.1 Design optimization       132         5.1.2 Comparison with Conventional Boost Converter       134         5.1.3 Experimental Results       139         30 kW silicon-device-based prototype       142         5.2.1 Magnetics design       144         5.2.2 Measurement results       155         5.2.3 30 kW prototype second revision       159                                                        |

| 5        | 5.1         | 10 kW silicon-device-based prototype       131         5.1.1 Design optimization       132         5.1.2 Comparison with Conventional Boost Converter       134         5.1.3 Experimental Results       139         30 kW silicon-device-based prototype       142         5.2.1 Magnetics design       144         5.2.2 Measurement results       155         5.2.3 30 kW prototype second revision       159         60 kW silicon-device-based prototype       164 |

| 6 | Con    | trol of | Composite DC-DC Converter                        | 178        |

|---|--------|---------|--------------------------------------------------|------------|

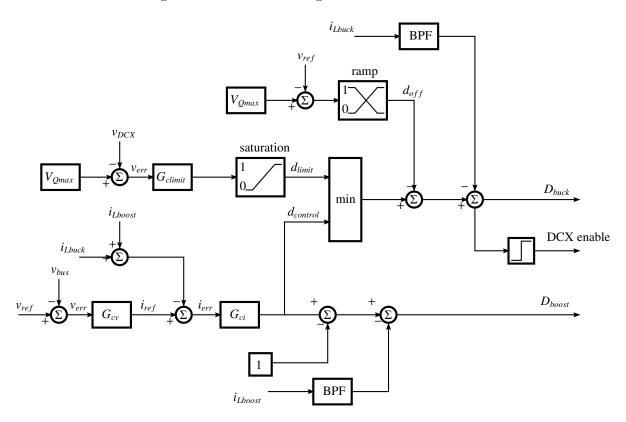

|   | 6.1    | Propo   | sed Control Algorithm                            | . 178      |

|   |        | 6.1.1   | Main control loop                                | . 180      |

|   |        | 6.1.2   | DCX voltage limit                                | . 182      |

|   |        | 6.1.3   | Boost-only mode                                  | . 184      |

|   |        | 6.1.4   | Auxiliary current loop with band-pass filter     | . 186      |

|   |        | 6.1.5   | Summary of controller architecture               | . 188      |

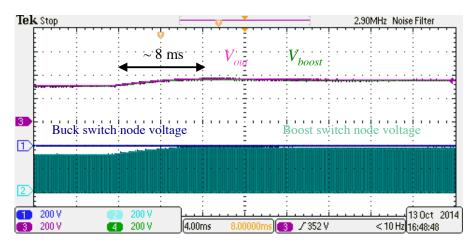

|   | 6.2    | Exper   | imental result of proposed controller operation  | . 190      |

| 7 | Con    | clusion | and extension of the work                        | 198        |

| Е | Biblic | ography | y.                                               | 202        |

| A | ppe    | ndix    |                                                  |            |

| Α | DC     | X Exter | nded $LLCC$ Resonance Modeling                   | 210        |

|   | A.1    | Deriva  | ation of fourth-order state plane transformation | . 210      |

|   | A.2    | Comp    | lete DCX resonant model                          | . 213      |

| в | Imp    | lementa | ation of efficiency-enhanced DAB control         | <b>221</b> |

## Tables

## Table

| 1.1  | A typical mid-size sedan vehicle model parameters                                                | 17 |

|------|--------------------------------------------------------------------------------------------------|----|

| 1.2  | A typical traction PMSM model parameters                                                         | 17 |

| 1.3  | Converter quality factor $Q$ comparison between the composite D converter and the                |    |

|      | conventional boost converter, under standard driving cycles $\ldots \ldots \ldots \ldots \ldots$ | 20 |

| 2.1  | 1200 V 200 A 2MBI200VB-120-50 IGBT Module Loss Model                                             | 29 |

| 2.2  | Conventional Boost Design Summary                                                                | 29 |

| 2.3  | Converter quality factor $Q$ of the conventional boost converter, under standard driv-           |    |

|      | ing cycles                                                                                       | 31 |

| 2.4  | Converter quality factor $Q$ comparison between the SAZZ approach and the conven-                |    |

|      | tional approach, under standard driving cycles                                                   | 34 |

| 2.5  | 1200 V 100 A 2MBI100VA-120-50 IGBT Module Loss Model $\hfill \ldots \ldots \ldots \ldots \ldots$ | 39 |

| 2.6  | Coupled Inductor Boost Design Summary                                                            | 39 |

| 2.7  | Converter quality factor $Q$ comparison between the coupled inductor approach and                |    |

|      | the conventional approach, under standard driving cycles                                         | 40 |

| 2.8  | 600 V 46 A FCH76N60NF Super-Junction MOSFET Loss Model                                           | 43 |

| 2.9  | Three-level Boost Design Summary                                                                 | 44 |

| 2.10 | Converter quality factor $Q$ comparison between the three-level converter and the                |    |

|      | conventional boost converter, under standard driving cycles                                      | 45 |

|      |                                                                                                  |    |

| 2.11 | Converter quality factor $Q$ comparison of existing approaches $\ldots \ldots \ldots \ldots \ldots$  | 49  |

|------|------------------------------------------------------------------------------------------------------|-----|

| 3.1  | Composite A Converter Magnetics Design Summary                                                       | 57  |

| 3.2  | Composite B Converter Magnetics Design Summary                                                       | 60  |

| 3.3  | Composite C Converter Magnetics Design Summary                                                       | 62  |

| 3.4  | Composite D Converter Magnetics Design Summary                                                       | 65  |

| 3.5  | Converter Specified Device Power Rating $P_{Dn}$ Comparison at fixed Voltage Conver-                 |     |

|      | sion Ratio $M = 3.25$                                                                                | 67  |

| 3.6  | Converter Total Capacitor Power Rating Comparison with $M_{max} = 4 \dots \dots$                     | 69  |

| 3.7  | Converter Quality Factor $Q$ For Standard Driving Cycles $\ldots \ldots \ldots \ldots \ldots \ldots$ | 73  |

| 3.8  | Converter Size Comparison                                                                            | 74  |

| 4.1  | Diode model parameters                                                                               | 92  |

| 4.2  | 20 kW DCX prototype design parameters                                                                | 97  |

| 4.3  | Predicted converter quality factor $Q$ of the $20\mathrm{kW}$ DCX module prototype within a          |     |

|      | composite D converter, under different driving profiles (with 250 V battery voltage). 1              | .30 |

| 5.1  | Module specification summary                                                                         | .33 |

| 5.2  | Composite converter design summary                                                                   | .34 |

| 5.3  | Switch rms current comparison at $210$ V input, $650$ V output with 5 kW output power 1              | .35 |

| 5.4  | Capacitor rating for conventional and composite converters                                           | .38 |

| 5.5  | Total capacitor energy and power rating comparison                                                   | .38 |

| 5.6  | DCX planar transformer parameters                                                                    | .50 |

| 5.7  | DCX planar tank inductor parameters                                                                  | .50 |

| 5.8  | Boost Inductor Design                                                                                | .54 |

| 5.9  | Buck inductor Design                                                                                 | .54 |

| 5.10 | Measured 30 kW system efficiency for forward and reverse power flow $\ldots \ldots \ldots \ldots $   | .58 |

| 5.11 | Magnetics design summary of 30 kW prototype second revision                                          | 59  |

| 5.12 | Predicted converter quality factor $Q$ and average efficiency $\eta$ of 30 kW composite         |

|------|-------------------------------------------------------------------------------------------------|

|      | converter prototype under different driving profiles (with $250\mathrm{V}$ battery voltage) 164 |

| 5.13 | $30\mathrm{kW}$ Composite A converter with SiC devices magnetics component design 174           |

| 5.14 | 30 kW Composite A converter with SiC devices capacitor design                                   |

| 5.15 | Converter quality factor $Q$ comparison between composite A converter with SiC de-              |

|      | vices and the conventional boost converter                                                      |

| 7.1  | Converter quality factor $Q$ comparison between the composite D converter and the               |

|      | conventional boost converter, under standard driving cycles                                     |

| B.1  | Micro-controller ePWM channel designation                                                       |

| B.2  | Micro-controller ADC channel configuration                                                      |

# Figures

# Figure

| 1.1  | Battery electric vehicle (BEV) powertrain architecture                                                                                  | 2  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Hybrid electric vehicle (HEV) powertrain architecture                                                                                   | 5  |

| 1.3  | Fuel cell electric vehicle (FCEV) powertrain architecture                                                                               | 8  |

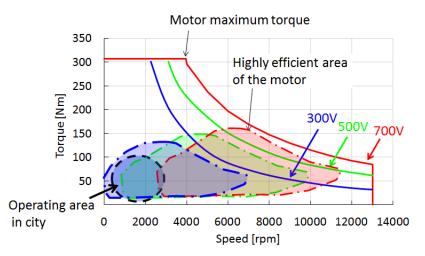

| 1.4  | High efficiency operation area of the motor under different bus voltages                                                                | 10 |

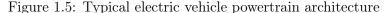

| 1.5  | Typical electric vehicle powertrain architecture                                                                                        | 11 |

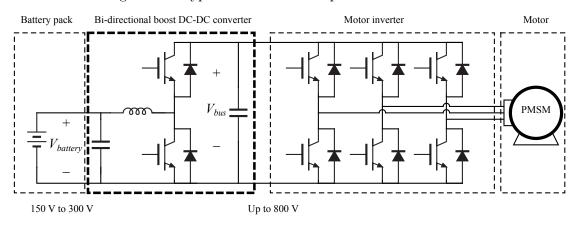

| 1.6  | Converter quality factor $Q = P_{out}/P_{loss}$ metric vs. efficiency $\eta$                                                            | 11 |

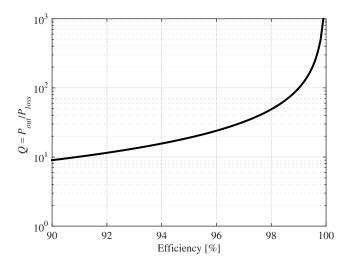

| 1.7  | Simulation of a typical Ford Forcus electric vehicle                                                                                    | 13 |

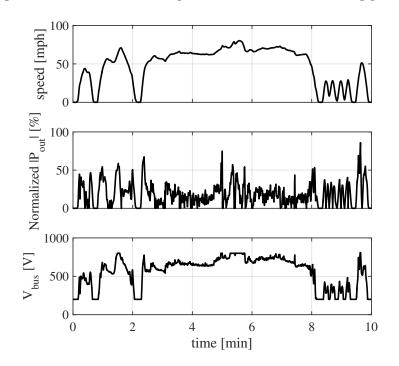

| 1.8  | Modeled traction powertrain with US06 driving profile                                                                                   | 18 |

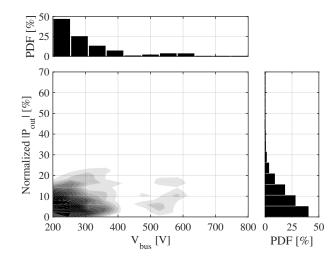

| 1.9  | $V_{bus}$ and normalized $ P_{out} $ probability distribution in simulated UDDS driving cycle.                                          | 19 |

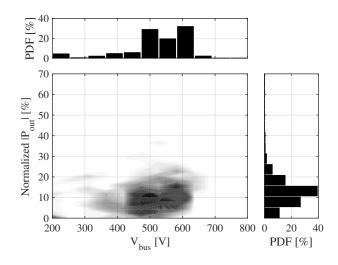

| 1.10 | $V_{bus}$ and normalized $ P_{out} $ probability distribution in simulated HWFET driving cycle.                                         | 19 |

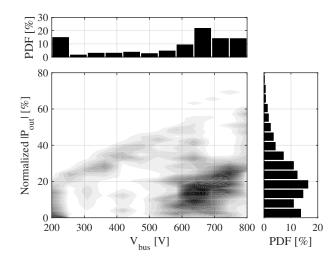

| 1.11 | $V_{bus}$ and normalized $ P_{out} $ probability distribution in simulated US06 driving cycle                                           | 20 |

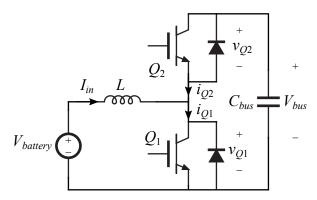

| 2.1  | Conventional bi-directional boost converter realized with IGBT                                                                          | 23 |

| 2.2  | Switch $Q_1$ voltage and current waveforms $\ldots \ldots \ldots$ | 23 |

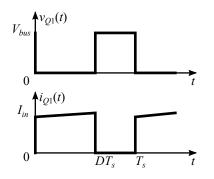

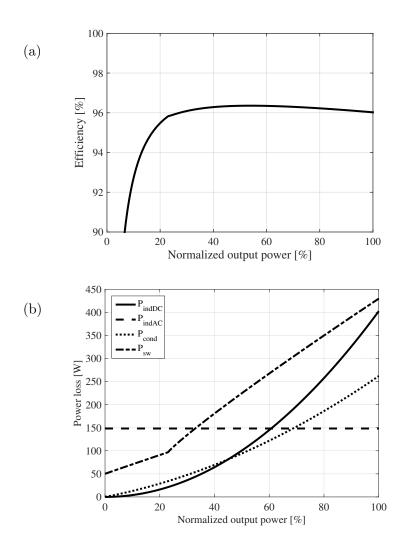

| 2.3  | Typical conventional boost converter design at $V_{battery} = 200$ V and $V_{bus} = 650$ V:                                             |    |

|      | (a) converter efficiency vs. normalized output power; (b) normalized power loss vs.                                                     |    |

|      | normalized output power.                                                                                                                | 30 |

| 2.4  | Bi-directional boost SAZZ converter in [45]                                                                                             | 32 |

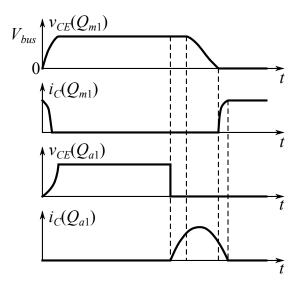

| 2.5  | Waveforms of boost SAZZ converter with the operation of positive power flow, re-                                                        |    |

|      | produced from [45]                                                                                                                      | 33 |

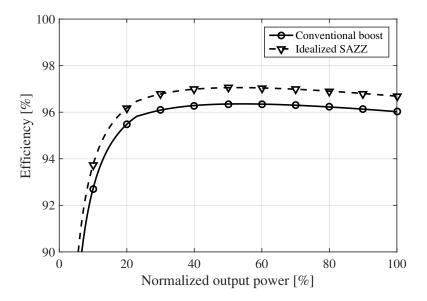

| 2.6  | Idealized SAZZ converter efficiency prediction                                                                                                                  | 34 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

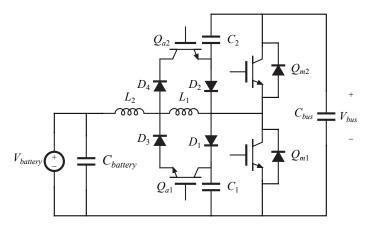

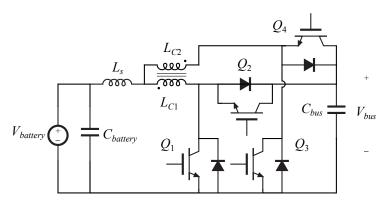

| 2.7  | Bi-directional coupled inductor boost converter                                                                                                                 | 35 |

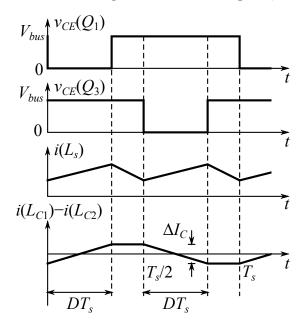

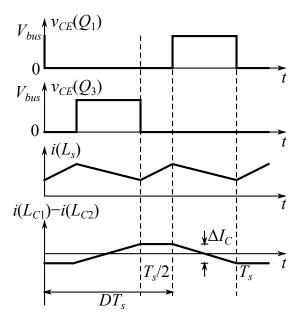

| 2.8  | Waveforms of close-coupled converter in Fig. 2.7, with duty cycle $D \leq 50\%$                                                                                 | 36 |

| 2.9  | Waveforms of close-coupled converter in Fig. 2.7, with duty cycle $D > 50\%$                                                                                    | 37 |

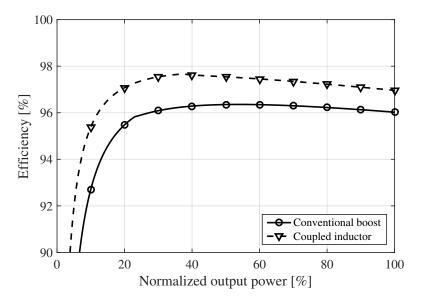

| 2.10 | Coupled inductor boost converter efficiency prediction                                                                                                          | 40 |

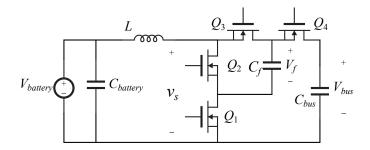

| 2.11 | Bi-directional three-level boost converter                                                                                                                      | 40 |

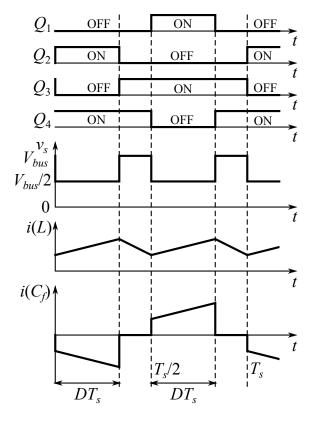

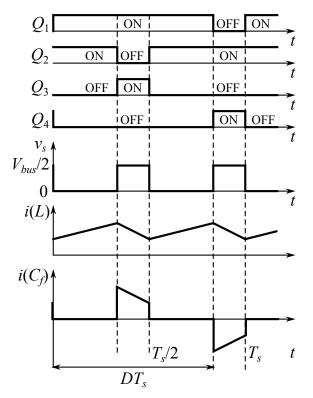

| 2.12 | Waveforms of three-level boost converter, when the voltage conversion ratio $M \leq 2.$ .                                                                       | 41 |

| 2.13 | Waveforms of three-level boost converter, when the voltage conversion ratio $M>2.$ .                                                                            | 42 |

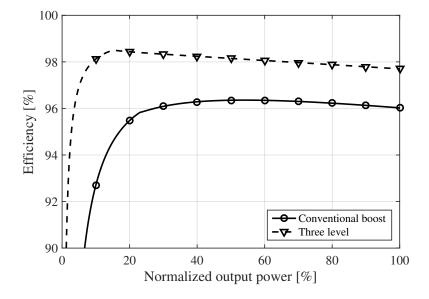

| 2.14 | Three-level boost converter efficiency prediction                                                                                                               | 44 |

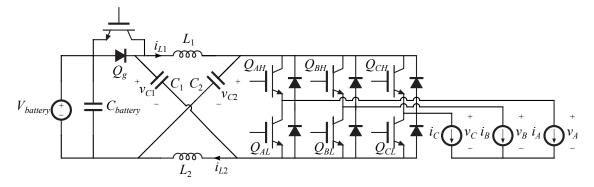

| 2.15 | Bi-directional three-phase Z-source inverter                                                                                                                    | 46 |

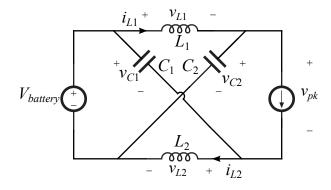

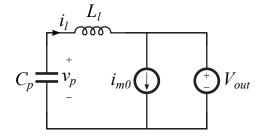

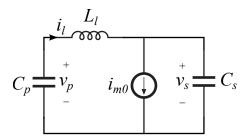

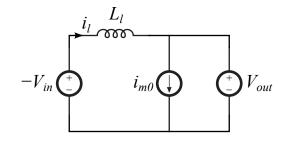

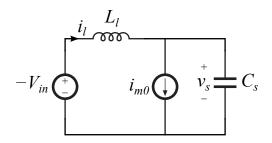

| 2.16 | The equivalent circuit of Z-source inverter at normal chopping phase                                                                                            | 46 |

| 2.17 | The equivalent circuit of Z-source inverter at shoot-through phase                                                                                              | 47 |

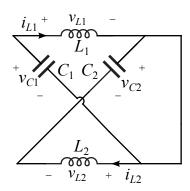

| 3.1  | Conventional boost converter averaged switch model                                                                                                              | 50 |

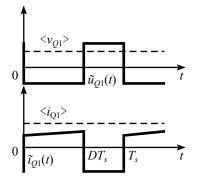

| 3.2  | Average and ac components of transistor $Q_1$ voltage and current $v_{Q_1}$ and $i_{Q_1}$                                                                       | 51 |

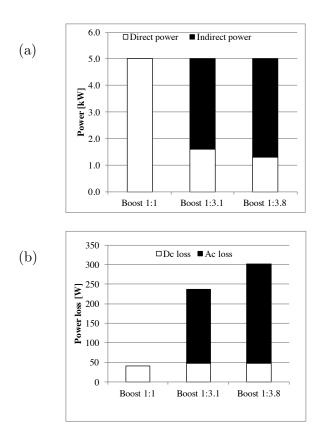

| 3.3  | Relationship between direct $/$ indirect power and dc $/$ ac power loss: (a) direct $/$                                                                         |    |

|      | indirect power distribution; (b) power loss distribution $\ldots \ldots \ldots \ldots \ldots \ldots$                                                            | 53 |

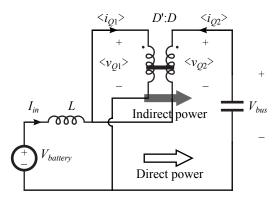

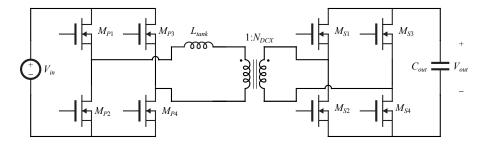

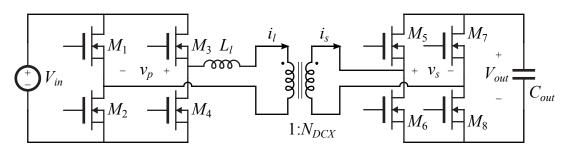

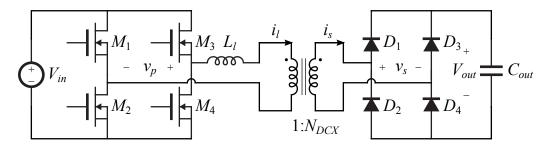

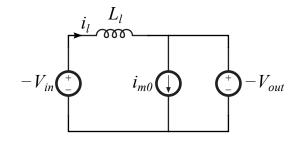

| 3.4  | Power stage schematic of DC Transformer (DCX) module                                                                                                            | 54 |

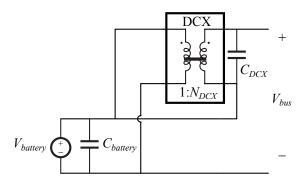

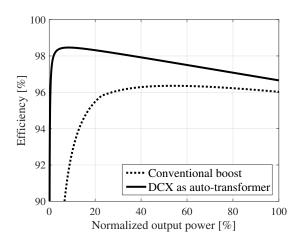

| 3.5  | DCX connected as an auto-transformer                                                                                                                            | 55 |

| 3.6  | Modeled efficiency of DCX module connected as an auto-transformer                                                                                               | 55 |

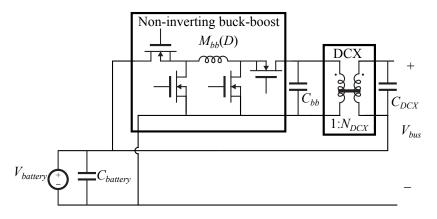

| 3.7  | Boost composite converter A                                                                                                                                     | 56 |

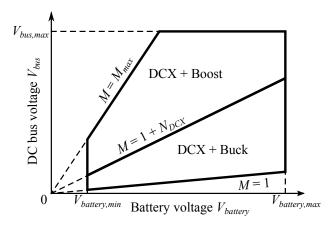

| 3.8  | Composite converter A & B operating modes                                                                                                                       | 56 |

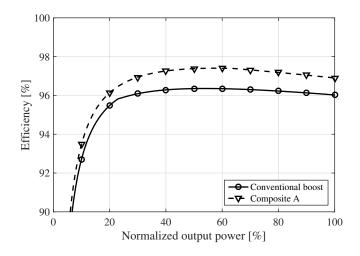

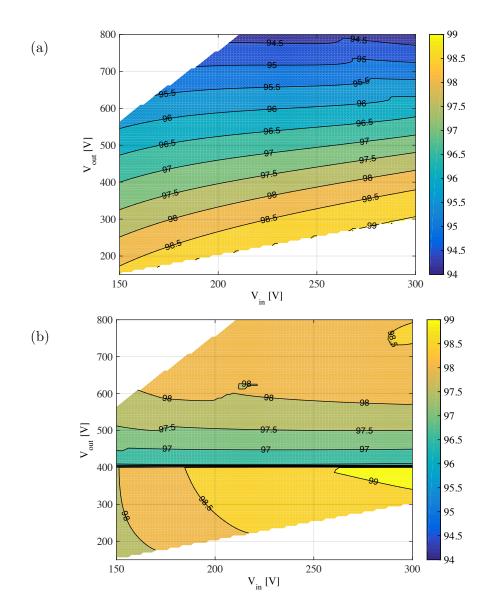

| 3.9  | Modeled efficiency of composite A converter                                                                                                                     | 58 |

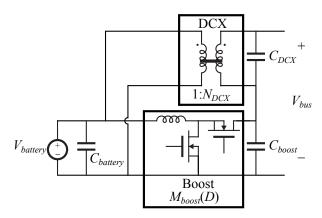

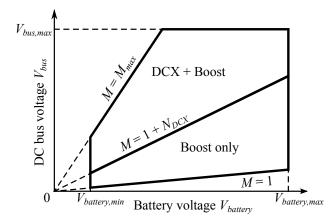

| 3.10 | Composite converter topology B                                                                                                                                  | 59 |

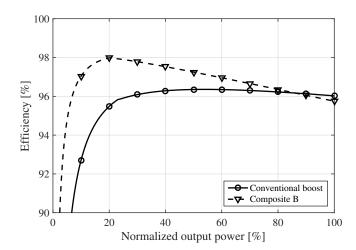

| 3.11 | Modeled efficiency of composite B converter                                                                                                                     | 60 |

| 3.12 | Composite converter topology C $\ldots \ldots $ | 61 |

| 3.13 | Composite converter topology C operation modes                                                                                                                  | 61 |

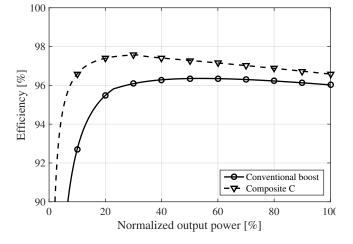

| 3.14 | Modeled efficiency of composite C converter                                                     | 63 |

|------|-------------------------------------------------------------------------------------------------|----|

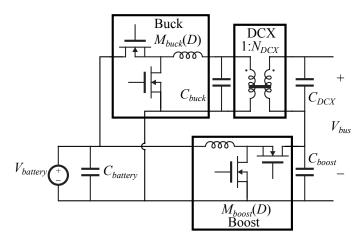

|      | Composite converter topology D                                                                  | 64 |

|      |                                                                                                 |    |

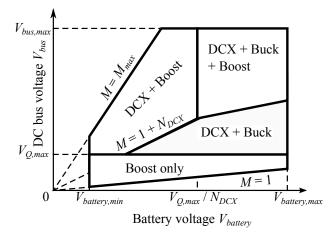

| 3.16 | Composite converter D operating modes                                                           | 65 |

| 3.17 | Modeled efficiency of composite D converter                                                     | 66 |

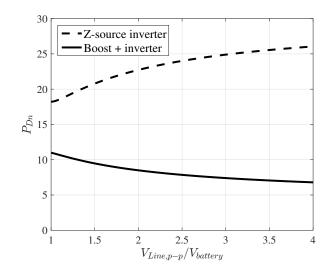

| 3.18 | Specified device power rating comparison between Z-source inverter and conventional             |    |

|      | boost cascaded with inverter approach                                                           | 68 |

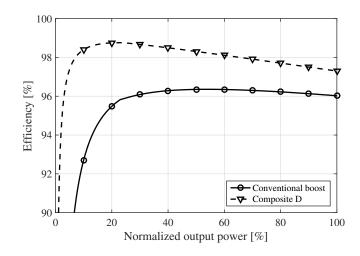

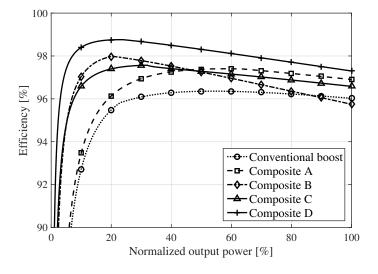

| 3.19 | Comparison of predicted composite converter efficiencies at fixed $200\mathrm{V}$ input voltage |    |

|      | and $650 \mathrm{V}$ output voltage                                                             | 71 |

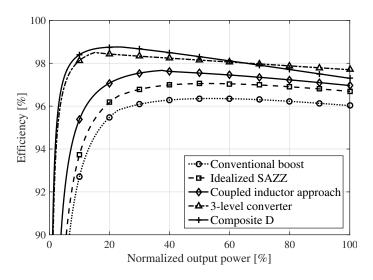

| 3.20 | Boost converter efficiency comparison of different approaches with fixed $200 \mathrm{V}$ input |    |

|      | and $650 \mathrm{V}$ output                                                                     | 71 |

| 4.1  | Dual Active Bridge (DAB) schematic                                                              | 79 |

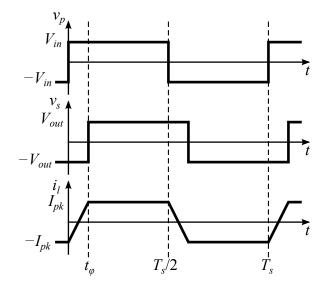

| 4.2  | Simplified DAB operation waveform                                                               | 79 |

| 4.3  | DAB schematic with secondary side passive rectification                                         | 80 |

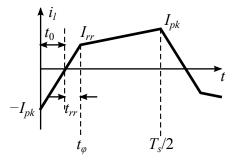

| 4.4  | Simplified tank inductor current waveform of DCX                                                | 81 |

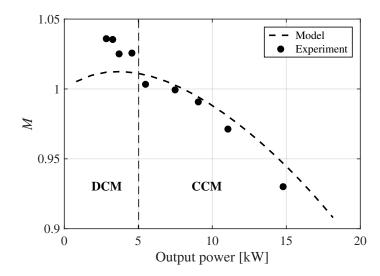

| 4.5  | Normalized DCX voltage conversion ratio model and measurement                                   | 83 |

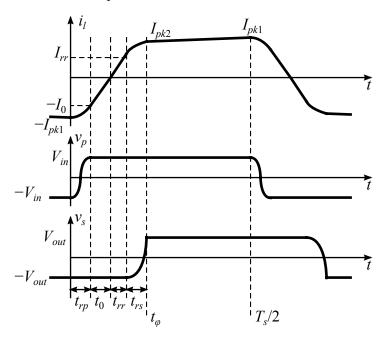

| 4.6  | Detailed DCX operation waveform                                                                 | 84 |

| 4.7  | DCX equivalent circuits during commutation                                                      | 85 |

| 4.8  | DCX state plane plots                                                                           | 86 |

| 4.9  | DCX state plane trajectory at hard switching                                                    | 87 |

| 4.10 | DCX detailed equivalent circuit at primary side commutation                                     | 88 |

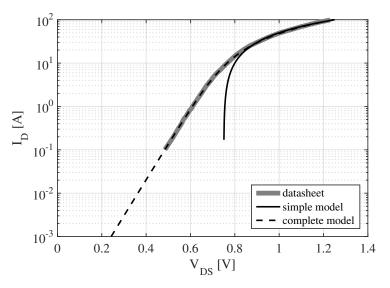

| 4.11 | Comparison of different diode models                                                            | 91 |

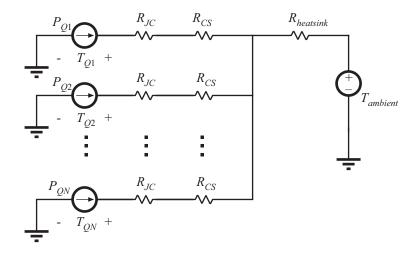

| 4.12 | Simple device thermal circuit model                                                             | 92 |

| 4.13 | DCX inductor and transformer flux density sketch                                                | 94 |

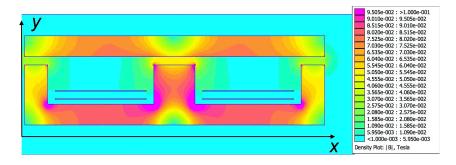

| 4.14 | DCX planar tank inductor flux density plot in 2D FEA                                            | 95 |

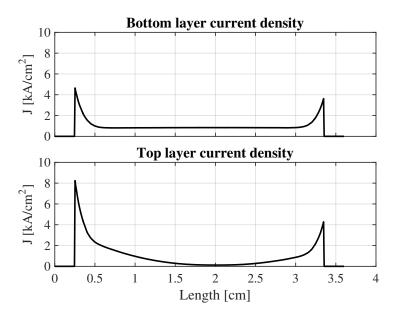

| 4.15 | DCX planar tank inductor winding current density plot in 2D FEA                                 | 96 |

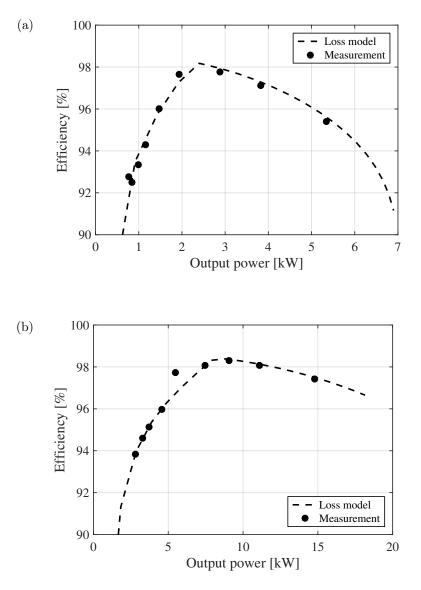

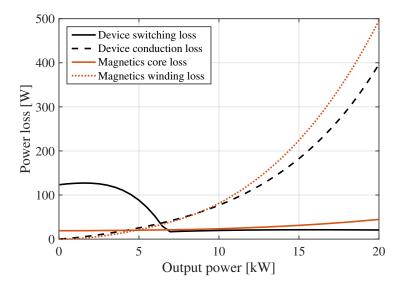

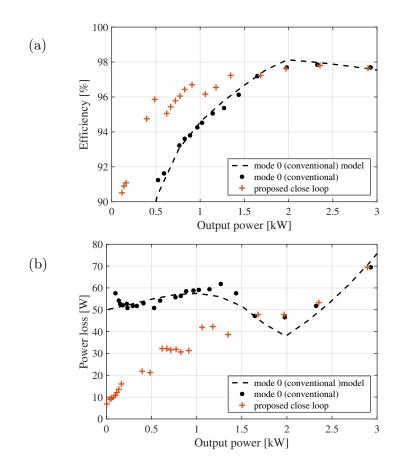

| 4.16 | DCX loss model and measurement comparison                                                       | 98 |

| 4.17 | Modeled DCX prototype loss breakdown                                                              |

|------|---------------------------------------------------------------------------------------------------|

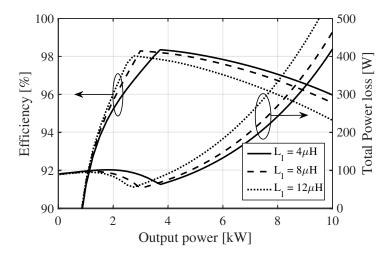

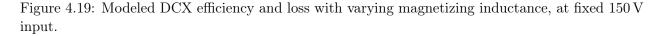

| 4.18 | Modeled DCX efficiency and loss with varying tank inductance                                      |

| 4.19 | Modeled DCX efficiency and loss with varying magnetizing inductance                               |

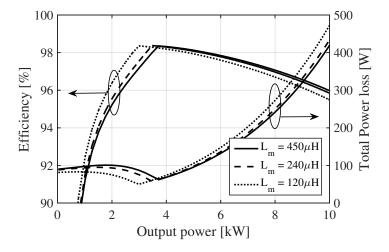

| 4.20 | Modeled DCX efficiency and loss with DAB operation                                                |

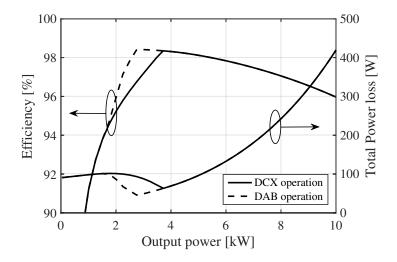

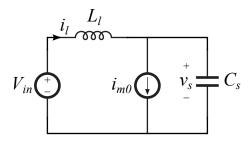

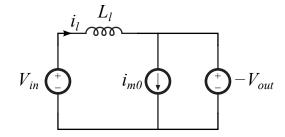

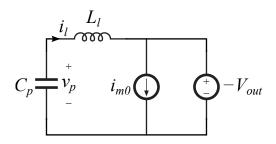

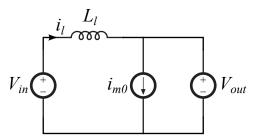

| 4.21 | Equivalent resonant tank circuit during the proposed resonant transition 103                      |

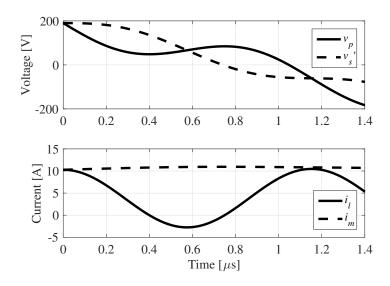

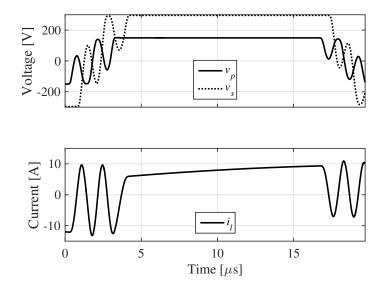

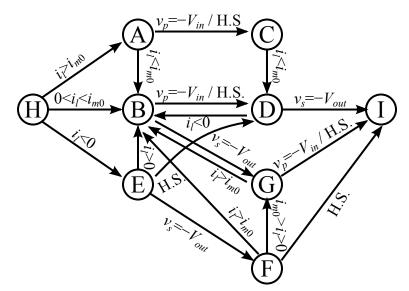

| 4.22 | Simulated <i>LLCC</i> resonance transient                                                         |

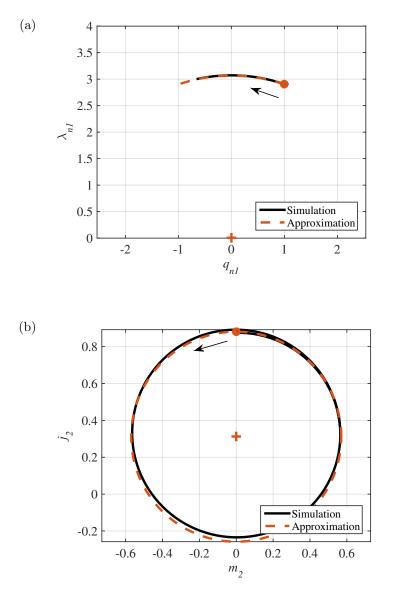

| 4.23 | Simulated and analytically approximated state plane trajectory of the $LLCC$ reso-                |

|      | nance tank                                                                                        |

| 4.24 | SPICE simulation of DCX in resonant mode 0                                                        |

| 4.25 | SPICE simulation of DCX in resonant mode 1                                                        |

| 4.26 | SPICE simulation of DCX in resonant mode 2                                                        |

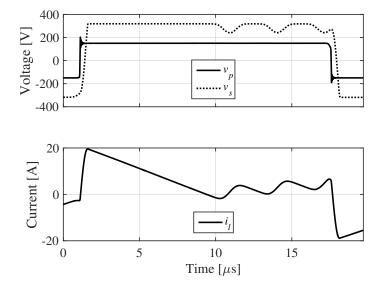

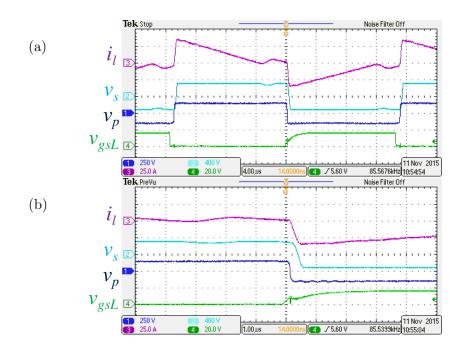

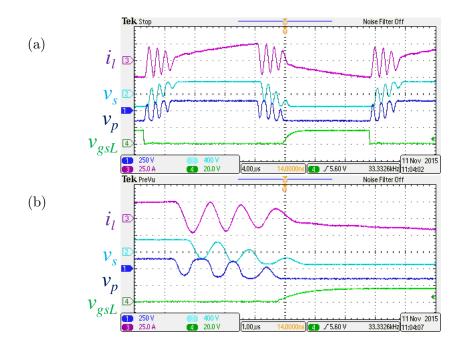

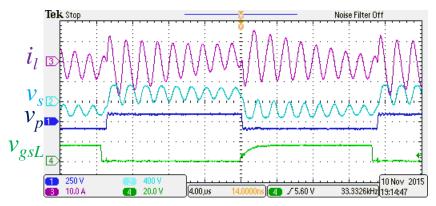

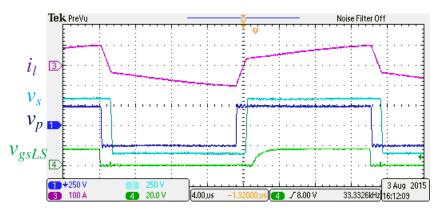

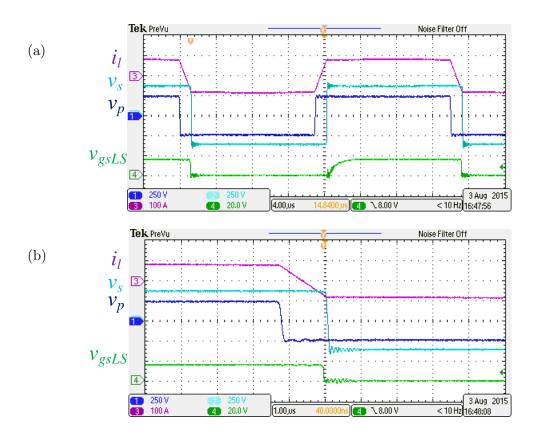

| 4.27 | $20\mathrm{kW}$ DCX prototype light load measurement in resonant mode 0 (conventional             |

|      | approach)                                                                                         |

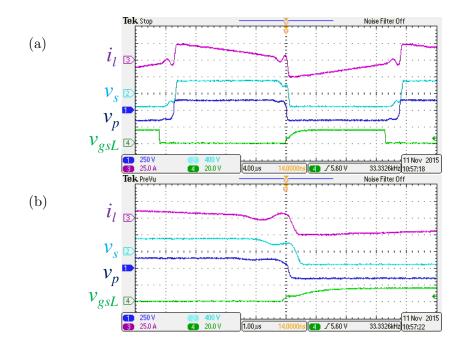

| 4.28 | 20 kW DCX prototype light load measurement in resonant mode 1 $\ldots \ldots \ldots \ldots 110$   |

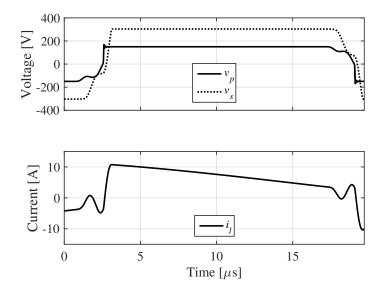

| 4.29 | 20 kW DCX prototype light load measurement in resonant mode 2 $\ldots \ldots \ldots \ldots 111$   |

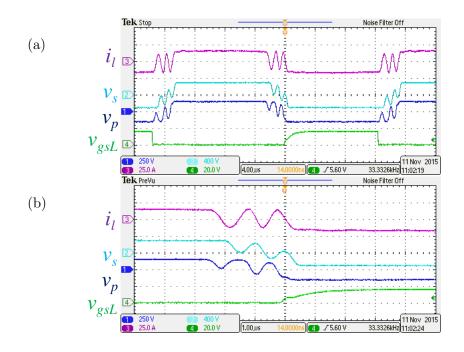

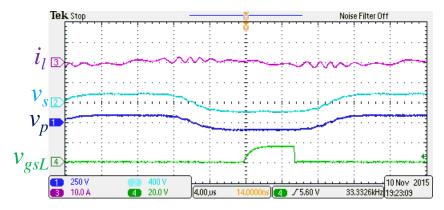

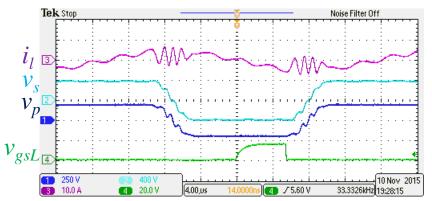

| 4.30 | 20 kW DCX prototype light load measurement in resonant mode 3 $\ldots$                            |

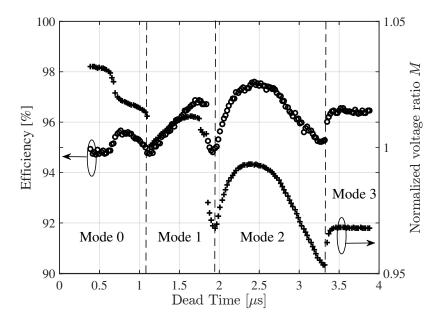

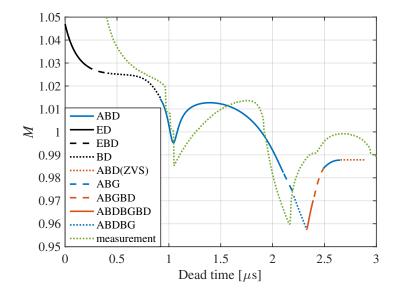

| 4.31 | Measured DCX voltage conversion ratio and efficiency versus dead time $\ . \ . \ . \ . \ . \ 112$ |

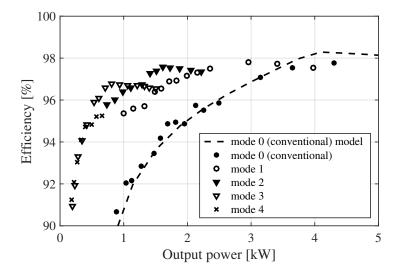

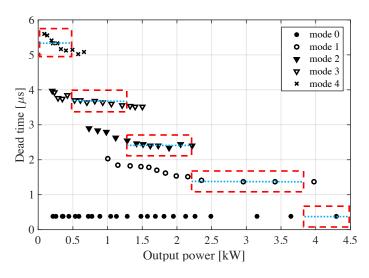

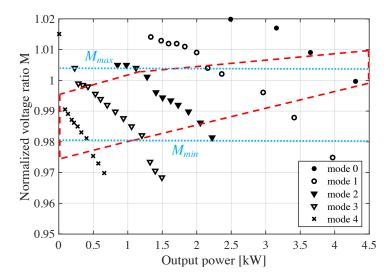

| 4.32 | Measured DCX peak efficiency versus output power at different modes $\ldots \ldots \ldots 113$    |

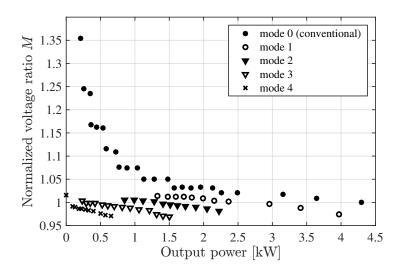

| 4.33 | Measured DCX normalized voltage conversion ratio versus output power, at the op-                  |

|      | timum efficiency points                                                                           |

| 4.34 | No-load operation in conventional mode 0                                                          |

| 4.35 | No-load operation in mode 5                                                                       |

| 4.36 | No-load operation with maximum input voltage                                                      |

| 4.37 | Peak efficiency dead time in each mode                                                            |

| 4.38 | Zoom in of Fig. 4.4.3.1                                                                           |

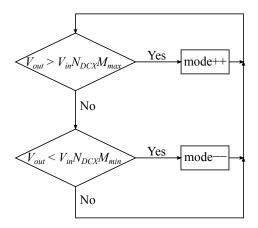

| 4.39 | Proposed simple approximate optimum efficiency trajectory control decision diagram 118            |

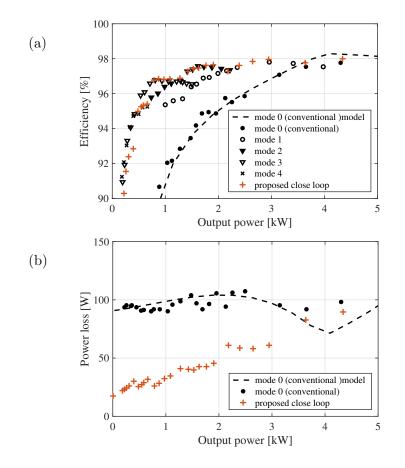

| 4.40 | Measured DCX close loop operation at nominal input                                                |

| 4.41 | Measured DCX close loop operation at maximum input                                                                                                                    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.42 | Measured DCX close loop operation at minimum input                                                                                                                    |

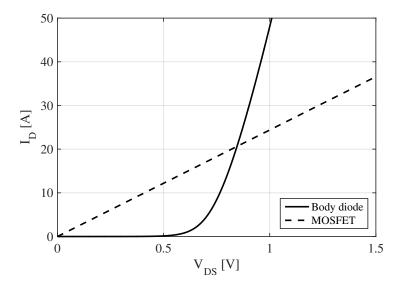

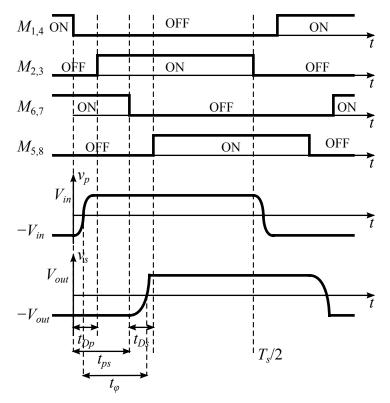

| 4.43 | DAB operation with passive phase shift control                                                                                                                        |

| 4.44 | MOSFET channel conduction versus body diode conduction                                                                                                                |

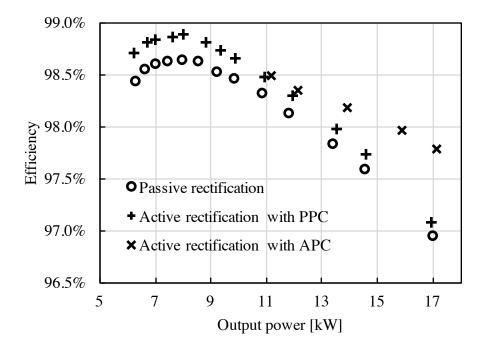

| 4.45 | Efficiency comparison of passive rectification and different active rectifications 123                                                                                |

| 4.46 | DAB operation with active phase shift control                                                                                                                         |

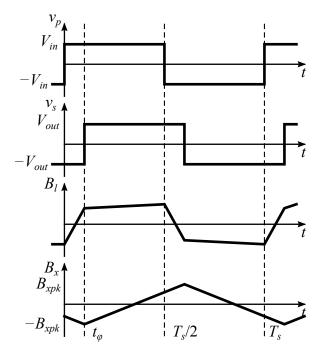

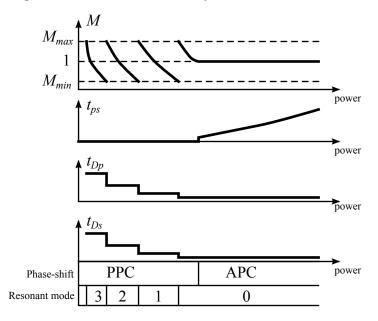

| 4.47 | Timing diagram of efficiency-enhanced DAB control                                                                                                                     |

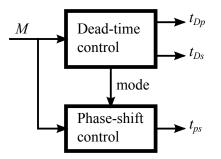

| 4.48 | Modes in efficiency-enhanced DAB control                                                                                                                              |

| 4.49 | Efficiency-enhanced DAB control block diagram                                                                                                                         |

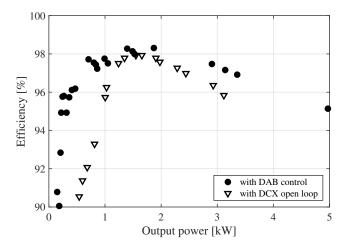

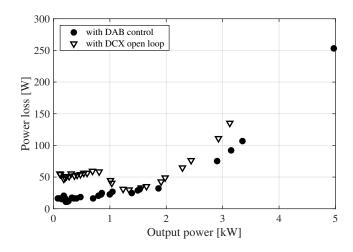

| 4.50 | Measured efficiency comparison of open loop operation and DAB close loop operation,                                                                                   |

|      | at fixed 100 V input voltage                                                                                                                                          |

| 4.51 | Measured power loss comparison of open loop operation and DAB loop operation, at                                                                                      |

|      | fixed 100 V input voltage                                                                                                                                             |

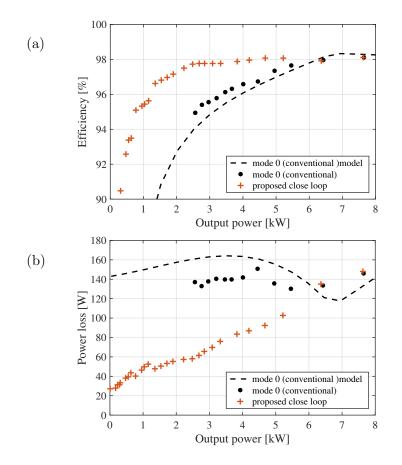

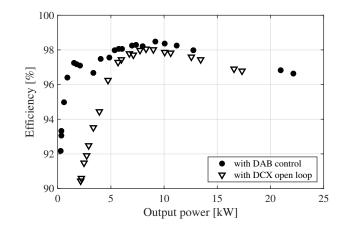

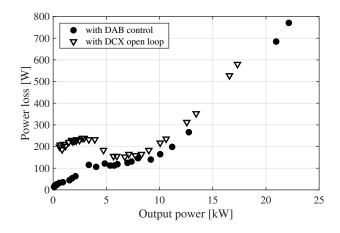

| 4.52 | Measured efficiency comparison of open loop operation and DAB close loop operation,                                                                                   |

|      | at fixed 250 V input voltage                                                                                                                                          |

| 4.53 | Measured power loss comparison of open loop operation and DAB loop operation, at                                                                                      |

|      | fixed 250 V input voltage                                                                                                                                             |

| 5.1  | Converter efficiency comparison at fixed 5 kW output power                                                                                                            |

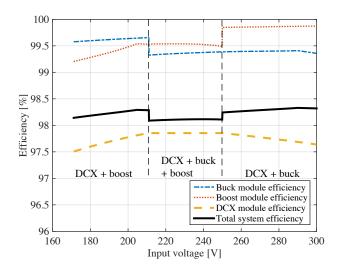

|      | Calculated converter module efficiency and total system efficiency                                                                                                    |

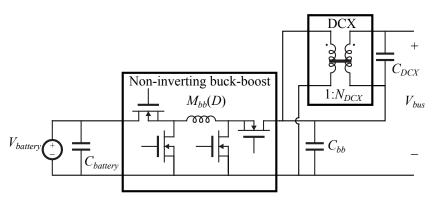

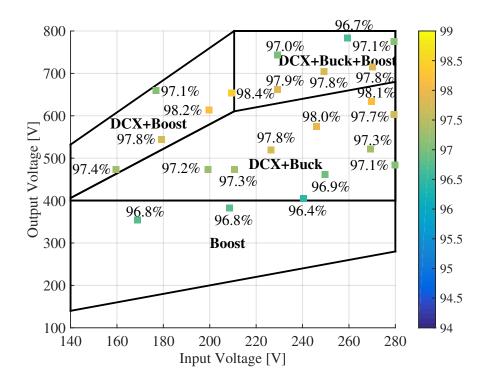

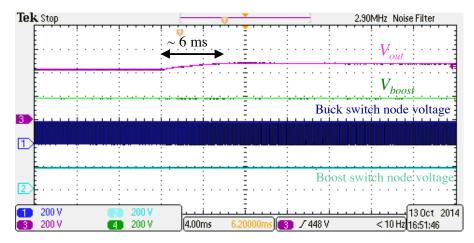

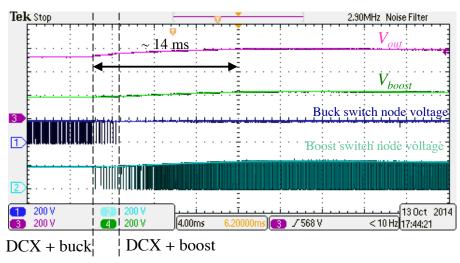

| 5.3  | Composite converter operation in DCX + Boost mode $\dots \dots \dots$ |

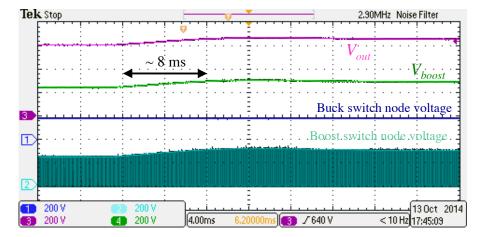

| 5.4  | Composite converter operation in DCX + Buck mode                                                                                                                      |

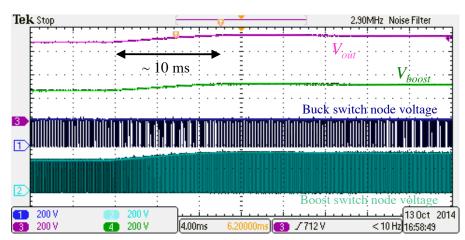

| 5.5  | Composite converter operation in DCX + Buck + Boost mode                                                                                                              |

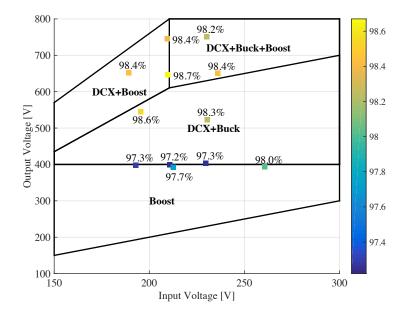

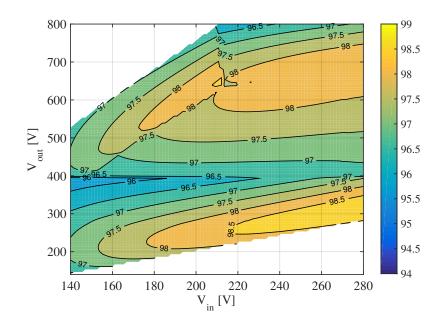

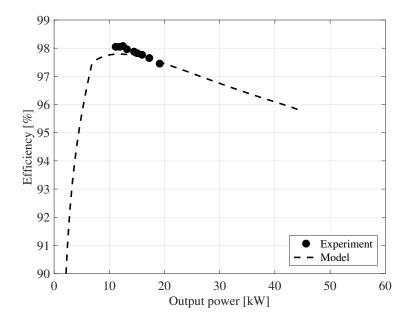

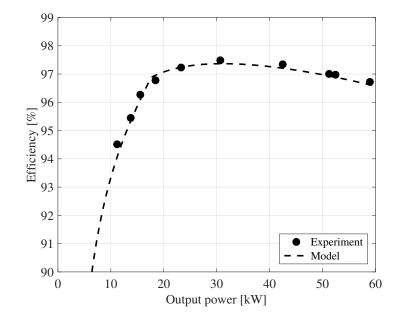

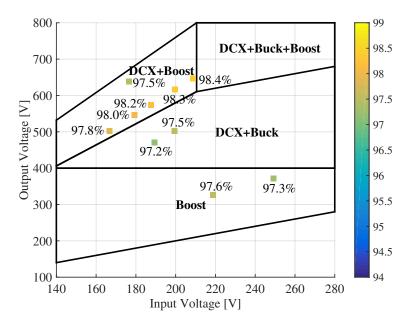

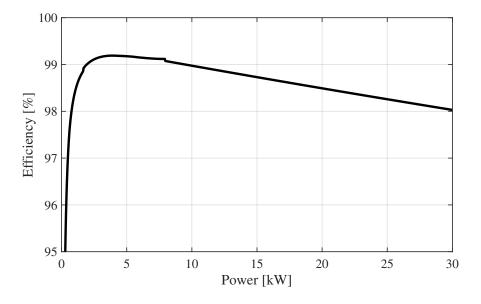

| 5.6  | Measured composite converter efficiency vs. $V_{in} \& V_{out}$ , at $P_{out} = 5 \mathrm{kW} \ldots \ldots 142$                                                      |

|      |                                                                                                                                                                       |

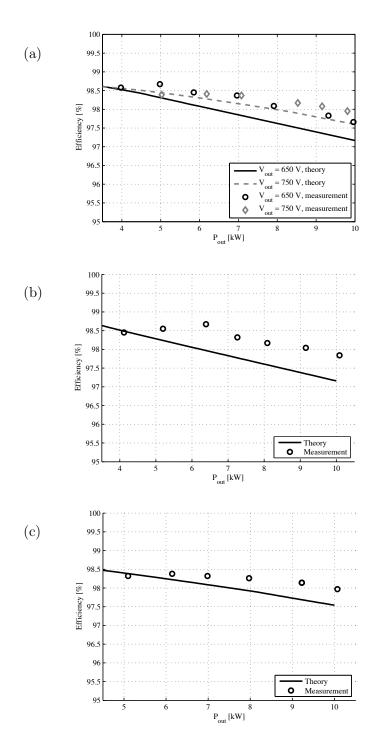

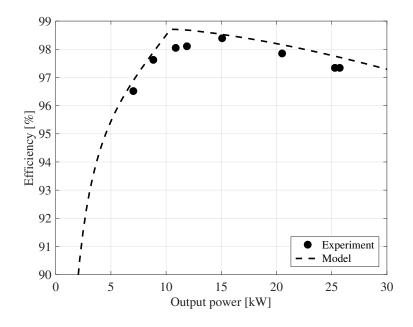

| 5.7  | Measured converter efficiency vs. output power                                                                                                                        |

| 5.8  | Comparison of 20 kVA DCX transformer design with Litz wire winding and PCB                                                                                            |

|      | winding                                                                                                                                                               |

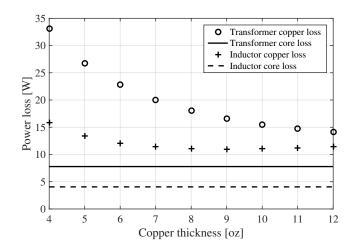

| 5.9  | DCX magnetics loss versus copper thickness                                                 | 148 |

|------|--------------------------------------------------------------------------------------------|-----|

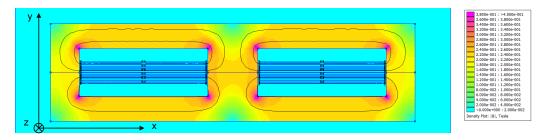

| 5.10 | Magnetic flux density plot of the 2-D FEA on the designed planar DCX transformer           | 148 |

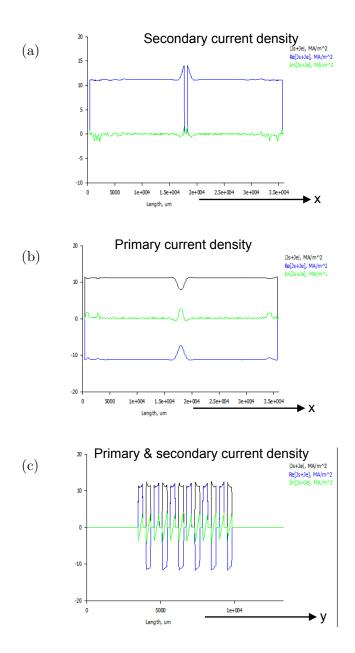

| 5.11 | Current density plots of the 2-D FEA on the designed planar DCX transformer                | 149 |

| 5.12 | (a) Schematic of DCX with asymmetrical tank inductor. (b) Transformer inter-               |     |

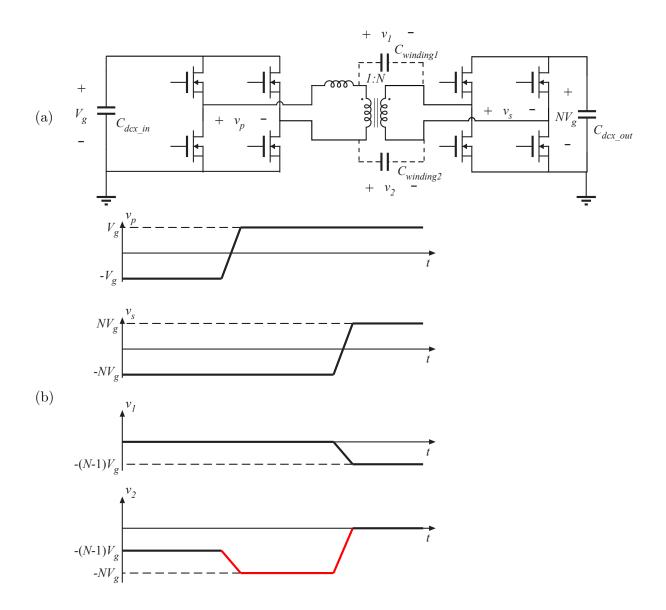

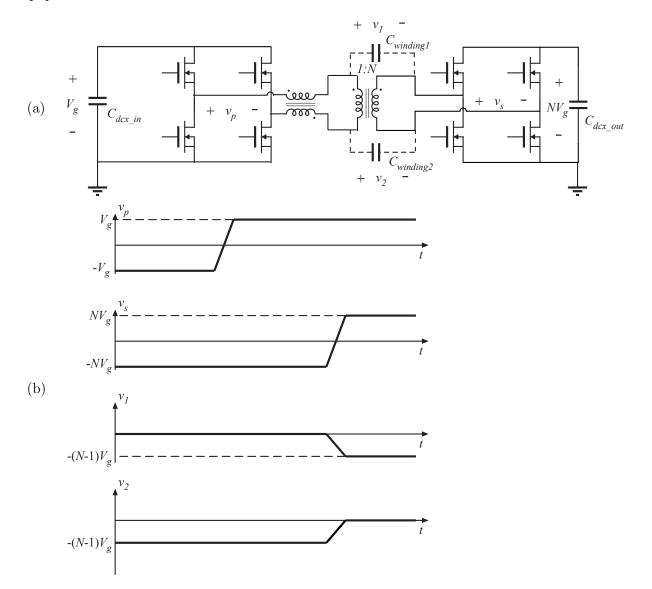

|      | winding capacitor voltage waveforms.                                                       | 151 |

| 5.13 | A symmetrical tank inductor: (a) DCX schematic; (b) transformer inter-winding              |     |

|      | capacitor voltage waveform.                                                                | 152 |

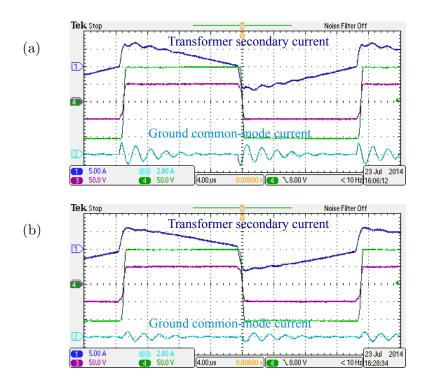

| 5.14 | Experimental DCX waveforms with symmetrical and asymmetrical tank inductor                 | 153 |

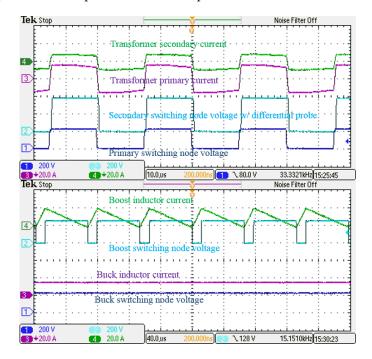

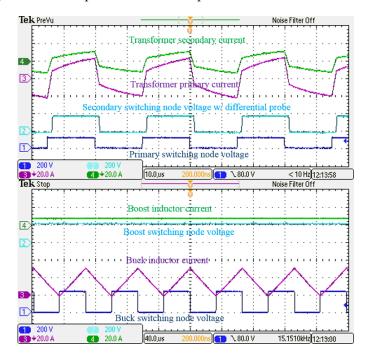

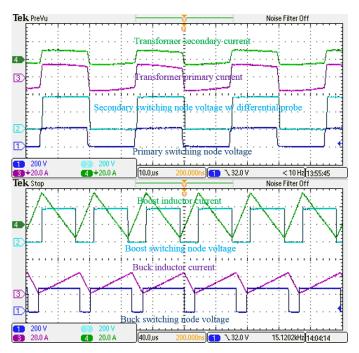

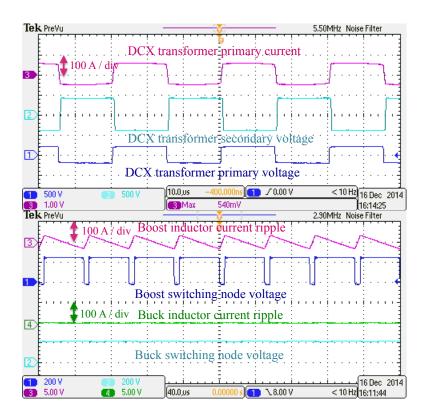

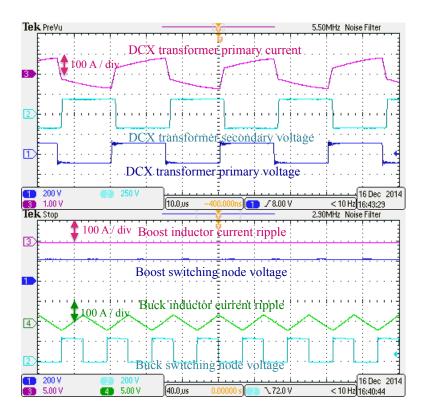

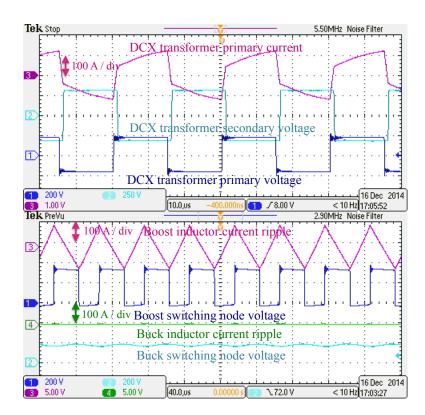

| 5.15 | 30 kW prototype medium load operation waveform                                             | 155 |

| 5.16 | 30 kW prototype light load operation waveform                                              | 156 |

| 5.17 | 30 kW prototype full load operation waveform                                               | 157 |

| 5.18 | 30 kW system measured efficiency as a function of output power                             | 157 |

| 5.19 | 30 kW system measured efficiency at fixed 15 kW output power $\hdots$                      | 158 |

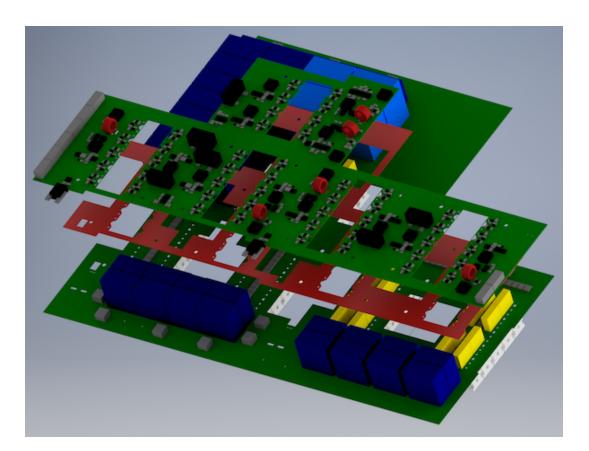

| 5.20 | 30 kW prototype second revision PCB stacking                                               | 160 |

| 5.21 | 30 kW prototype second revision photo                                                      | 161 |

| 5.22 | Measured efficiency of the $30\mathrm{kW}$ prototype, with efficiency-enhanced DAB control |     |

|      | enabled                                                                                    | 162 |

| 5.23 | Measured power loss of the $30\mathrm{kW}$ prototype, with efficiency-enhanced DAB control |     |

|      | enabled                                                                                    | 162 |

| 5.24 | Predicted composite converter energy loss distribution under different driving profiles.   | 163 |

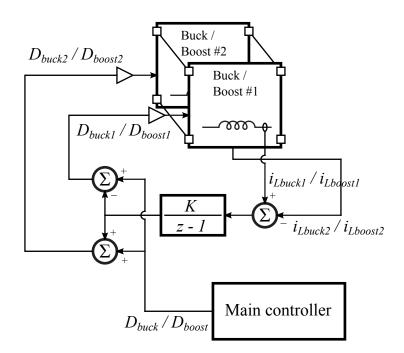

| 5.25 | $60\mathrm{kW}$ module system configuration, using parallel phase-shifted modules          | 165 |

| 5.26 | Modeled 60 kW system efficiency at fixed 30 kW output power, with different input $/$      |     |

|      | output voltages                                                                            | 165 |

| 5.27 | Block diagram of the current balancing control algorithm                                   | 166 |

| 5.28 | Interleaved boost converter operation waveforms with and without current balancing         |     |

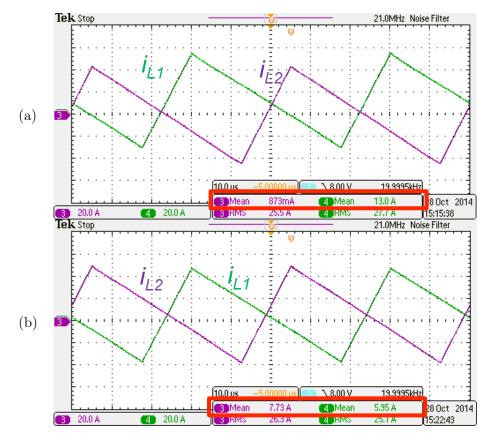

|      | algorithm                                                                                  | 168 |

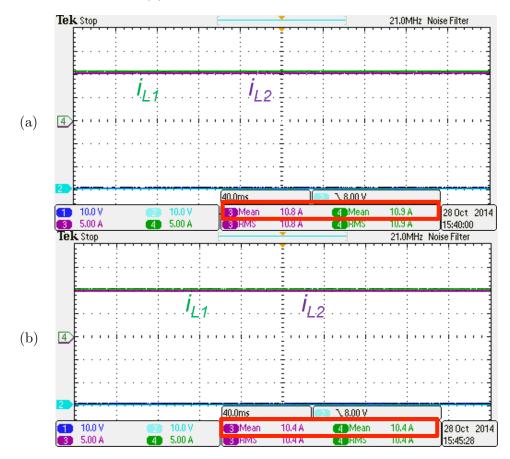

| 5.29 | Boost converter module current balancing in pass-through mode                              | 169 |

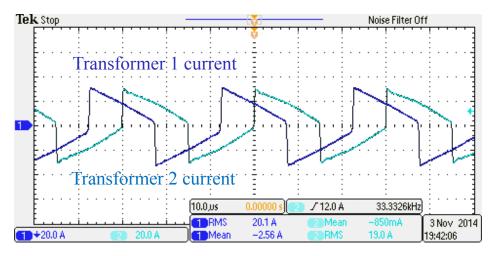

| 5.30 | Two interleaved DCXs naturally balance their transformer current                                                                                                          |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

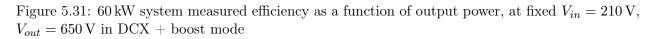

| 5.31 | $60\mathrm{kW}$ system measured efficiency as a function of output power, in DCX $+$ boost                                                                                |

|      | mode                                                                                                                                                                      |

| 5.32 | $60\mathrm{kW}$ system measured efficiency as a function of output power, in the DCX $+$ buck                                                                             |

|      | mode                                                                                                                                                                      |

| 5.33 | $60\mathrm{kW}$ system measured efficiency as a function of output power, in the DCX $+$ boost                                                                            |

|      | mode                                                                                                                                                                      |

| 5.34 | $60\mathrm{kW}$ system measured efficiency at different input / output voltages in different                                                                              |

|      | modes, with fixed 30 kW output power                                                                                                                                      |

| 5.35 | Predicted efficiency of composite converter A with $900\mathrm{V},$ at fixed $250\mathrm{V}$ input and                                                                    |

|      | 650 V output                                                                                                                                                              |

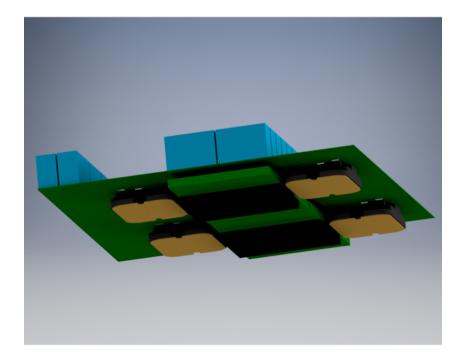

| 5.36 | CAD rendering of the composite A converter power stage design with SiC devices 177 $$                                                                                     |

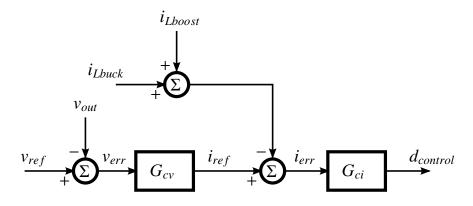

| 6.1  | The block diagram of the main control loop using average current control structure . 180                                                                                  |

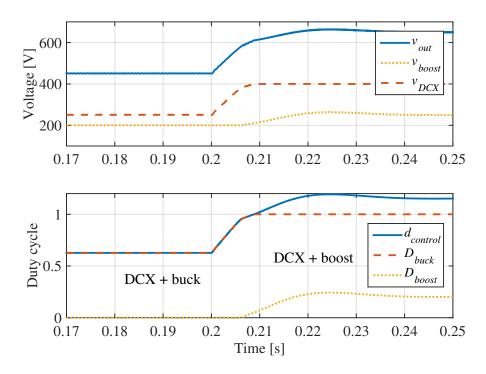

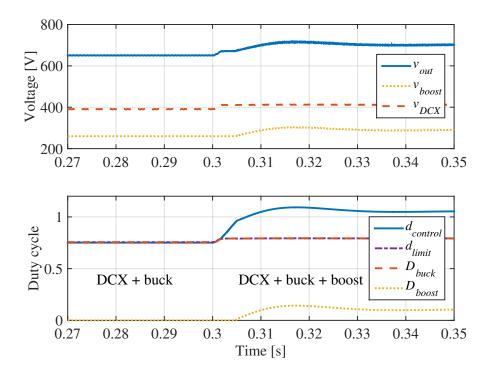

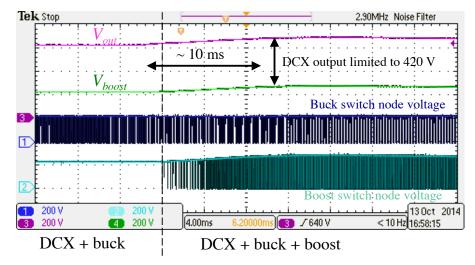

| 6.2  | Simulated DCX + buck to DCX + boost mode transition $\dots \dots \dots$   |

| 6.3  | The block diagram of the DCX voltage limit block, which leads to DCX + buck +                                                                                             |

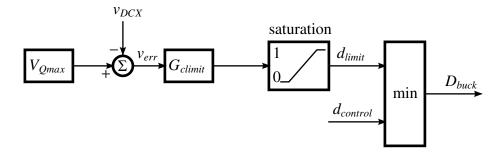

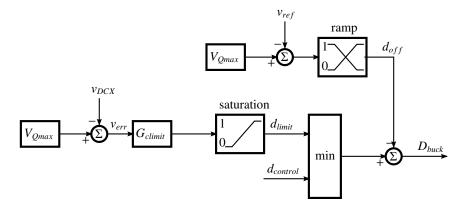

|      | boost mode of operation                                                                                                                                                   |

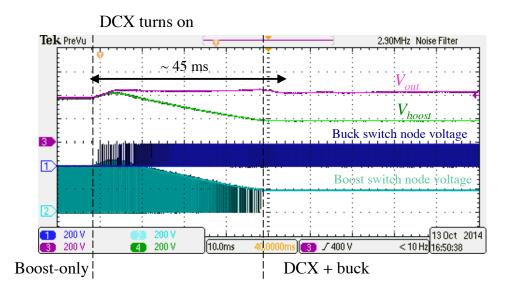

| 6.4  | Simulated DCX + buck to DCX + buck + boost transition $\dots \dots \dots$ |

| 6.5  | The block diagram of DCX voltage limit block with added buck-off block, which                                                                                             |

|      | forces the system into the Boost-only mode                                                                                                                                |

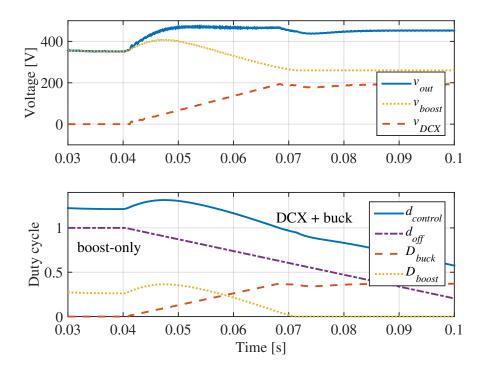

| 6.6  | Simulated boost-only to DCX + buck transition                                                                                                                             |

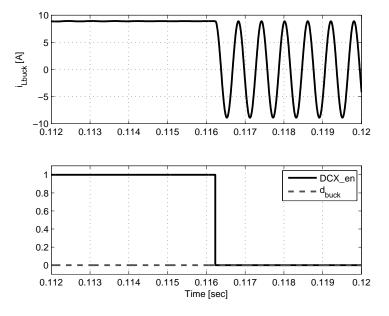

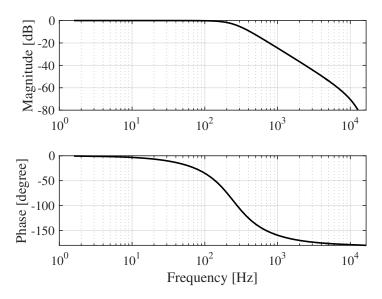

| 6.7  | Buck inductor current ringing after DCX turns off                                                                                                                         |

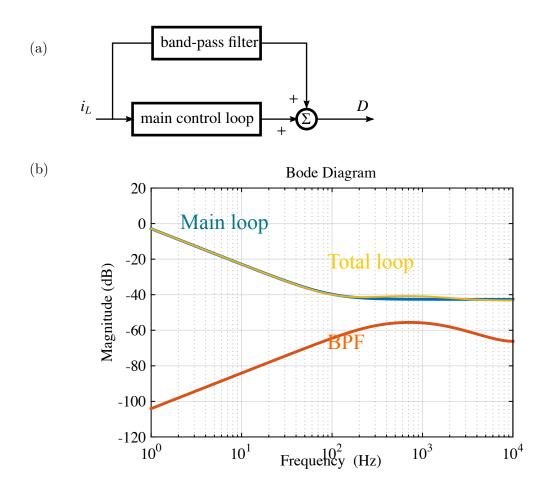

| 6.8  | (a) Extra band-pass-filter current feedback loop that damps out the converter mod-                                                                                        |

|      | ule in pass-through or shut-down mode. (b) The total current loop controller gain                                                                                         |

|      | frequency response, with the presence of extra band-pass-filter                                                                                                           |

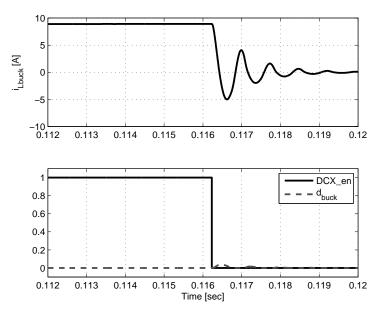

| 6.9  | With auxiliary band-pass filter current loop, the buck inductor current ringing is                                                                                        |

|      | suppressed                                                                                                                                                                |

| 6.10 | The block diagram of the full controller                                                                                                           | 189 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.11 | Transient waveforms with the output voltage reference step from $300 \text{ V}$ to $350 \text{ V}$ , at                                            |     |

|      | $V_{in} = 180 \mathrm{V}$ , and approximately $1.9 \mathrm{kW}$ output power. The system is in the boost-                                          |     |

|      | only mode.                                                                                                                                         | 191 |

| 6.12 | Transient waveforms with the output voltage reference step from $420\mathrm{V}$ to $470\mathrm{V}$ , at                                            |     |

|      | $V_{in} = 180$ V, and approximately 4.3 kW output power. The system is in the DCX +                                                                |     |

|      | buck mode.                                                                                                                                         | 191 |

| 6.13 | Transient waveforms with the output voltage reference step from $600 \text{ V}$ to $650 \text{ V}$ , at                                            |     |

|      | $V_{in} = 180$ V, and approximately 9.5 kW output power. The system is in the DCX +                                                                |     |

|      | boost mode                                                                                                                                         | 192 |

| 6.14 | Transient waveforms with the output voltage reference step from $670\mathrm{V}$ to $720\mathrm{V}$ , at                                            |     |

|      | $V_{in} = 220 \mathrm{V}$ , and approximately 11.3 kW output power. The system is in the DCX                                                       |     |

|      | $+ buck + boost mode. \dots \dots$           | 192 |

| 6.15 | Transient waveforms for an output voltage reference step from $520\mathrm{V}$ to $580\mathrm{V}$ , at                                              |     |

|      | $V_{in} = 180\mathrm{V},$ and around 7.3 kW output power. The system transitions from DCX $+$                                                      |     |

|      | buck mode to $DCX + boost mode. \dots \dots$ | 193 |

| 6.16 | Transient waveforms for a output voltage reference step from $620\mathrm{V}$ to $670\mathrm{V}$ , at                                               |     |

|      | $V_{in} = 220$ V, and around 9.4 kW output power. The system transitions from DCX +                                                                |     |

|      | buck mode to $DCX + buck + boost mode.$                                                                                                            | 194 |

| 6.17 | Transient waveforms for the output voltage reference step from $370\mathrm{V}$ to $420\mathrm{V}$ , at                                             |     |

|      | $V_{in} = 180 \mathrm{V}$ , and around 3.2 kW output power. The system transitions from boost-                                                     |     |

|      | only mode to DCX + buck mode                                                                                                                       | 194 |

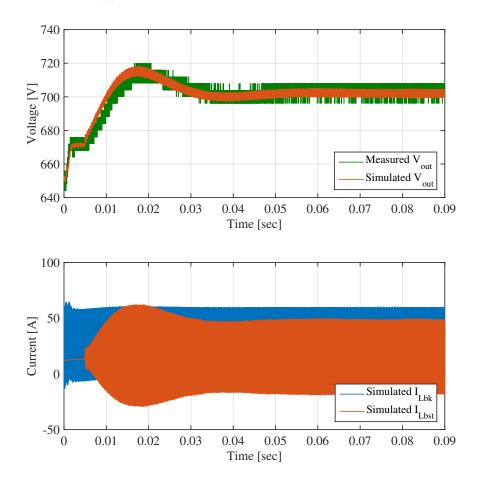

| 6.18 | Simulation vs. experimental results for the output voltage reference step from $650\mathrm{V}$                                                     |     |

|      | to 700 V, with 260 V input voltage, and around 9.6 kW output power. The measured                                                                   |     |

|      | oscilloscope data (green waveform) is affected by the oscilloscope limited resolution                                                              | 196 |

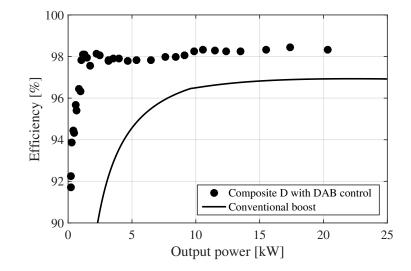

| 7.1  | Measured   | effic | iency  | of   | the  | 30   | kW   | pro   | otot | ype | э, ч | wit                  | h e | effic | cier | ncy | -ei | ιhε | anc | ed | D. | AE | 3 c | or | ntro | ol |     |

|------|------------|-------|--------|------|------|------|------|-------|------|-----|------|----------------------|-----|-------|------|-----|-----|-----|-----|----|----|----|-----|----|------|----|-----|

|      | enabled    |       |        |      |      |      |      |       |      | •   |      |                      |     | •     |      |     |     |     |     | •  |    | •  |     | •  | •    |    | 200 |

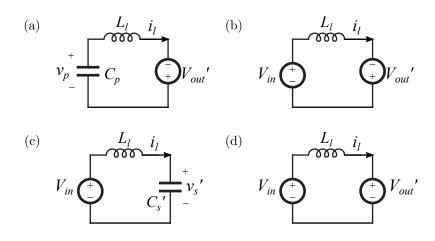

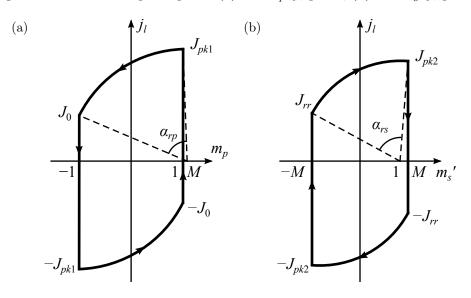

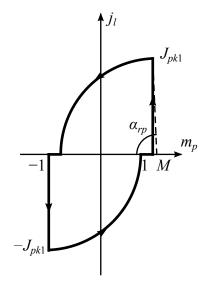

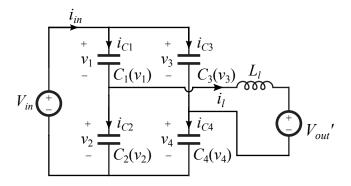

| A.1  | State A    |       |        |      |      |      |      |       |      | • • |      |                      |     |       |      |     |     | •   |     | •  |    | •  |     |    |      |    | 214 |

| A.2  | State B    |       |        |      |      |      |      |       |      | •   |      |                      |     | •     |      |     |     |     |     |    |    |    |     |    |      |    | 215 |

| A.3  | State C    |       |        |      |      |      |      |       |      |     |      |                      |     |       |      |     |     |     |     |    |    |    |     | •  |      |    | 216 |

| A.4  | State D    |       |        |      |      |      |      |       |      | •   |      |                      |     | •     |      |     |     |     |     |    |    |    |     |    |      |    | 216 |

| A.5  | State E    |       |        |      |      |      |      |       |      | ••• |      |                      |     | •     |      |     |     |     |     |    |    |    |     |    |      |    | 217 |

| A.6  | State F    |       |        |      |      |      |      |       |      | • • |      |                      |     | •     |      |     |     |     |     |    |    |    |     |    |      |    | 217 |

| A.7  | State G    |       |        |      |      |      |      |       |      |     |      |                      |     |       |      |     |     | •   |     |    |    | •  |     | •  |      |    | 218 |

| A.8  | State H    |       |        |      |      |      |      |       |      |     |      |                      |     |       |      |     |     | •   |     |    |    | •  |     | •  |      |    | 218 |

| A.9  | State I .  |       |        |      |      |      |      |       |      |     |      |                      |     |       |      |     |     | •   |     |    |    | •  |     | •  |      |    | 219 |

| A.10 | State tran | sitio | n dia  | grai | m .  |      |      |       |      | •   |      |                      |     | •     |      |     |     |     |     |    |    |    |     |    |      |    | 219 |

| A.11 | Resonant   | trans | sition | an   | alyt | ical | mo   | del   | an   | d n | nea  | $\operatorname{sur}$ | en  | nen   | t c  | om  | pa  | ris | on. | •  |    | •  |     |    |      |    | 220 |

| B.1  | Frequency  | resp  | onse   | of   | the  | digi | ital | filte | er.  | •   |      |                      |     |       |      |     |     |     |     | •  |    |    |     |    |      |    | 235 |

## Chapter 1

#### **Electrified Automotive Powertrain Overview**

The fossil-based fuel has been the dominant energy source for transportation over the last century. However, as the number of vehicles growing rapidly, the related issues are becoming evident, such as green house gas emission, air pollution, and the danger of oil resources depletion in the near future. One solution is to improve the fuel economy, which include improve the internal combustion engine (ICE) efficiency, reduce the vehicle air drag, improve the transmission and wheel efficiency, and/or utilize the hybrid electric vehicle (HEV) technology. On the other hand, obviously, the more thorough solution is to find alternative sustainable energy sources, such as fuel cell electric vehicle (FCEV). Solutions such as battery-powered electric vehicle (BEV) or plug-in hybrid electric vehicle (PHEV) can either improve the fuel economy or as an alternative energy source solution, depending on how the electricity is generated. Other than improving the efficiency of the existing ICE-powered vehicle, all the other approaches (HEV, PHEV, FCEV, BEV) involves the electrified automotive powertrain, and they are referred as electric vehicle (EV) in general.

Although EV was invented early as in 1834 [17], it was quickly taken over by ICE-powered vehicles in the 19th century, due to the big breakthrough in ICE technology. The research and developments of power train electrification are revived since the 90s [16,18], mainly due to environmental concerns, and government policies. For example, the California air resource board (CARB) passed the zero emission vehicle (ZEV) mandate in 1990, which required that by 1998, 2% of the vehicles sold in California to be ZEV, and this portion has to be increased to 10% by 2003. Since the late 90s, the modern HEVs debuted the automobile market [73]. HEVs are well accepted by the

$\mathbf{2}$

market, and their sales keep growing since then. It is predicted that by 2020, 20% of the annual vehicle sales are comprised by HEVs [81]. Nowadays many major automotive manufacturers such as Toyota, Honda, Ford, GM, and BMW, offer EV options in their production line.

However, there is still a long way to go in the EV development. Comparing with the conventional ICE-powered vehicle, the market share of HEV is still relatively small. On the other hand, in terms of sustainable energy, HEV is only an intermediate solution. The market acceptance of ultimate ZEV solutions, such as BEVs or FCEVs, is still not as good as expected. To further push the EV technology and expand the EV market, the industry is looking for future disruptive technologies that can further extend the vehicle drive range, improve the fuel economy, as well as reduce the production cost [68].

This chapter overviews the EV technology from a general perspective, and discusses about the requirements for the power electronics in the powertrain of EV, from the system point of view. Section 1.1 overviews different type of EV powertrain architectures. Section 1.2 gives brief descriptions on the functions of power electronics in electrified powertrain. In section 1.3, the specific power electronics characteristics in electrified powertrain applications are discussed. In section 1.4, a detailed electric vehicle powertrain model is introduced. Based on this model, several driving profiles in standard vehicle tests are simulated, and the load characteristics of the dc-dc converter for powertrain is extracted. These requirements serve as the basic guidance for all the designs in this work.

#### **1.1** Powertrain architecture overview

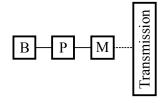

Figure 1.1: Battery electric vehicle (BEV) powertrain architecture. B: battery, P: power electronics module, M: motor. Solid lines: electrical connection. Dotted line: mechanical connection.

All the vehicles involves traction systems, energy sources, and the power controls that regulate the power flow. In general, as long as electric system is involved in the powertrain, the vehicle can be regarded as electric vehicle (EV). As mentioned previously, based on different energy sources, the EVs can be categorized into different technologies, such as battery electric vehicles (BEV), hybrid electric vehicles (HEV), and fuel cell electric vehicle (FCEV). Different vehicles can adopt very different powertrain architectures. In this section, some basic architectures are reviewed.

#### 1.1.1 Battery Electric Vehicle (BEV)

BEV utilizes battery as the only energy source, which has to be charged externally. If the charging electricity is generated from renewable energy sources, such as solar or wind power, the use of BEV leaves almost zero carbon footprint. However, even the electricity is generated from fossil-fuel based power plant, its carbon footprint is still much smaller than that of the traditional fossil-fuel based vehicle, because the energy conversion efficiency of the power plant is much higher than that of the vehicular ICE.

Similar to the miles-per-gallon (MPG) metric of the conventional ICE-powered vehicle, to quantify the energy consumption of BEV, the metric of miles-per-gallon-equivalent (MPGe) is introduced by the United States Environmental Protection Agency (EPA). The MPGe counts the vehicle energy consumption from the ac grid, and it is defined as:

$$1 \,\mathrm{MPGe} \approx 0.029\,67 \,\mathrm{miles/kWh}$$

(1.1)

The average combined fuel economy of the conventional ICE-powered vehicle made in 2016 is around 25 MPG, and even the most fuel economic vehicle has under 40 MPG. In contrast, the BEV can easily have more than 100 MPGe.

A typical battery electric vehicle (BEV) power train architecture is sketched in Fig. 1.1. Usually a single battery pack supplies the energy. The energy is processed by some power electronics unit to drive the electric motor. Because the electric motor can operate in a much wider speed / torque range than ICE, fixed gear ratio can be used in the transmission, which simplifies the transmission design and improves the transmission efficiency. Some BEV uses two motors to drive front and rear wheels separately, which provides extra flexibility and mobility. Ideally four wheels can have independent motor drives, which even eliminates the need for differential gears.

In the early histories of BEV, dc machines are used as the traction motor, because it is very easy to control. In modern BEV, dc motor is rarely used due to the reliability issue of the electric brush. Instead, ac machines such as induction machine (IM) or permanent magnet synchronous machine (PMSM) are used. Comparing PMSM with IM, IM usually has simpler construction therefore costs less to build. However, it exhibits slightly lower efficiency comparing with PMSM, due to extra rotor winding loss. Because PMSM replaces rotor winding with permanent magnet, it usually has higher efficiency and higher power density. However, also because of the permanent magnet, PMSM is more expensive. Since most high performance permanent magnets require the use of rare earth element materials, the PMSM may also have larger price fluctuation in the future. There is also some interests in using switched reluctance machine (SRM) for traction, due to its ruggedness and high power density. However, because of the torque ripple at low speed, and the associating noise problem, currently its use is mainly limited in academic research phase.

To convert the dc power from the battery pack to three phase ac power, a three-phase inverter is included in the power electronics module. More advanced architectures may incorporate a dc-dc converter to control the dc voltage supplied to the inverter. The advantage of the dc-dc converter is discussed in Section 1.2. Bidirectional power flow is usually required by the power electronics module, so that the vehicle is capable of regenerative brake, which means during the vehicle braking, instead of dissipating the vehicle kinetic energy as heat on the brake pad, the energy is partially or fully recycled back into the battery pack. The regenerative break is a distinctive feature of EV, comparing with ICE-powered vehicle.

The battery pack is composed many small battery cells connected in series and parallel. In contrast to the lead-acid batteries used in ICE-powered vehicles, in early 90s nickel-metal hydride (NiMH) battery was considered for BEV. Most of the modern BEV uses lithium-based battery technologies, such as lithium-ion (Li-ion) battery or lithium-polymer (LiPo) battery. A sophisticated battery management system is required for safety protection, cell balancing, state-of-charge (SoC) and state-of-health (SoH) monitoring. An alternative technology of BEV is to use supercapacitor to replace the battery. Comparing with battery, supercapacitor has smaller energy capacity, but larger charging / discharging rate. Therefore, it is more suitable for electric bus applications, where the cruising distance from one charging station to another is short, while more acceleration and braking is required.

### 1.1.2 Hybrid Electric Vehicle (HEV)

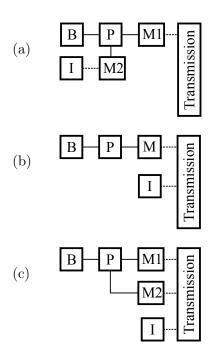

Figure 1.2: Hybrid electric vehicle (HEV) powertrain architecture. B: battery, P: power electronics module, M: motor, I: internal combustion engine. Solid lines: electrical connection. Dotted line: mechanical connection.(a) series hybrid, (b) parallel hybrid, (c) series-parallel hybrid system.

Hybrid electric vehicle (HEV) refers to the type of system where the electric traction system is combined with ICE. The energy source of HEV is gasoline, and it is partially or fully converted to electric energy for traction. Comparing with the conventional ICE-powered vehicle, HEV has better fuel economy because:

(1) The ICE in HEV is only required to provide the average traction power, and the power

rating of the ICE is much reduced. Therefore, machines such as Artkinson cycle engine with lower power rating but higher efficiency are used in HEV.

- (2) In HEV, the driving dynamics is more or less decoupled from ICE. Ideally ICE is only required to operate at one fixed efficiency-optimized operation point.

- (3) HEV is capable of regenerative brake. The vehicle kinetic power is recycled during braking, instead of dissipated.

For example, the Toyota Prius 2016 has 52 combined-MPG.

There are many variations in the HEV powertrain architecture. For example, depending on how much electric power is involved in the traction powertrain, the HEV can be categorized into micro-hybrid, mild-hybrid, and full-hybrid technologies. As a matter of fact, by definition even the existing ICE-powered vehicle can be categorized as HEV, because it has to use the starter motor to start the ICE. Based on similar idea, the micro-hybrid vehicle uses electric motor to reduce the idling time of the ICE. In mild-hybrid vehicle, the electric powertrain is able to handle the regenerative brake. With increased electric traction power, in full-hybrid vehicle the ICE is only required to produce the average driving power, while the peak power is handled by the electric motor. Similar idea has been used in Formula One's race car, where electric motor is used for acceleration. To further increase the portion of the electric traction power to 100% enables the vehicle to operate in electric-only mode. Usually these HEVs allow charging from the grid, which are often referred to as plug-in hybrid electric vehicle (PHEV), or range-extended electric vehicle (REEV).