# Optimization of Active-Bridge Based Modular Power Converters

by

#### Branko Majmunović

B.A., University of Belgrade, 2016M.S., Aalborg University, 2018

A thesis submitted to the

Faculty of the Graduate School of the

University of Colorado in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy

Department of Electrical, Computer, and Energy Engineering

2022

Committee Members:

Prof. Dragan Maksimović, Chair

Prof. Zorana Popović

Prof. Brian Johnson

Prof. Daniel Costinett

Prof. Robert W Erickson

Branko Majmunović, (Ph.D., Electrical, Computer, and Energy Engineering)

Optimization of Active-Bridge Based Modular Power Converters

Thesis directed by Prof. Prof. Dragan Maksimović

Modularization is one of the essential concepts used in today's power electronics integration. Modular converters are often realized based on active bridges, arranged around high-frequency passive components. Due to soft-switching properties, these converters feature high efficiency and high power density, especially at the nominal conversion ratio. This thesis covers optimization of the aforementioned converters from different angles, including topology configuration, selection of semiconductor devices, modulation strategies, as well as optimization and integration of magnetic components. The thesis is organized into two parts based on different target applications.

The first part of the thesis considers the design and optimization of stacked active bridge (SAB) converters for high-conversion ratio dc-to-dc applications. Firstly, a transformerless high step-down SAB dc-dc converter is introduced. The SAB converter consists of series-stacked, capacitively coupled inverter modules and parallel-connected rectifier modules. The nominal step-down conversion ratio is determined by the number of inverter modules, while the output current capability scales with the number of paralleled rectifier modules. SAB operating principles, including phase-shift control and soft switching, achieved through series inductors, are similar to those of transformer-isolated dual active bridge (DAB) converters. It is found that the best size-versus-loss trade-off is achieved by the integration of the series inductors on a custom core. Furthermore, it is shown how soft switching contributes to natural voltage sharing among the series-stacked inverter modules. The approach is verified by experimental results on a 400-to-48 V, 3 kW SAB prototype using GaN devices and featuring 400 W/in<sup>3</sup> power density. A flat efficiency curve is obtained, with 99% peak efficiency, 97.5% full-load efficiency, and 98% efficiency at 20% load. Second, a galvanic isolated version of the SAB converter is discussed. To achieve galvanic isolation, transformers are inserted between the inverters and rectifier bridges. The nominal step-down conversion ratio is

determined by the number of inverter modules and the turns ratio of the transformer. In order to reduce the footprint of the magnetic components, the transformers are coupled on a single core, and the series inductances are realized as controllable leakage inductances within the same magnetic structure using a novel custom core and planar winding arrangement, a solution unique to the iSAB configuration. The approach is verified by experimental results on a 400-to-48 V, 3 kW, 400 kHz iSAB prototype using GaN devices and having 96.7% peak efficiency.

The second part of the thesis is centered around the topic of modular SiC-based string inverters for medium-voltage transformer-less photovoltaic (PV) systems. The interface of lowvoltage (LV) DC to medium-voltage (MV) three-phase AC grid is often based on series-stackable modular converter architectures. To minimize energy storage requirements, it is advantageous to employ a quadruple active bridge (QAB) stage operating as a "dc transformer" (DCX) in each stackable module. The QAB stage offers three isolated dc link voltages, which then allow flexible stacking of three single-phase dc-to-ac inverter stages. Each of the module phases processes a pulsating power having a component at twice the line frequency. This presents a challenge in maintaining zero-voltage switching (ZVS) on the secondary sides of the QAB during low-power portions of the line cycle. The design of the QAB stage is covered in this thesis. A detailed analysis of ZVS switching waveforms is presented, including the effects of nonlinear device capacitances. It is shown how ZVS can be achieved at all times using a relatively small circulating current provided by the magnetizing inductance of the high-frequency transformer. Analytical expressions are given for the optimal values of the magnetizing inductance and the dead times of the QAB primary and secondary bridges. The approach is verified by experimental results on a 1 kV, 10 kW SiC-based prototype, demonstrating a relatively flat efficiency curve with a peak efficiency of 97.1% at 75% load.

### Dedication

To my parents.

#### Acknowledgements

Above all, I would like to express my sincere gratitude to Prof. Dragan Maksimović for equipping me with a fundamental understanding of Power Electronics. Being advised by him and attending his impeccable lectures have been invaluable privileges to me. I will forever be grateful to be impacted by his mind clarity and humbleness throughout the past few years.

I would like to show my appreciation to other members of my thesis committee: Prof. Zoja Popović, Prof. Brian Johnson, Prof. Daniel Costinett, and Prof. Robert W Erickson for their constructive critics, which enhanced this work substantially.

I want to thank Dr. Johan Strydom for his great mentorship during my internship at Texas Instruments, and I hope that a hint of his wisdom has rubbed off on me.

I am also grateful to the Department of Energy - Solar Energy Technologies Office (DOE-SETO) for sponsoring a portion of the work presented in this thesis.

I would like to show appreciation to my supervisors from my master studies at Aalborg University: Prof. Frede Blaabjerg, Prof. Tomislav Dragičević, Prof. Remus Teodorescu, Prof. Tamas Kerekes and Dr. Lorand Bede.

Many thanks to Prof. Predrag Pejović who taught me the first steps in Power Electronics through his unforgettable lectures.

I want to express deep appreciation to all my colleagues from Colorado Power Electronics Center (CoPEC), for exchanging their knowledge and experience, and giving me a helping hand, whenever I needed it throughout the past years. Special thanks to my colleague Dr. Satyaki Mukherjee for endless discussions and challenging each other on various topics, which I took a lot

from.

I will always be grateful to Dr. Zdravko Zubac and Dr. Ivan Zorić for their support and believing in me since my first days in Electrical Engineering.

Finally, I would like to express my deepest thanks to my parents and brother Marko, for their unconditional love and support, and to Natali for being patient and fighting this battle alongside me.

# Contents

# Chapter

| 1 | Intro | oduction                                                                            | 1  |

|---|-------|-------------------------------------------------------------------------------------|----|

|   | 1.1   | Trends and Challenges in Advanced Power Electronics Converters                      | 1  |

|   | 1.2   | DC Transformers in Power Electronics                                                | 2  |

|   | 1.3   | Introduction to Stacked Active Bridge Converters (Part I)                           | 6  |

|   | 1.4   | Introduction to Modular SiC Based String Inverters for Medium-voltage Transformer-  |    |

|   |       | less PV Systems (Part II)                                                           | 8  |

|   | 1.5   | Thesis Outline                                                                      | 12 |

| 2 |       | ing of Semiconductor devices in Stacked Active Bridges                              | 15 |

| 4 | 2.1   |                                                                                     | 15 |

|   | 2.2   | Voltage Scaling of Semiconductor Devices with Splitting the High-Voltage Side with  | 10 |

|   |       | SAB - Theoretical Perspective                                                       | 17 |

|   | 2.3   | Voltage Scaling of Semiconductor Devices with Splitting the High- Voltage Side with |    |

|   |       | SAB - Revisited                                                                     | 18 |

|   | 2.4   | Energy stored in SAB                                                                | 20 |

|   | 2.5   | Chapter Summary and Conclusions                                                     | 21 |

| 3  | 400    | V-to-48                     | V Stacked Active Bridge Converter                                             | 22 |  |  |  |

|----|--------|-----------------------------|-------------------------------------------------------------------------------|----|--|--|--|

|    | 3.1    | 3.1 SAB converter operation |                                                                               |    |  |  |  |

|    | 3.2    | Capac                       | itor voltage balancing                                                        | 26 |  |  |  |

|    | 3.3    | Realiz                      | ation of the series inductors                                                 | 31 |  |  |  |

|    |        | 3.3.1                       | Loss modeling, design optimization, and comparison of inductor realizations . | 33 |  |  |  |

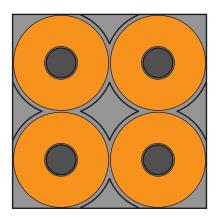

|    |        | 3.3.2                       | Magnetic structure with four coupled inductors                                | 35 |  |  |  |

|    |        | 3.3.3                       | Effects of inductor coupling on the capacitor voltage balancing               | 38 |  |  |  |

|    | 3.4    | Exper                       | imental results                                                               | 38 |  |  |  |

|    | 3.5    | Chapt                       | er Summary and Conclusions                                                    | 48 |  |  |  |

| 4  |        |                             | V Transformer-Isolated Stacked Active Bridge Converter with Integrated Mag-   |    |  |  |  |

|    | neti   |                             |                                                                               | 50 |  |  |  |

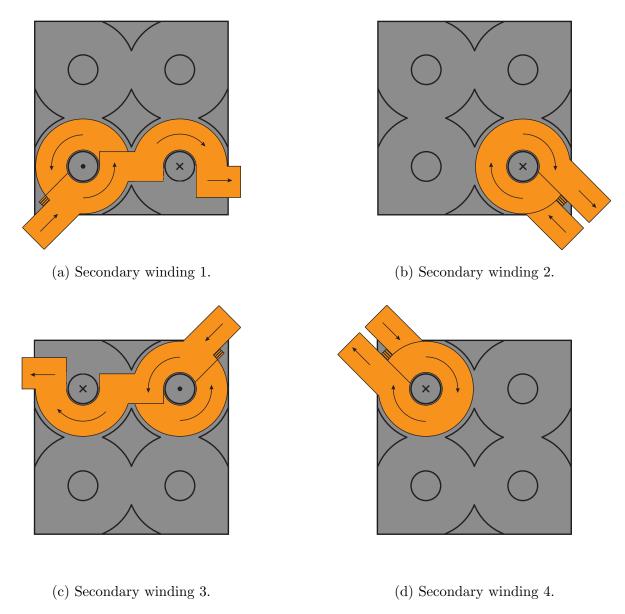

|    | 4.1    | iSAB                        | Integrated Magnetics Structure                                                | 52 |  |  |  |

|    |        | 4.1.1                       | Core Geometry                                                                 | 52 |  |  |  |

|    |        | 4.1.2                       | Primary Side Winding Arrangement and the Magnetizing Flux                     | 52 |  |  |  |

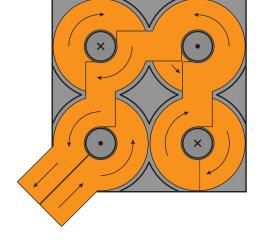

|    |        | 4.1.3                       | Secondary-Side Winding Arrangement and the Magnetizing Flux                   | 55 |  |  |  |

|    | 4.2    | Integr                      | ated Magnetics Design using Finite Element Analysis (FEA)                     | 56 |  |  |  |

|    | 4.3    | Exper                       | imental Results                                                               | 57 |  |  |  |

|    | 4.4    | Chapt                       | er Summary and Conclusions                                                    | 57 |  |  |  |

| Pa | art II | I - Mod                     | lular Silicon Carbide (SiC) Based String Inverters for Medium-voltage         | :  |  |  |  |

|    | Tra    | nsform                      | nerless PV Systems                                                            |    |  |  |  |

| 5  | Desi   | ign and                     | Optimization of a Quadruple Active Bridge DCX Stage in a DC to Three-Phase    | :  |  |  |  |

|    | AC     | Module                      | for Medium-Voltage Grid Integration                                           | 62 |  |  |  |

|    | 5.1    | Introd                      | uction                                                                        | 62 |  |  |  |

|    |        | 5.1.1                       | Control Signals for Zero Voltage Switching at Zero Instantaneous Power        |    |  |  |  |

|    |        |                             | Transfer in One Phase                                                         | 66 |  |  |  |

|   | 3.2  | ZVSS     | sequence Analysis Neglecting the Parasitic Capacitance of the Series inductor. | υı |

|---|------|----------|--------------------------------------------------------------------------------|----|

|   |      | 5.2.1    | Zero Voltage Switching at Zero Instantaneous Power Transfer in One Phase $ . $ | 67 |

|   |      | 5.2.2    | Experimental results                                                           | 75 |

|   |      | 5.2.3    | Summary of the Section                                                         | 80 |

|   | 5.3  | ZVS S    | Sequence Analysis Considering the Parasitic Capacitance of the Series Inductor | 80 |

|   |      | 5.3.1    | Zero voltage switching at zero instantaneous power transfer in one phase       | 80 |

|   |      | 5.3.2    | Parameter Selection for Minimum Peak Magnetizing Current                       | 83 |

|   |      | 5.3.3    | Sensitivity to parameter variations                                            | 90 |

|   | 5.4  | Design   | optimization                                                                   | 91 |

|   |      | 5.4.1    | Active-bridge conduction losses                                                | 93 |

|   |      | 5.4.2    | Loss in the magnetic components                                                | 94 |

|   |      | 5.4.3    | Total modeled loss                                                             | 97 |

|   | 5.5  | Exper    | imental results                                                                | 98 |

|   |      | 5.5.1    | Design validation                                                              | 00 |

|   |      | 5.5.2    | Efficiency comparison against a conventional design using a large magnetizing  |    |

|   |      |          | inductance                                                                     | 05 |

|   |      | 5.5.3    | Efficiency and loss breakdown                                                  | 08 |

|   | 5.6  | Concl    | usions                                                                         | 09 |

| 6 | Cone | clusions | s and Future Work 1                                                            | 11 |

|   | 6.1  | Thesis   | s Summary and Conclusions                                                      | 11 |

|   | 6.2  | Future   | e Work Directions                                                              | 13 |

|   |      |          |                                                                                |    |

| Bibliography | 117 |

|--------------|-----|

| A 1    | •            |

|--------|--------------|

| Append | 17           |

| Append | $\mathbf{L}$ |

|        |              |

| A | Derivation of Relations Between Parameters Mismatch and Voltage Imbalance Between The |         |                        |       |  |  |

|---|---------------------------------------------------------------------------------------|---------|------------------------|-------|--|--|

|   | Mod                                                                                   | ules in | SAB                    | 125   |  |  |

| В | Loss                                                                                  | Model   | ling in SAB            | 127   |  |  |

|   | B.1                                                                                   | Induct  | or loss                | . 127 |  |  |

|   |                                                                                       | B.1.1   | Copper loss            | . 127 |  |  |

|   |                                                                                       | B.1.2   | Core loss              | . 127 |  |  |

|   | B.2                                                                                   | Semico  | onductor device losses | . 128 |  |  |

|   |                                                                                       | B.2.1   | Conduction loss        | . 128 |  |  |

|   |                                                                                       | B.2.2   | Turn-on loss           | . 128 |  |  |

|   |                                                                                       | B.2.3   | Turn-off loss          | . 128 |  |  |

|   | В.3                                                                                   | PCB 1   | osses                  | . 129 |  |  |

# Tables

# Table

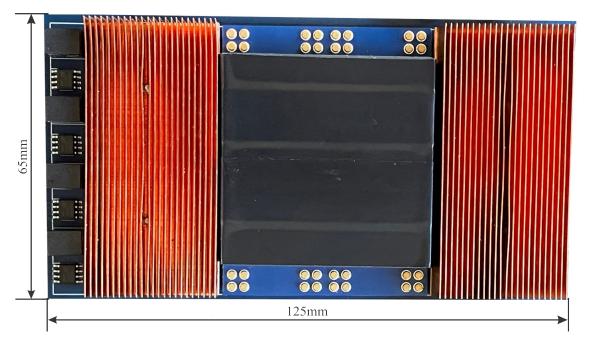

| 3.1  | Components and parameter values in the 400-to-48 V, $3\mathrm{kW}$ SAB prototype $\ \ldots\ \ldots$ | 39  |

|------|-----------------------------------------------------------------------------------------------------|-----|

| 3.2  | Experimentally measured imbalance of the inverter input dc voltages with respect                    |     |

|      | to the nominal value of $V_{IN}/4=100\mathrm{V}$                                                    | 43  |

| 3.3  | Delay mismatch introduced by the gate driver (LMG1210RVRT) and the digital                          |     |

|      | isolator (SN74LVC2G17DBVT)                                                                          | 43  |

| 3.4  | Comparison of 400-to-48 V, $3\mathrm{kW}$ prototypes                                                | 48  |

| 5.1  | Time instants of the switching sequence during ZVS transition                                       | 67  |

| 5.2  | Time intervals of the switching sequence during ZVS transition                                      | 67  |

| 5.3  | System specifications and circuit parameters                                                        | 69  |

| 5.4  | Time instants of the approximated switching sequence                                                | 73  |

| 5.5  | Time intervals of the approximated switching sequence                                               | 73  |

| 5.6  | Experimental prototype parameters                                                                   | 75  |

| 5.7  | Design parameters                                                                                   | 76  |

| 5.8  | Time instants of the switching sequence during ZVS transition                                       | 82  |

| 5.9  | Time intervals of the switching sequence during ZVS transition                                      | 82  |

| 5.10 | Experimental prototype parameters                                                                   | 90  |

| 5.11 | Capacitances in the experimental prototype                                                          | 91  |

| 5.12 | Components used in the hardware prototype                                                           | 100 |

| 5.13 | Dead times, | magnetizing | inductance, | and | maxir | num | phase | shif | t in | the | e ex | cpe | rin | neı | nta | ıl |     |

|------|-------------|-------------|-------------|-----|-------|-----|-------|------|------|-----|------|-----|-----|-----|-----|----|-----|

|      | prototype . |             |             |     |       |     |       |      |      |     |      |     |     |     |     |    | 105 |

# Figures

# Figure

| 1.1 | Applications with high demand of advanced power electronics systems: data centers,    |    |

|-----|---------------------------------------------------------------------------------------|----|

|     | smart homes, solar farms, and electric vehicle charging stations [12]                 | 2  |

| 1.2 | Turn-on and turn-off trajectory in drain to source current vs. voltage plane for hard |    |

|     | and soft switching transitions                                                        | 3  |

| 1.3 | Topology that represents an example of a galvanically-isolated high step-down "dc     |    |

|     | transformer"                                                                          | 4  |

| 1.4 | DAB and SRC ac currents at nominal conversion ratio                                   | 5  |

| 1.5 | Topology that represents a non-isolated example of a high step-down "dc transformer". | 6  |

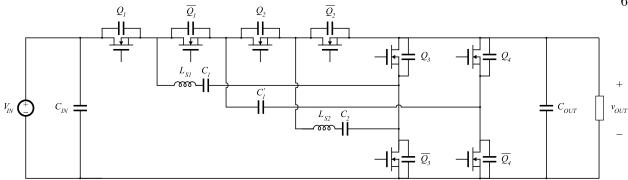

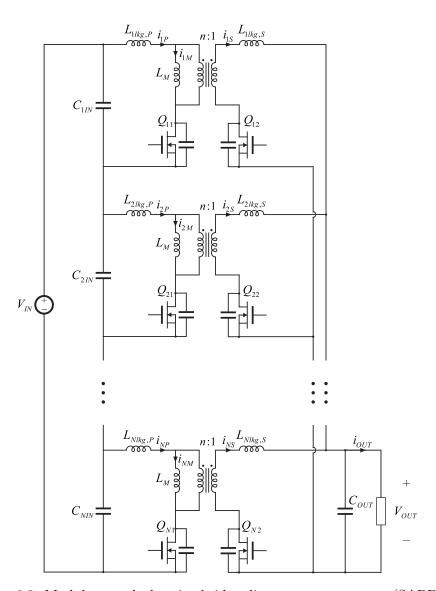

| 1.6 | Stacked active bridge (SAB) dc-dc converter comprising of 4 series-stacked, capaci-   |    |

|     | tively coupled half-bridge inverter modules and 2 parallel-connected full-bridge rec- |    |

|     | tifier modules                                                                        | 7  |

| 1.7 | Traditional LVDC to MVAC architecture using line frequency transformer                | 9  |

| 1.8 | Modular multilevel architectures for interfacing LVDC to MVAC [16]                    | 10 |

| 1.9 | Modular multilevel architecture for interfacing LVDC to MVAC based on a three-        |    |

|     | phase module. The module is based on QAB dcdc converter that provides galvanic        |    |

|     | isolation between the phases                                                          | 11 |

| 2.1 | Modular connection of active bridges                                                  | 16 |

| 2.2 | Voltage scaling of the RSP                                                            | 19 |

| 2.3 | Scaling of the normalized conduction loss of the SAB with blocking voltage of the                                                                           |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | devices used in the stack                                                                                                                                   | 20 |

| 3.1 | Stacked active bridge (SAB) dc-dc converter comprising $n=4$ series-stacked, capac-                                                                         |    |

|     | itively coupled half-bridge inverter modules and $m=2$ parallel-connected full-bridge                                                                       |    |

|     | rectifier modules                                                                                                                                           | 23 |

| 3.2 | Control signals $c_I$ , $\overline{c_I}$ for the inverter modules, and $c_R$ , $\overline{c_R}$ , for the rectifier modules,                                |    |

|     | together with the inductor currents $i_{14}$ in the SAB converter of Fig. 3.1                                                                               | 25 |

| 3.3 | SAB converter with two inverter modules having a timing mismatch between the                                                                                |    |

|     | control signals $c_{I,1}$ and $c_{I,2}$                                                                                                                     | 26 |

| 3.4 | Control signals $c_{I,1}$ , $\overline{c_{I,1}}$ and $c_{I,2}$ , $\overline{c_{I,2}}$ for the inverter modules, and $c_R$ , $\overline{c_R}$ , for the rec- |    |

|     | tifier modules, together with the input currents $i_{IN,1}$ , $i_{IN,2}$ , and the switching node                                                           |    |

|     | voltages $v_{sw,1}$ , $v_{sw,2}$ in the SAB converter of Fig. 3.3 under imbalanced conditions                                                               |    |

|     | due to timing mismatches                                                                                                                                    | 27 |

| 3.5 | State-plane diagrams for the normalized switching node voltages $v_{sw,1}$ , $v_{sw,2}$ , and                                                               |    |

|     | inductor currents $i_1$ , $i_2$ , corresponding to the waveforms under imbalanced condi-                                                                    |    |

|     | tion shown in Fig. 3.4. The state-plane trajectories when the voltages are perfectly                                                                        |    |

|     | balanced are shown in light-gray color                                                                                                                      | 28 |

| 3.6 | Voltage imbalance $\Delta V$ as a function of the timing mismatch $t_{\Delta\beta}$ between the control                                                     |    |

|     | signals $c_{I,1}$ and $c_{I,2}$ in the SAB converter of Fig. 3.3, for different values of the half-                                                         |    |

|     | bridge switch node capacitance $C_{HB}$                                                                                                                     | 29 |

| 3.7 | Voltage imbalance $\Delta V$ as a function of the inductance mismatch $\Delta L/L$ , for different                                                          |    |

|     | values of the half-bridge switch-node capacitance $C_{HB}$                                                                                                  | 30 |

| 3.8 | Voltage imbalance $\Delta V$ as a function of the half-bridge switch-node capacitance mis-                                                                  |    |

|     | match $\Delta C_{HB}/C_{HB}$ , where $C_{HB}=2.4\mathrm{nF}.$                                                                                               | 30 |

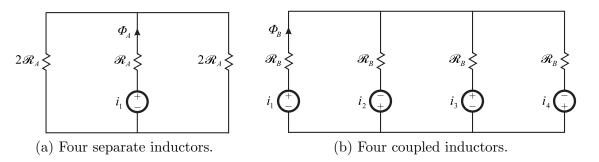

| 3.9 | Four different realizations of the series inductors                                                                                                         | 31 |

| e- |

|----|

| OX |

| 32 |

| 33 |

| on |

| at |

| 34 |

| ), |

| re |

| ct |

| 35 |

| ur |

| 36 |

| 37 |

| ре |

| ds |

| 39 |

| ре |

| re |

| 40 |

| n- |

| es |

| 40 |

| 41 |

| es |

| n- |

| 42 |

|    |

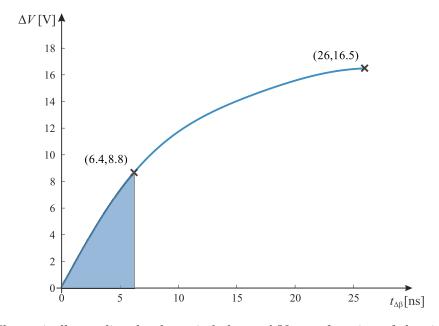

| 3.21 | Theoretically predicted voltage imbalance $\Delta V$ as a function of the timing mismatch                       |    |

|------|-----------------------------------------------------------------------------------------------------------------|----|

|      | $t_{\Delta\beta}$ between the control signals $c_{I,1}$ and $c_{I,2}$ in the SAB converter with the half-bridge |    |

|      | switch node capacitance $C_{HB}=2.4nF$ . The predicted range of $\Delta V$ is determined                        |    |

|      | based on the maximum time delay mismatch given in Table 3.3                                                     | 42 |

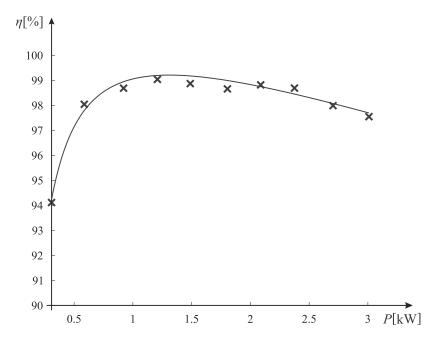

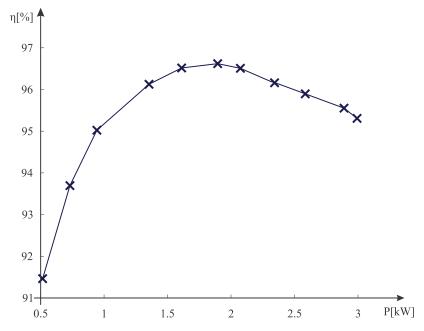

| 3.22 | Measured efficiency of the experimental SAB prototype, together with a model-                                   |    |

|      | predicted efficiency curve, as functions of the output power from 10% to 100%                                   | 43 |

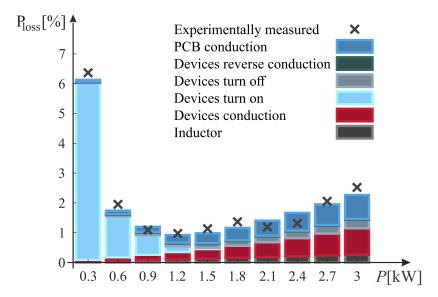

| 3.23 | Model-predicted loss budget and the total measured loss in the $3\mathrm{kW}$ SAB prototype                     |    |

|      | operating from 10% to 100% of load                                                                              | 44 |

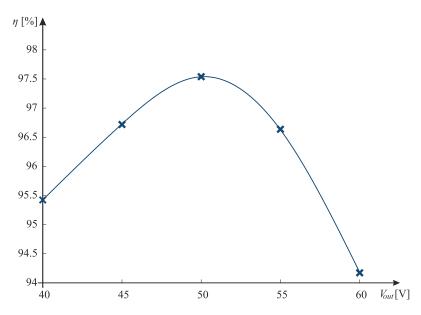

| 3.24 | Measured efficiency of the experimental SAB prototype, as a function of the output                              |    |

|      | voltage from -20% to +20% of the nominal voltage, at fixed output power of $3\mathrm{kW}.$                      | 45 |

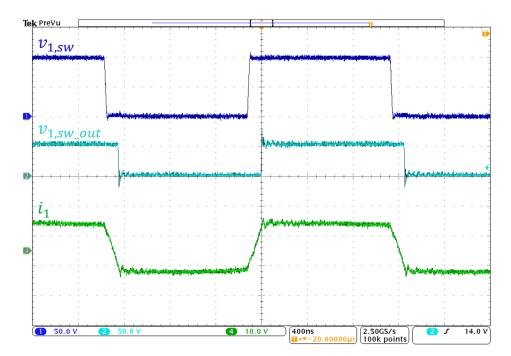

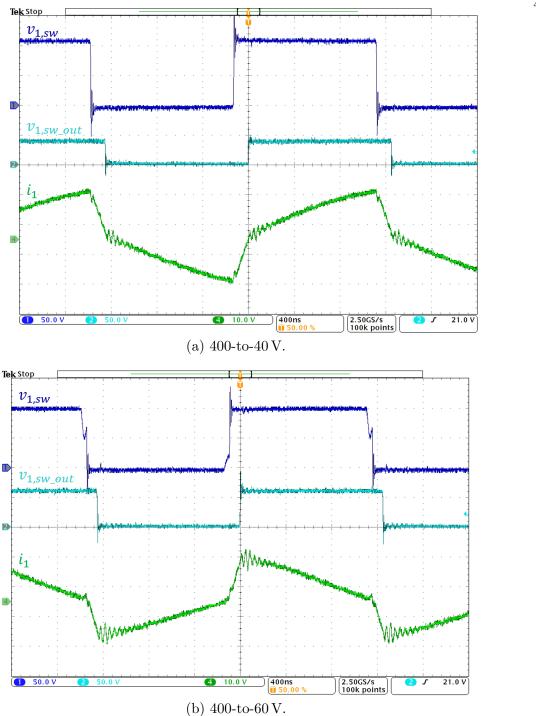

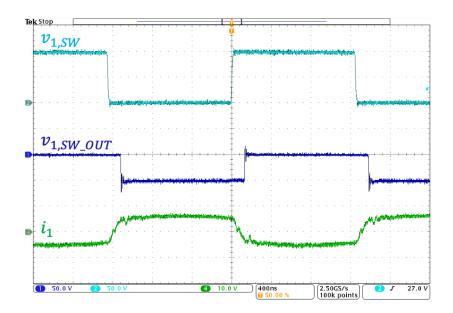

| 3.25 | Experimental waveforms in the SAB prototype operating at $\pm 20\%$ of the nominal                              |    |

|      | output voltage at 3 kW: inverter 1 switch-node voltage $v_{1,sw}$ , rectifier 1 switch-node                     |    |

|      | voltage $v_{1,sw,out}$ , and series inductor current $i_1$                                                      | 46 |

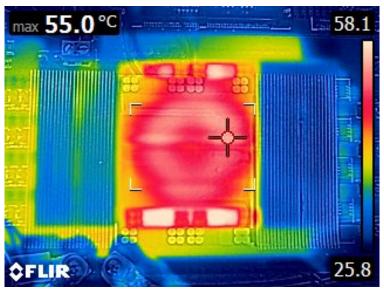

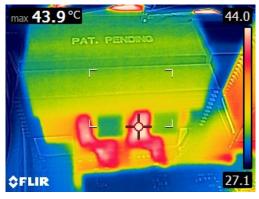

| 3.26 | Thermal images of the SAB prototype taken at $3\mathrm{kW}$ output power. The ambient                           |    |

|      | temperature is $25^{\circ}$ C                                                                                   | 47 |

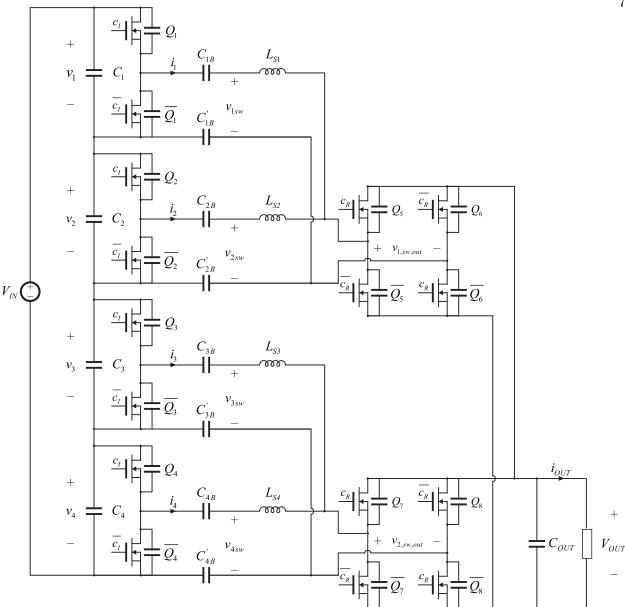

| 4.1  | Isolated stacked active bridge (iSAB) dc-dc converter comprising $n=4$ series-                                  |    |

|      | stacked, half-bridge inverters and $m=2$ parallel-connected full-bridge rectifier mod-                          |    |

|      | ules. All transformers and series inductors are integrated on the same custom mag-                              |    |

|      | netic core with planar windings.                                                                                | 51 |

| 4.2  | Integrated magnetics core and primary winding arrangement, together with illustra-                              |    |

|      | tion of the magnetizing flux path                                                                               | 53 |

| 4.3  | Winding arrangement of the secondary-side planar windings                                                       | 54 |

| 4.4  | Leakage flux path                                                                                               | 55 |

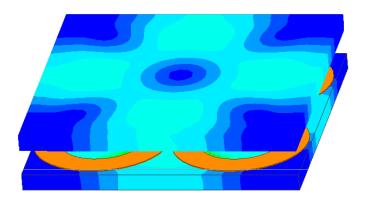

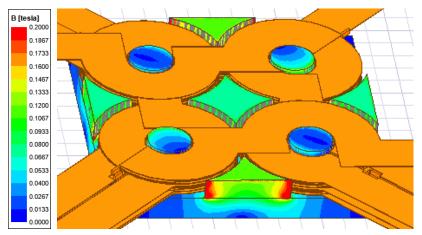

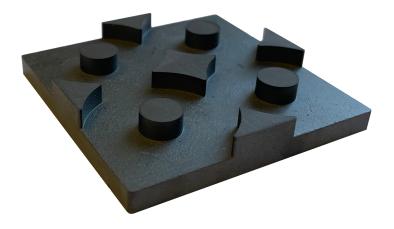

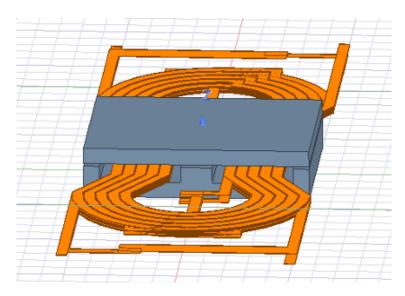

| 4.5  | FEA simulation of the integrated magnetics structure and iSAB current waveforms.                                | 56 |

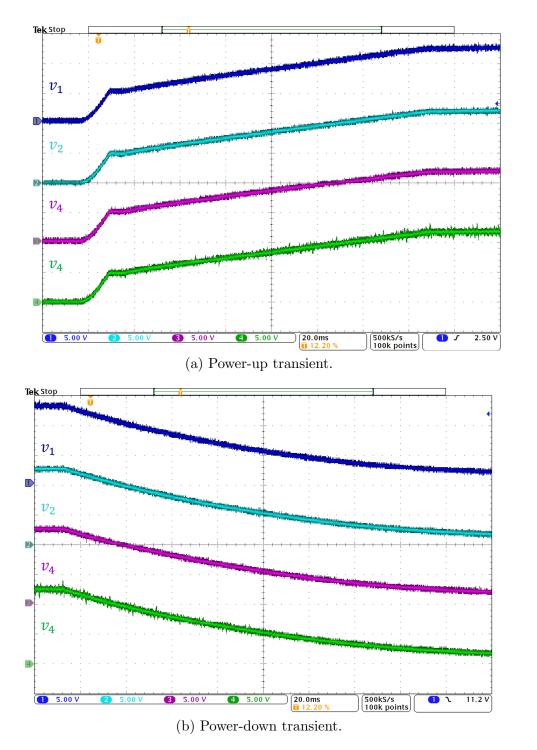

| 4.6  | Photograph of the 3 kW, 400-to-48 V iSAB prototype                                                              | 58 |

| 4.7  | Experimental waveforms in the 400-to-48 V iSAB prototype operating at $3\mathrm{kW};$ in-             |    |

|------|-------------------------------------------------------------------------------------------------------|----|

|      | verter 1 switch-node voltage $v_{1,sw}$ , rectifier 1 switch-node voltage $v_{1,sw,out}$ , and series |    |

|      | inductor current $i_1$                                                                                | 59 |

| 4.8  | Measured efficiency of the experimental iSAB prototype as a functions of the output                   |    |

|      | power from 10% to 100%                                                                                | 59 |

| 5.1  | System architecture with cascaded isolated inverter modules [4]. The module config-                   |    |

|      | uration is shown in Fig. 5.2                                                                          | 63 |

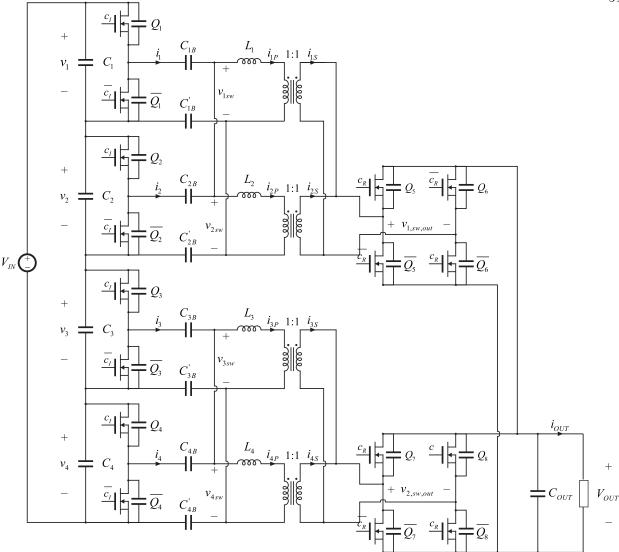

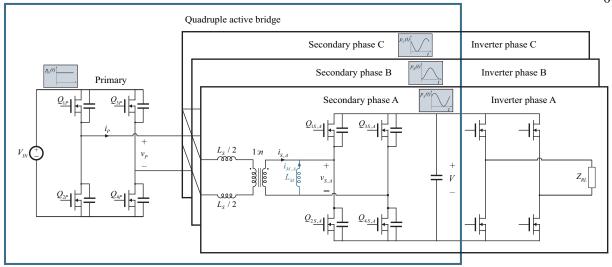

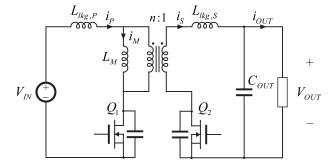

| 5.2  | Transformer-isolated inverter module using a quadruple active bridge (QAB) dc-dc                      |    |

|      | converter operated as a fixed-ratio "dc transformer" (DCX).<br>                                       | 64 |

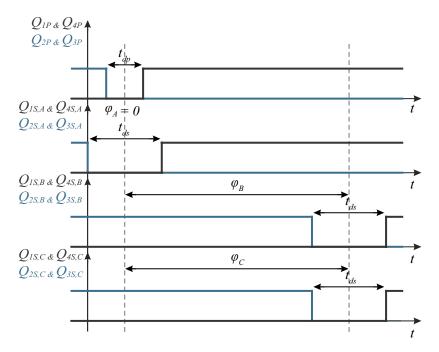

| 5.3  | QAB switch control signals at the time when the secondary Phase A processes zero                      |    |

|      | power                                                                                                 | 66 |

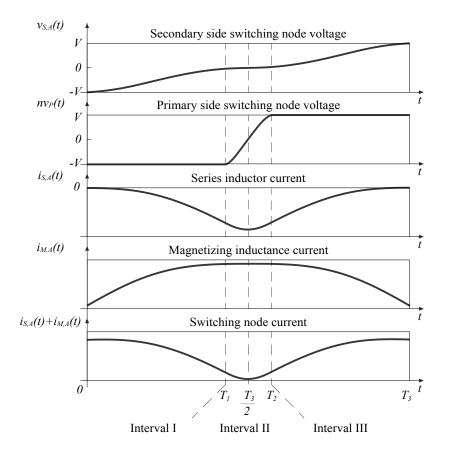

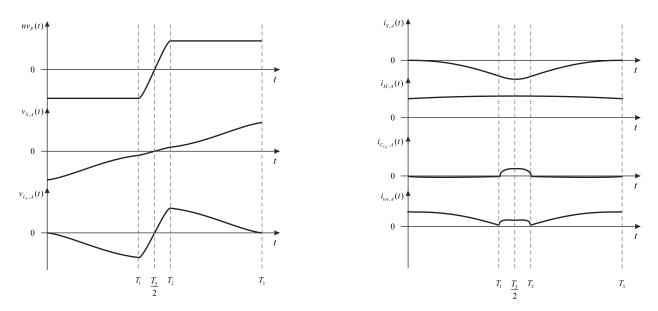

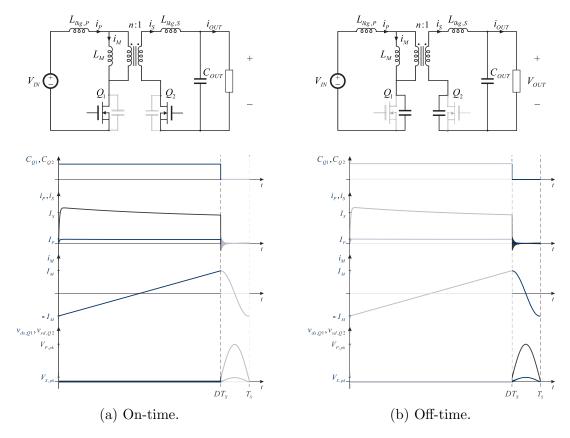

| 5.4  | Model-based waveforms of the ZVS transition at the zero power transfer instant for                    |    |

|      | Phase A. Referring to Fig. 5.3, $T_3 = t_{ds}$ and $T_2 - T_1 = t_{dp}$                               | 68 |

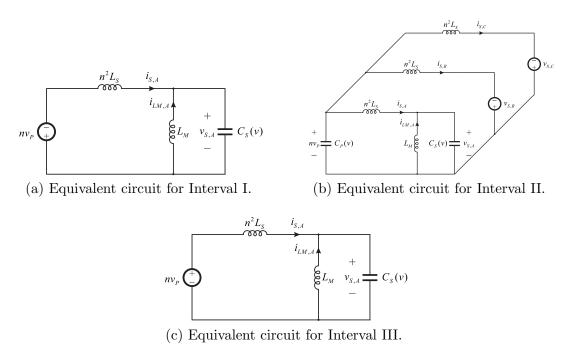

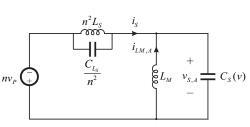

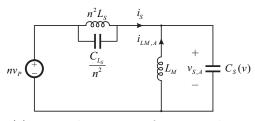

| 5.5  | Equivalent circuits during ZVS transition at the zero power transfer instant for one                  |    |

|      | of the phases                                                                                         | 71 |

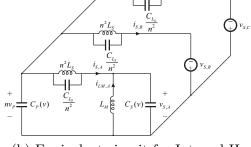

| 5.6  | Approximate equivalent circuits during ZVS transition                                                 | 72 |

| 5.7  | Exact and approximate waveforms of the primary side switching-node voltage $nv_p(t)$                  |    |

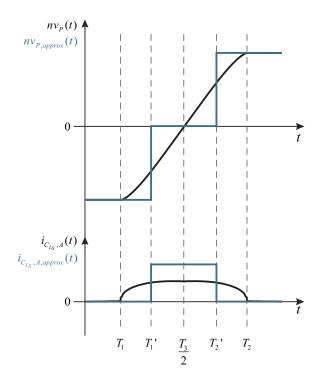

|      | during Interval II                                                                                    | 72 |

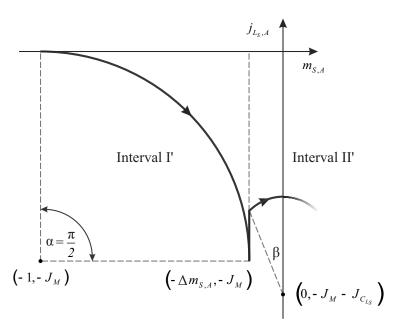

| 5.8  | State plane trajectory during interval I'                                                             | 73 |

| 5.9  | $600\mathrm{V},4\mathrm{kW}$ SiC-based experimental prototype                                         | 75 |

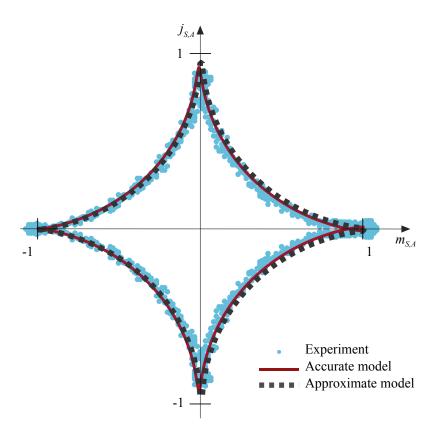

| 5.10 | State plane trajectory at the time Phase A power is zero. Experimental results are                    |    |

|      | overlapped with solutions based on accurate and approximate models                                    | 76 |

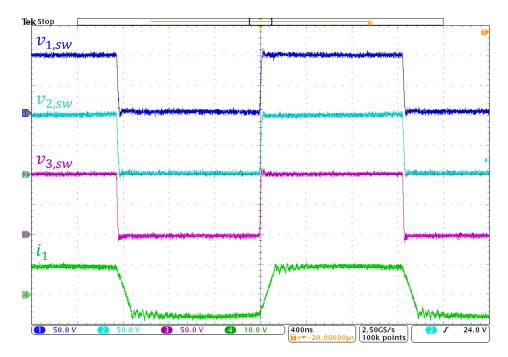

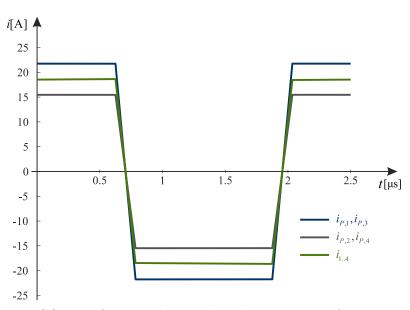

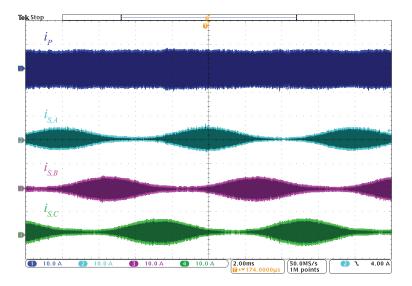

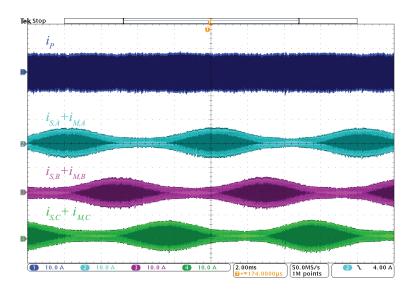

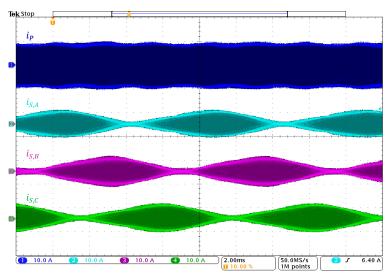

| 5.11 | Quadruple active bridge primary and secondary currents                                                | 77 |

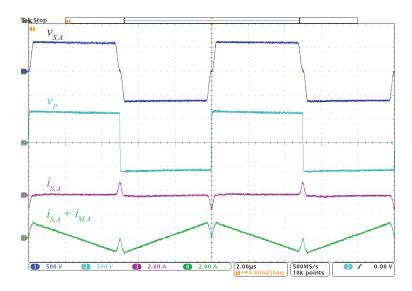

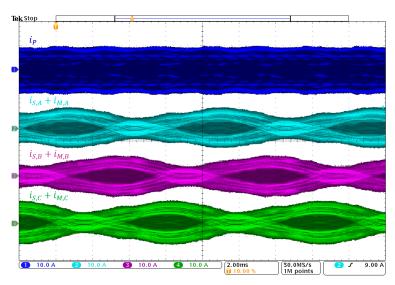

| 5.12 | Quadruple active bridge primary and secondary currents                                                | 78 |

| 5.13 | Efficiency measurements                                                                               | 79 |

| 5.14 | Model-based waveforms of the ZVS transition at the zero power transfer instant for                   |     |

|------|------------------------------------------------------------------------------------------------------|-----|

|      | Phase A. Referring to Fig. 5.3, $T_3 = t_{ds}$ and $T_2 - T_1 = t_{dp}$                              | 81  |

| 5.15 | Equivalent circuits during ZVS transition at the zero power transfer instant for one                 |     |

|      | of the phases                                                                                        | 82  |

| 5.16 | Half-bridge switching node device capacitance                                                        | 84  |

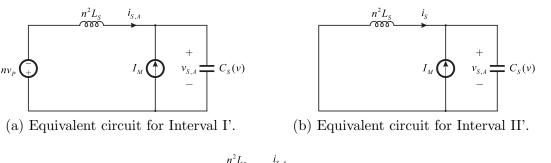

| 5.17 | Approximate equivalent circuits during ZVS transition                                                | 85  |

| 5.18 | Exact and approximate waveforms of the primary-side switching-node voltage $nv_p(t)$                 |     |

|      | during Interval II                                                                                   | 87  |

| 5.19 | State plane trajectory during intervals $I'$ and $II'$                                               | 88  |

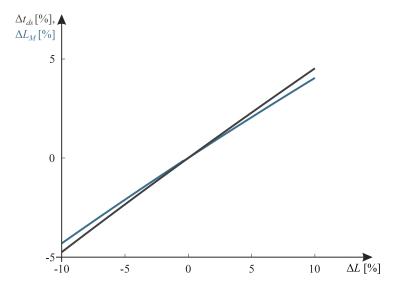

| 5.20 | Effects of the variation in the series inductance on the changes $\Delta t_{sd}$ and $\Delta L_M$ in |     |

|      | the design parameters                                                                                | 91  |

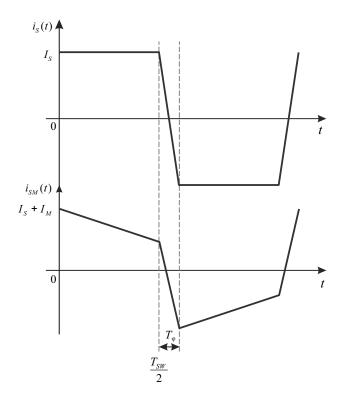

| 5.21 | Theoretical currents waveforms during a switching period                                             | 92  |

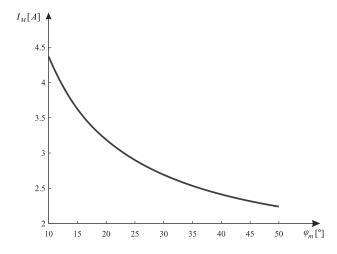

| 5.22 | Peak magnetizing current dependence on $\varphi_m$                                                   | 92  |

| 5.23 | RMS primary and secondary currents as functions of $\varphi_m$                                       | 93  |

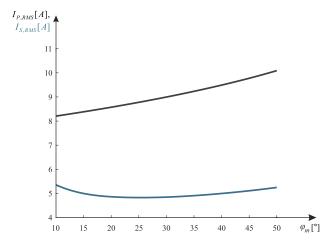

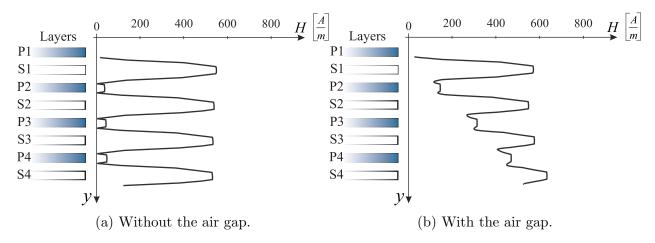

| 5.24 | H field magnitude in the planar high frequency transformer along $y$ axis at one                     |     |

|      | instant during a line cycle                                                                          | 95  |

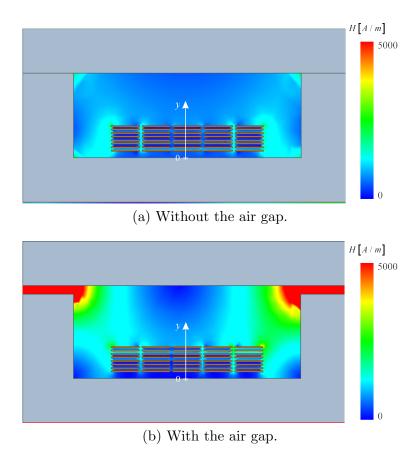

| 5.25 | 2D FEA simulation showing $H$ field distribution in the planar high frequency trans-                 |     |

|      | former at a point of the line cycle                                                                  | 96  |

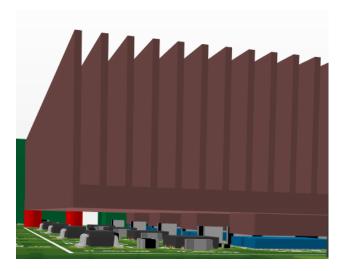

| 5.26 | 3D model of the MV high frequency transformer used for finite-element analysis in                    |     |

|      | Ansys Maxwell                                                                                        | 97  |

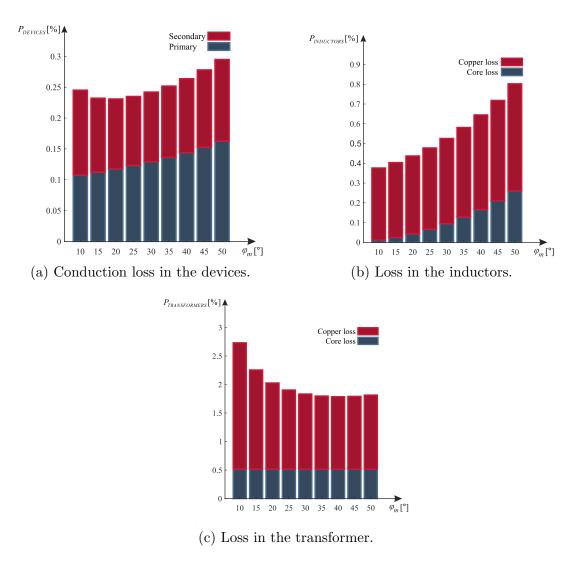

| 5.27 | Component losses as functions of the maximum phase shift $\varphi_m$                                 | 98  |

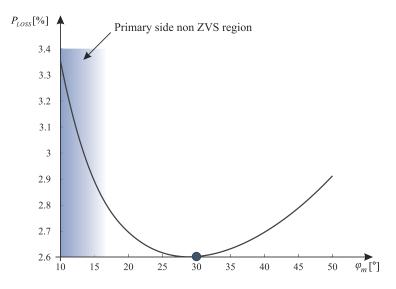

| 5.28 | Total loss as a function of $\varphi_m$                                                              | 99  |

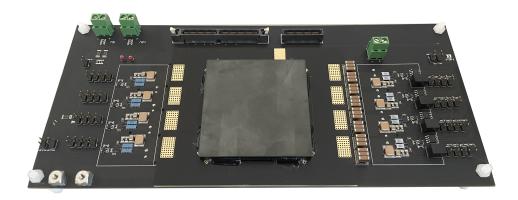

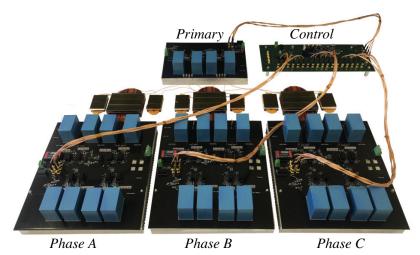

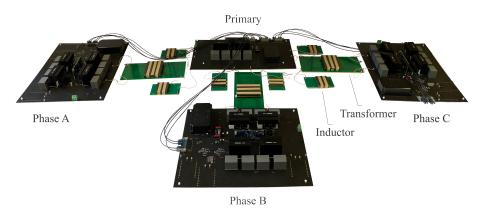

| 5.29 | $1\mathrm{kV},10\mathrm{kW}$ SiC-based prototype of the isolated DC to three-phase AC module 1       | 100 |

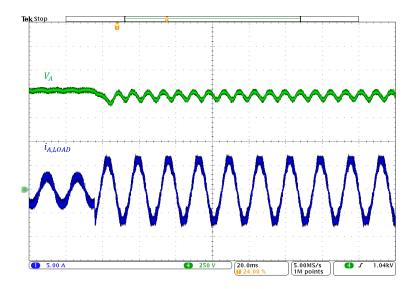

| 5.30 | Phase A dc-link voltage $V_A$ and the inverter output current $i_{A,LOAD}$ , during a step           |     |

|      | change from $50\%$ to $100\%$ of load                                                                | 101 |

| 5.31 | Quadruple active bridge primary and secondary currents                                               | 102 |

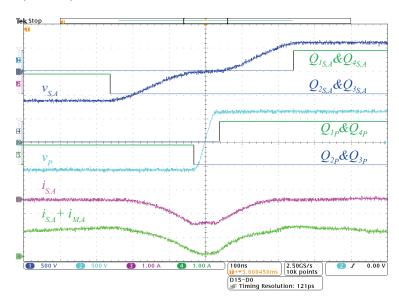

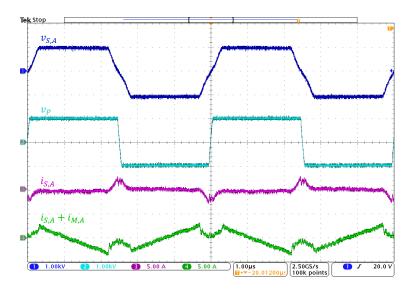

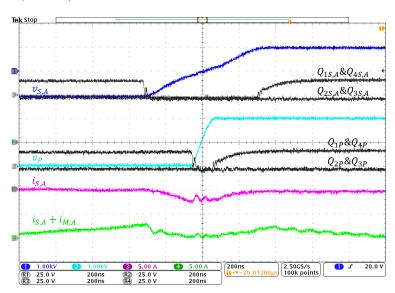

| 5.32 | Waveforms illustrating zero voltage switching at the zero power instant for phase A.                 | 103 |

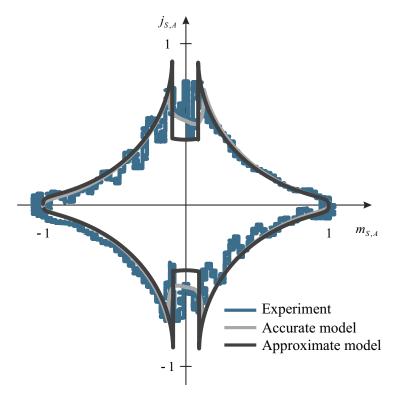

| 5.33 | State plane trajectory at the time Phase A power is zero. Experimental results are        |

|------|-------------------------------------------------------------------------------------------|

|      | overlapped with solutions based on accurate and approximate models                        |

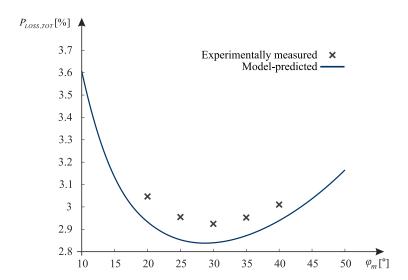

| 5.34 | Experimentally measured loss for designs around the optimum $\varphi_m$ together with the |

|      | model-predicted optimization curve                                                        |

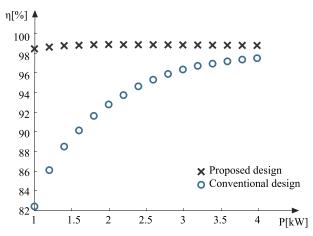

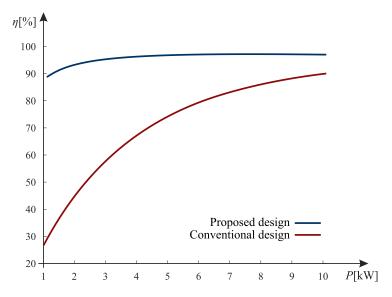

| 5.35 | Model-predicted efficiency curves for the design with the optimized maximum phase         |

|      | shift, magnetizing inductance, and dead times, and for the conventional design with       |

|      | ungapped transformers                                                                     |

| 5.36 | Model-predicted loss breakdown of the QAB prototype using conventional design             |

|      | with ungapped transformers                                                                |

| 5.37 | Loss of the experimental QAB prototype operating at 500 V dc link voltages using          |

|      | conventional design with ungapped transformers, together with a model-predicted           |

|      | loss breakdown                                                                            |

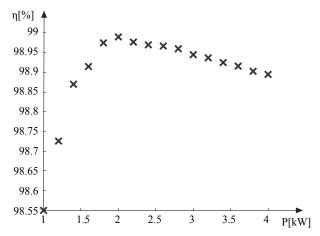

| 5.38 | Efficiency of the experimental QAB prototype using the optimized maximum phase            |

|      | shift, magnetizing inductance, and dead times, together with a model-predicted ef-        |

|      | ficiency curve                                                                            |

| 5.39 | Loss of the experimental QAB prototype using the optimized maximum phase shift,           |

|      | magnetizing inductance, and dead times, together with a model-predicted loss break-       |

|      | down                                                                                      |

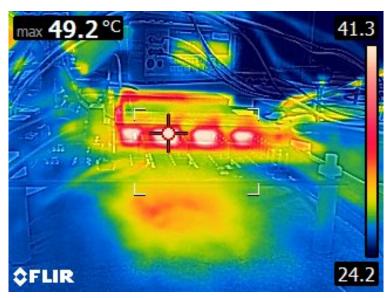

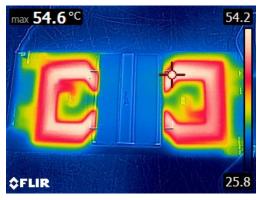

| 5.40 | Thermal images of the devices and one of the transformers in the experimental pro-        |

|      | to<br>type operating at full power (10 kW) and at room ambient temperature, without       |

|      | any forced-air cooling                                                                    |

| 6.1  | Direct Power Converter (DPx)                                                              |

| 6.2  | Equivalent circuits and operating waveforms of DPx over the switching period 115          |

| 6.3  | Modular, stacked active bridge direct power converter (SABDPx)                            |

#### Chapter 1

#### Introduction

#### 1.1 Trends and Challenges in Advanced Power Electronics Converters

Power Electronics (PE) is responsible for converting electric power from one form to another, which makes it an essential part of every electric system. Over 70% of electrical energy, today is processed by PE. This trend will continue to grow over the next few decades [1]. Moreover, it is projected that 40% of the overall worldwide energy consumption will be in the form of electricity by 2030. As illustrated in Fig. 1.1, some of the areas where the PE is exceedingly expanding include: data centers, telecommunication systems, smart homes, renewable energy systems, electrified vehicles etc.

Improvements in efficiency, and power density, as well as cost reduction, are the main factors that drive innovations in the design and optimization of power converters. Miniaturization of power converters is mainly driven by the rise in switching frequency, which leads to a reduction of energy stored in the passive components, namely inductors and capacitors [70]. The size reduction and high-frequency content further impose challenges in loss reduction and thermal management of passive components. The rise in the operating switching frequency also imposes challenges in the thermal management of semiconductor devices. Switching loss, which is caused by the overlap of drain to source voltage and current, as well as stored charge in the power device, proportionally increases with switching frequency. Power devices based on wide-bandgap (WBG) materials such as Gallium Nitride (GaN), and Silicon Carbide (SiC) have recently gained massive attention due to their high critical electric field, which leads to several orders of magnitude smaller specific

Figure 1.1: Applications with high demand of advanced power electronics systems: data centers, smart homes, solar farms, and electric vehicle charging stations [12].

on-resistance (RSP), compared to traditionally used silicon-based devices, greatly increasing the overall wafer yield. Reduction in RSP means that the same resistance of the channel can be achieved with a smaller die area, which reduces parasitic capacitances of the device, and therefore reduces switching loss [30]. Nevertheless, simply replacing the silicon devices with wide-bandgap devices does not fully utilize the potential benefits. Instead, proper selection of topology, together with devices, and design of passives results in a competent design for a particular application. Traditionally used hard-switched, pulse-width-modulated (PWM) converters have fundamentally limited efficiency with the amount of indirect power that is being processed. The amount of indirect power is directly proportional to the conversion ratio [91]. More indirect power results in larger ac losses in the converter. The ac losses scale up with higher operating frequencies, placing constraints on the miniaturization of the power converters, especially for high step-up/down applications.

#### 1.2 DC Transformers in Power Electronics

The class of converters known as "dc transformer," or "DCX" features superior performance in fixed, high conversion ratio applications [85, 97], in terms of efficiency and power density. Their main property is processing indirect power efficiently. This is achieved thanks to:

• Soft-switching of semiconductor devices. Soft-switching can take two major forms: zero-

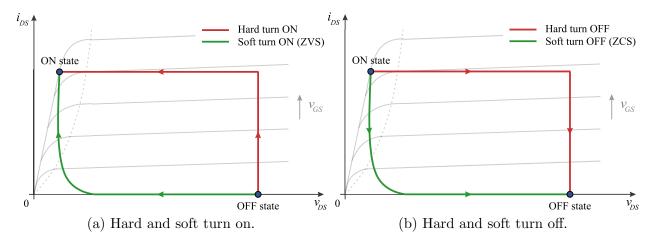

Figure 1.2: Turn-on and turn-off trajectory in drain to source current vs. voltage plane for hard and soft switching transitions.

voltage-switching (ZVS), or zero-current-switching (ZCS). ZVS event happens when drain to source voltage of the device drops to zero before the device starts turning on, i.e. before the current in the channel starts rising. Similarly, ZCS event occurs with the current falling down to zero, before turning the device off. Fig. 1.2 represents turn-on and turn-off trajectories in drain to source current vs. voltage plane for hard and soft switching transitions. Both ZVS and ZCS greatly reduce the overlap between the voltage and current of the device, compared to a hard-switching event. High voltage and low to moderate current applications can greatly benefit from ZVS, while ZCS is beneficial in low voltage high currents applications. Loss reduction offered by soft switching enables semiconductor devices to switch at higher frequencies, without significant loss increase.

• AC inductors. Inductors in traditional PWM converters carry both DC + AC components. A higher conversion ratio imposes higher volt-seconds across the inductor, which means that the value of the inductance needs to be increased, in order to keep the current ripple within the specified limits. Increased inductance leads to larger energy stored in the inductor  $E_{ind} = \frac{LI_{ind}^2}{2}$ . Contrary, ac inductors only need to store as much energy, as it is needed to charge/discharge parasitic capacitance of the switching node of the active

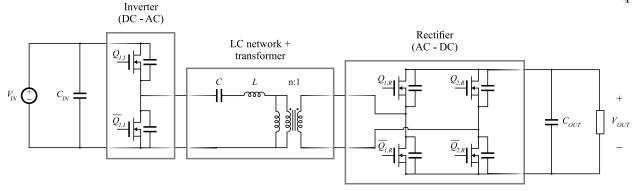

Figure 1.3: Topology that represents an example of a galvanically-isolated high step-down "dc transformer".

bridge, to accommodate for the soft-switching of the devices. Storing less energy is in direct correlation with reduced loss, and size of the inductor.

A commonly used transformer-isolated DCX is presented in Fig. 1.3. The converter consists of three major parts:

- Inverter converts DC power to AC power. To achieve ZVS of the inverter bridge, it is essential that the current coming out of the switching node, lags behind the switching node voltage, i.e. that the input impedance seen from the inverter needs to look inductive at the operating frequency. For example, at the turn-off event of the bottom switch, the direction of the current coming out of the switch node needs to be negative, so that the inductor current naturally charges up the parasitic capacitance of the switching node.

- LC network + transformer determines the conversion ratio of the converter, together with the operating switching frequency, the phase shift between the active bridges, and the load. Aside from the current direction, it is necessary that inductive energy stored in the LC network is greater than the energy stored in the parasitic capacitance of the switching node of the active bridge, in order to complete ZVT.

- Rectifier converts AC power back to DC power. Unlike in the case of the inverter bridge, the current entering the switching node of the rectifier bridge needs to lead the switching

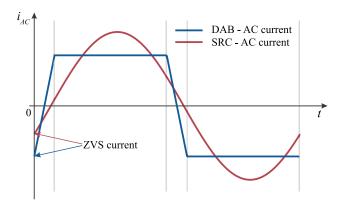

Figure 1.4: DAB and SRC ac currents at nominal conversion ratio.

node voltage in order to achieve ZVS.

Based on the control of active bridges, and LC network design, DCX could be realized as: Series-Resonant-Converter (SRC) [88, 90], Dual-Active-Bridge (DAB) [24, 20], LLC [92], etc. The DCX can be operated as an SRC if the resonant frequency of the series inductor L and capacitor Cis relatively close to the switching frequency. If the resonant frequency is well below the switching frequency, the converter operates as a DAB. Fig. 1.4 shows accurrents through the series inductors in DAB and SRC converters. It can be noted that for the same power transfer, the DAB has smaller RMS currents and larger currents at ZVS transitions. Because the resonant frequency of SRC is higher compared to that of DAB, the inductance can be reduced, resulting in a smaller magnetic flux density (B). However, this further reduces the energy available for ZVS in the SRC. The efficiency can be optimized by running the converter between SRC and DAB operation, as discussed in [97]. By reducing the magnetizing inductance, DCX can be operated as an LLC. The ac currents in the LLC converter have a shape similar to the SRC current, shown in Fig.1.4, with superimposed circulating currents on the primary side, caused by the smaller magnetizing inductance. The circulating current in LLC greatly improves the ZVS range compared to SRC. On the other hand, the imbalance between the primary and secondary currents increases the loss in the transformer.

This thesis is focused on the design and optimization of modular converters based on active

Figure 1.5: Topology that represents a non-isolated example of a high step-down "dc transformer".

bridges that operate well above the resonance frequency. When operated as DCX, the converters feature trapezoidal flat-top ac currents, analogous to DAB current waveforms in Fig. 1.4. This mode of operation features major advantages such as ratio of mean to rms current close to one, wide ZVS range, and simple phase shift control with fixed switching frequency.

#### 1.3 Introduction to Stacked Active Bridge Converters (Part I)

High-step-down or high-step-up dc-dc converters are usually based on transformer-isolated converters, shown in Fig. 1.3, such as dual active bridge (DAB) [20, 22, 95], or resonant LLC converters [92]. The high step-down or step-up transformer is one of the most significant contributors to the overall converter loss and size, which has prompted approaches based on splitting the transformer into stacked units [34, 33, 89, 36].

As an alternative to transformer-isolated converters, various hybrid switched capacitor (SC) based topologies, presented in Fig. 1.5, with inductive elements added to achieve soft charging and soft switching, have been considered for high step-down or step-up conversion applications. For example, switched tank converters [47, 57, 51] are hybrid SC-based converters that operate near the resonant frequency of the LC tank, similar to series resonant converts (SRC). Similar converter architectures, but operating at a switching frequency well above the resonance and with operating and control characteristics similar to DAB converters, are transformerless stacked active bridge (TSAB) converters [99, 98, 100]. Advantages of the above-resonance operation include a

Figure 1.6: Stacked active bridge (SAB) dc-dc converter comprising of 4 series-stacked, capacitively coupled half-bridge inverter modules and 2 parallel-connected full-bridge rectifier modules.

wider ZVS range, reduced RMS currents, regulation capability through simple phase-shift control, and reduced sensitivity to LC parameter variations. On the other hand, operation near resonance leads to zero current switching (ZCS), which can be advantageous in high-current applications. Both switched-tank and TSAB converters exhibit partial hard switching of the inverter devices. An approach based on capacitively coupled active-bridge modules following the input-series output-

parallel (ISOP) architecture is shown in Fig. 1.6. This architecture inherently eliminates the partial hard switching problem by capacitively isolating the inverter from the rectifier bridges. Conduction losses on the rectifier devices present a challenge in high-current, high step-down converters. The ISOP architecture further enables paralleling the rectifier modules on the output dc side, which has advantages in terms of built-in current sharing and the absence of potentials for undesired parasitic oscillations compared to brute-force device paralleling [50].

Capacitively coupled ISOP converter configurations have been considered in telecom rectifier systems, employing SRC modules [5]. The work presented in [40] takes a similar approach for data center applications, using capacitively coupled LLC modules. In general, input-series configurations are realized by stacking the inverter active bridges, as shown in Fig. 3.1. Compared to traditional, single-module inverters, the stacked configuration requires a larger number of switching devices. However, the switching devices used in the stacked inverter configuration are rated at a lower voltage, allowing devices with a much-improved figure of merit (FOM). Splitting the input voltage has a fundamental advantage over single-module inverters in terms of the energy required for zero-voltage switching (ZVS). One may note that stacked inverter configurations can also be combined with isolation transformers, splitting the conversion task between the two stages, as shown in [3] and [42].

# 1.4 Introduction to Modular SiC Based String Inverters for Medium-voltage Transformer-less PV Systems (Part II)

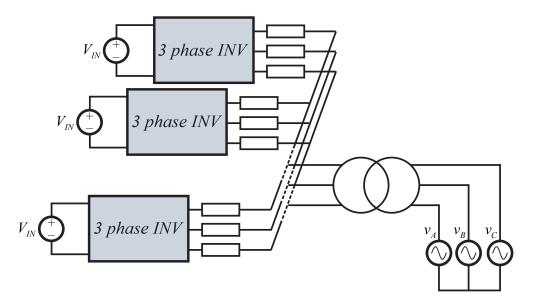

Low-voltage (LV) dc to medium-voltage (MV) ac connection has traditionally been done by paralleling three-phase inverters at LVAC side and stepping the voltage up through line frequency MV transformer, as shown in Fig. 1.7. Hefty line frequency transformer, and considerable conduction loss on LVAC side in this configuration present motivation for looking into alternative approaches to LVDC to MVDC connection.

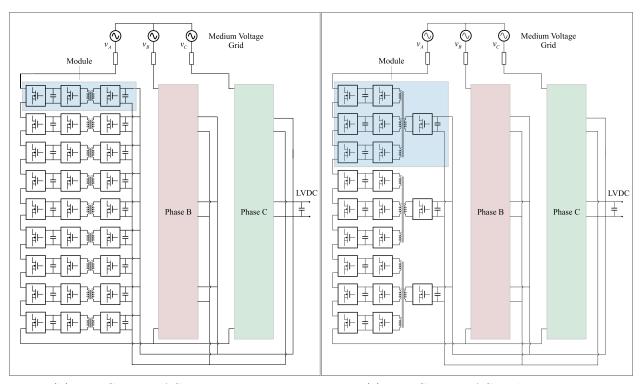

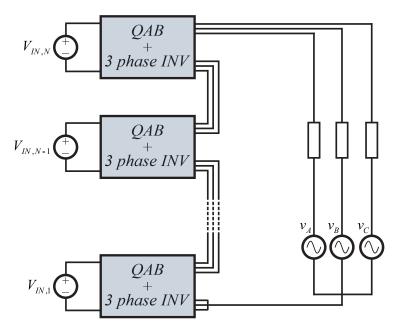

Modular power electronics architectures [43] have lately gained increased attention in electric vehicle (EV) dc charges [86, 54, 41, 15], power distribution for data centers [96], photovoltaic (PV)

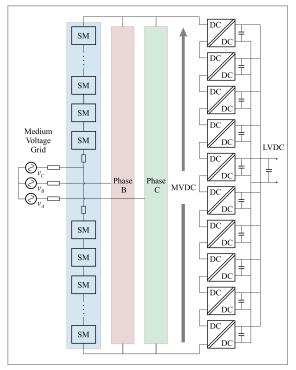

power systems [39, 45, 4], and other applications. Fig. 1.8 shows the advancement of modular architectures. Fig. 1.8a consists of an MVDC bus and a modular inverter. The MV isolation is done on the DCDC side, using input-parallel-output-series (IPOS) configuration of isolated dc to dc converters. The isolated converters operate at medium to relatively high switching frequencies and therefore achieve a significant reduction in size compared to the line frequency transformer in the conventional design [44]. A popular choice for the MV inverter is Modular-Multilevel-Converter (MMC) [35, 53]. Each leg of the inverter is comprised of multiple submodules. The submodules are phase-shifted so that the effective switching frequency is increased, therefore reducing the filter size requirements [62, 63]. Various implementations of the modular inverter are presented in [76, 75]. However, the main disadvantage of this topology is that each of the submodules in the inverter leg contains a capacitor that has to store energy at twice the line frequency, which significantly impacts the size of the converter.

Another option is to avoid creating MV dc bus, by bringing the output of each individual isolated dc to dc converter directly to the submodule, as shown in Fig. 1.8b. This approach relaxes the requirements on the DC capacitance in the submodule. The pulsating power propagates through the isolated converter to the LVDC side. At the LVDC, the three-phase pulsating power cancels,

Figure 1.7: Traditional LVDC to MVAC architecture using line frequency transformer.

(a) LVDC to MVAC architecture 1.

- (b) LVDC to MVAC architecture 2.

- (c) LVDC to MVAC architecture 3.

Figure 1.8: Modular multilevel architectures for interfacing LVDC to MVAC [16].

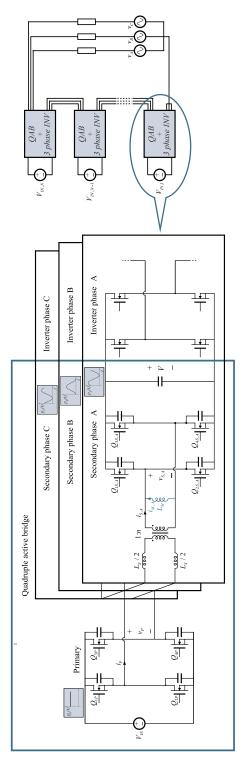

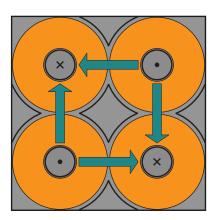

Figure 1.9: Modular multilevel architecture for interfacing LVDC to MVAC based on a three-phase module. The module is based on QAB dcdc converter that provides galvanic isolation between the phases.

leaving only DC power.

The architecture can be further simplified by connecting multiple secondaries of the isolated dc to dc converter to one primary, as presented in Fig. 1.8c, reducing the component count.

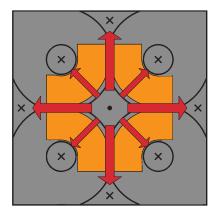

The architecture can be further improved by coupling the secondaries from different phases to the same primary as presented in Fig. 1.9. This topology leverages the three-phase AC power cancelation within a module. The pulsating power propagates through the secondary sides of the isolated converter, but it cancels at the primary, therefore, the primary side bridge processes only DC power.

#### 1.5 Thesis Outline

The thesis is divided into two parts, and it is organized as follows:

Part I is focused on Gallium Nitride (GaN) based high step-down Stacked Active Bridge converters.

Chapter 2 examines voltage scaling of specific on-resistance (RSP) of semiconductor devices within SAB. It is shown how splitting the DC bus voltage across multiple modules in SAB, using lower voltage-rated devices, can be beneficial from the RSP standpoint. It is also shown how using a too large number of stacked modules can have detrimental effects on the overall conduction loss. This implies that an optimum number of stacked modules can be determined, to minimize the conduction loss.

Chapter 3 presents design optimization and analysis of a 400V to 48V, 3kW capacitively coupled (CC) SAB converter. The SAB configuration with CC enables elimination of the high step-down transformer. The only magnetic components in the converter are series inductors that are used for soft charging of blocking capacitors and soft switching of the semiconductor devices. Various implementations of the series inductors are compared in terms of loss and size. Effects of timing mismatch between gate pulses, and other parameters' tolerances in the circuit, on the amount of imbalance among the voltages of the

blocking capacitors, are determined considering zero-voltage transitions (ZVTs).

Chapter 4 discusses design of a 400V to 48V, 3kW galvanically isolated SAB converter. The SAB configuration is utilized to achieve the conversion ratio, while the transformer only needs to provide galvanic isolation. All the transformers and the inductors are integrated together into a single magnetic structure to shrink the footprint of the magnetic components.

• Part II is focused on Modular Silicon Carbide (SiC) Based String Inverters for Medium-voltage Transformer-less PV Systems.

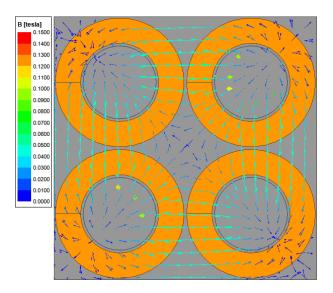

Chapter 5 discusses a stackable modular architecture, where each module has a dc port and three isolated single-phase ac ports [4]. The MV isolation within the module is achieved through Quadruple Active Bridge (QAB) dc to dc converter. The QAB is comprised of one primary and three secondary active bridges arranged around three high-frequency transformers with MV isolation. Power through each of the secondary active bridges consists of both DC and AC components, while the three-phase AC components cancel out at the primary bridge. The pulsating component through the secondary bridges makes ZVS of the devices during low power transfer intervals challenging. The work presented in the thesis focuses on design optimization of the QAB with reduced magnetizing inductance for achieving ZVS of the secondary side devices throughout the line cycle.

# $\begin{array}{c} {\bf Part\ I} \\ {\bf Gallium\ Nitride\ (GaN)\ based\ High\ Step-Down\ Stacked} \\ \\ {\bf Active\ Bridge\ Converters} \end{array}$

#### Chapter 2

#### Scaling of Semiconductor devices in Stacked Active Bridges

This chapter introduces modular active-bridge based dc-transformers. The main focus is on the scaling of the semiconductor devices with a different number of series-stacked modules. Splitting the high-voltage side of the converter between a different number of modules enables the use of different voltage-rated devices. The effect of the number of modules on the performance of the stacked-active-bridge is discussed in this chapter.

#### 2.1 Modularization of active-bridge based dc-transformers

It can be observed from Fig. 1.3 that the converter is comprised of two distinguishable parts: active bridges (inverter and rectifier), and passive components.

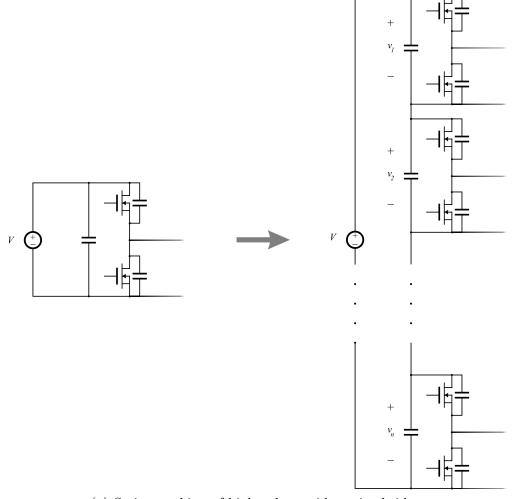

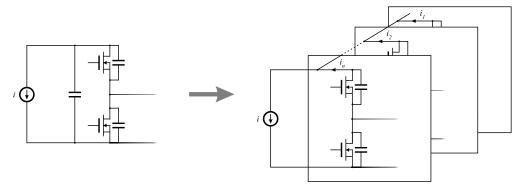

- Active Bridges are composed of semiconductor devices. In high conversion ratio applications, the high-voltage side is normally arranged in a half-bridge configuration, while the low-voltage side is normally arranged in a full-bridge configuration, as shown in Fig. 1.3. In order to maximize the utilization of semiconductor devices, the high voltage side can be split into multiple "modules" connected in series Fig. 2.1a. This configuration is referred to as Stacked-Active-Bridge (SAB) further in the text. Similarly, the low voltage side can be split into multiple parallel connected modules Fig. 2.1b.

- Passive Components are connected between the active bridges. The optimization of passives is dependent on the converter mode of operation (SRC, DAB, LLC, etc.). Mod-

(a) Series stacking of high-voltage side active bridge.

(b) Parallel connection of low-voltage side active bridges.

Figure 2.1: Modular connection of active bridges.

ularization of active bridges can also lead to improvements in the design of passives. For example, integration of the magnetic components, or elimination of the transformer.

# 2.2 Voltage Scaling of Semiconductor Devices with Splitting the High-Voltage Side with SAB - Theoretical Perspective

The specific on-resistance (RSP) of a semiconductor device is typically described with (2.1) [30, 58].

$$AR_{ON} = \frac{k}{\mu_n \epsilon_S E^3} V_B^2. \tag{2.1}$$

Product of  $R_{ON}$  (resistance of the drift region), and A (active area of the device), in (2.1) represents RSP. The RSP is dependent on:

#### • Semiconductor property related parameters:

- \* k a constant dependent on the process,

- \*  $\mu_n$  the electron mobility,

- \*  $\epsilon_S$  the semiconductor permittivity,

- \*  $E_c$  the critical field for avalanche breakdown.

#### ullet $V_B$ - the device breakdown voltage.

Assuming fixed semiconductor property and process related parameters, it is of interest to investigate how does the RSP scales with the blocking voltage of the device. Using different blocking voltage devices is possible by staking multiple modules in series. The blocking voltage scaling analysis is normalized to a fixed total semiconductor area, and the total conduction loss of the stacked active bridge is compared for different number of modules n.

According to (2.1), the conduction loss of a single module blocking the entire DC bus voltage is directly proportional to:

$$P_{cond,1} \sim \frac{1}{A} \frac{k}{\mu_n \epsilon_S E^3} V_B^2. \tag{2.2}$$

Considering the same total active semiconductor area A, the conduction loss of n series-sacked modules that block the same DC bus voltage is proportional to:

$$P_{cond,1} \sim n \frac{1}{\left(\frac{A}{n}\right)} \frac{k}{\mu_n \epsilon_S E^3} \left(\frac{V_B}{n}\right)^2.$$

(2.3)

Which leads to conclusion that the total conduction loss in unaffected by the number of modules:

$$\frac{P_{cond,n}}{P_{cond,1}} = 1. (2.4)$$

This conclusion is based on theoretical relation given in (2.1), which only approximately relates the blocking voltage to RSP of a device. Further investigation is presented in the following subsection, to revisit equation (2.1), which will give a more accurate insight in the voltage scaling of the devices.

# 2.3 Voltage Scaling of Semiconductor Devices with Splitting the High-Voltage Side with SAB - Revisited

Gallium Nitride (GaN) has been emerging technology over the past years, and it is continuing to grow. Wide band-gap (WBG) of GaN results in increased critical electric field by an order-of-magnitude. This leads to three orders-of-magnitude reduction in RSP [30]. RSP in lateral GaN devices is further reduced thanks to higher electron mobility in the two-dimensional electron gas (2DEG).

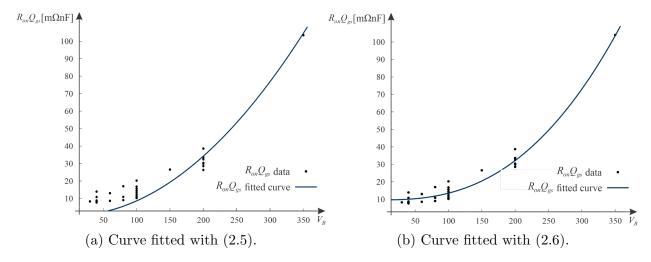

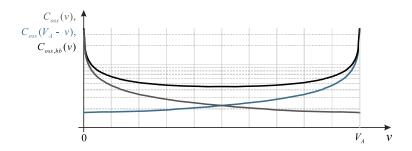

Efficient power conversion (EPC) has a wide portfolio of GaN devices ranging from 30V to 350V, in various sizes. Fig. 2.2 shows  $R_{ON}Q_{GS}$  dependence on blockinkg voltage  $V_B$ . The datapoints plotted with dots is pulled from EPC website [2].  $Q_{GS}$  in the figure represents the gate-source charge. Since the information about active die area of the device is not easily accessible, it is assumed that  $Q_{GS} \sim A$ . Considering quadratic dependence of RSP to  $V_B$ , and a constant K, shown in (2.5), the curve-fit overlapped with the data is shown in Fig. 2.2a.

$$Q_{gs}R_{on} = KV_B^2, (2.5)$$

One can note that the curve-fit given with (2.5) does not accurately reflect the data. The curve fit

Figure 2.2: Voltage scaling of the RSP.

equation can be expanded to a more generalized exponential form:

$$Q_{qs}R_{on} = KV_B^{\alpha} + C, (2.6)$$

where K,  $\alpha$  and C are parameters determined by fitting the data. The curve-fit, overlapped with the data is presented in Fig.2.2b, showing very good matching. Interestingly, the exponent of the fitted curve is given with:

$$\alpha = 2.55,\tag{2.7}$$

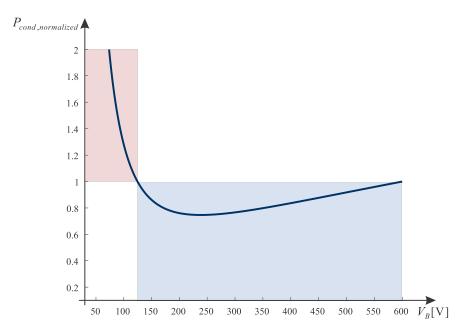

contrary to quadratic dependence, assumed in (2.1). Fig. 2.3 shows the normalized conduction loss dependence of a SAB on the blocking voltage of the devices used. A lower blocking voltage device on the x-axis implies a higher number of modules, while the total active semiconductor area is kept constant. The two regions of the curve can be distinguished:

• Low blocking voltage region - dominated by constant C term in (2.6). This phenomenon happens due to metalization and die-to-pin interconnects. In smaller voltage-rated devices this effect dominates the conduction loss over the loss in the channel of the semiconductor. Therefore, using a large number of smaller voltage-rated devices in series, increases the total conduction loss in SAB.

Figure 2.3: Scaling of the normalized conduction loss of the SAB with blocking voltage of the devices used in the stack.

High blocking voltage region is dominated by the exponential term in (2.6). As it was shown previously with (2.4), if the exponent α = 2, the total conduction loss in the channel does not change with the voltage rating of the devices used in the stacked active bridge. However, if α > 2, as in the case of (2.7), the overall conduction loss reduces, with using a bigger number of smaller voltage-rated devices in SAB.

As illustrated in Fig. 2.3 with the blue region, splitting the DC bus voltage in multiple modules can be beneficial form the conduction loss point of view. Contrary, using too many modules can have a detrimental effect on the overall conduction loss, as shown in the red region in Fig. 2.3.

# 2.4 Energy stored in SAB

Aside from voltage scaling in terms of conduction loss, which has been discussed in the previous section, scaling of the total energy stored in a SAB is an important aspect. Even though the energy stored in an active bridge does not directly impact loss in the devices when soft-switched topologies are considered, it is directly proportional to the amount of inductive energy, that needs

to be stored in the circuit, to achieve soft switching. Energy stored in a single module active bridge is given with:

$$E_{C_{oss,1}} = C_{oss,1} V_{IN}^2, (2.8)$$

where  $C_{oss,1}$  is a parasitic drain to source capacitance of a device in a single module active bridge. Now, considering a SAB with n modules, the total energy stored is:

$$E_{C_{oss,n}} = \frac{C_{oss,nV_{IN}^2}}{2n},$$

(2.9)

where  $C_{oss,n}$  is a parasitic drain to source capacitance of a device in an n-module SAB. Therefore, the ratio of stored energy using n modules, and stored energy using a single module is given with:

$$\frac{E_{C_{oss,n}}}{E_{C_{oss,1}}} = \frac{C_{oss,n}}{nC_{oss,n}},\tag{2.10}$$

In order to benefit from using an n-module SAB, in terms of total stored energy, the parasitic capacitance of a device used in the SAB, needs to be smaller than n times parasitic capacitance of a device used in a single module AB.

$$C_{oss,n} < nC_{oss,1} \tag{2.11}$$

#### 2.5 Chapter Summary and Conclusions

Scaling of the semiconductor devices with a different number of series-stacked modules is discussed in this chapter. Different voltage-rated devices can be used by splitting the high-voltage side of the converter between different number of modules. It is shown how the total specific on-resistance (RSP) of the stack can be reduced with the number of modules. However, a too large number of modules can lead to significant increase in RSP. Therefore an optimum number of modules in the stacked-active-bridge can be selected to minimize RSP.

### Chapter 3

#### 400 V-to-48 V Stacked Active Bridge Converter

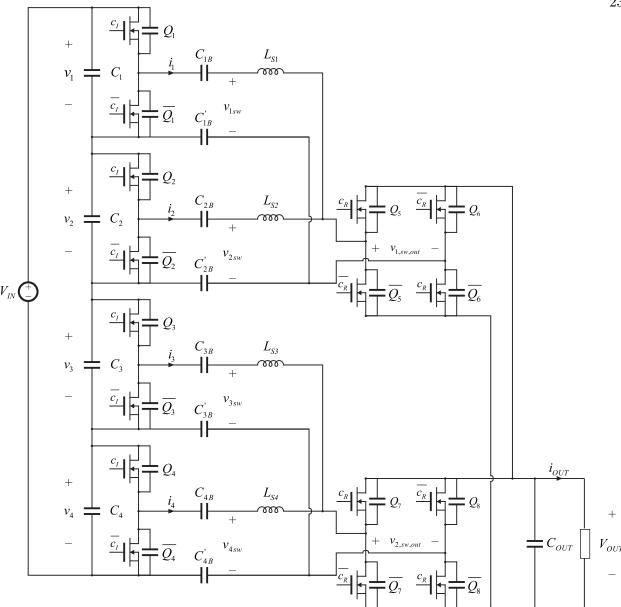

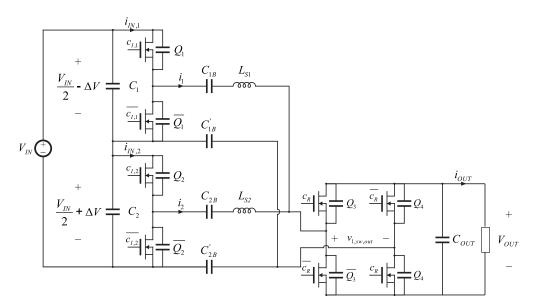

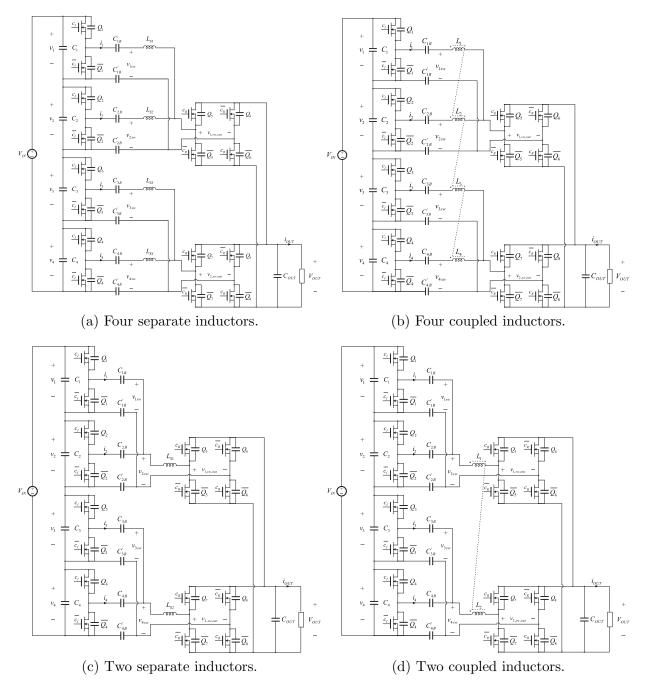

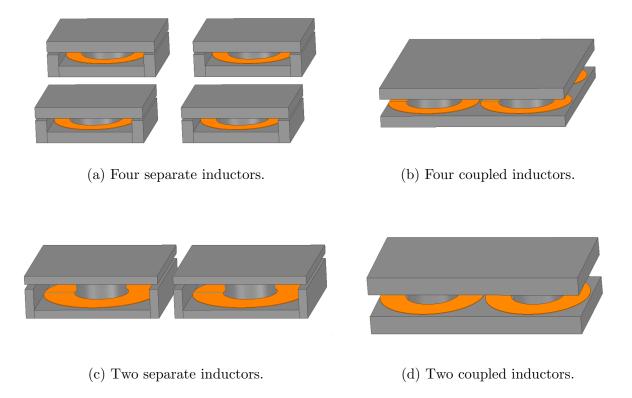

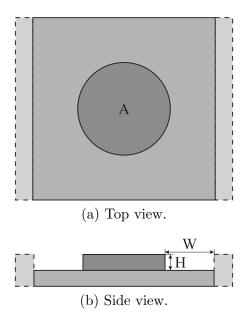

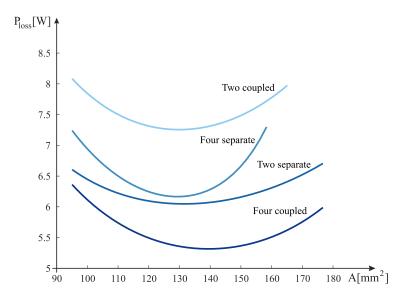

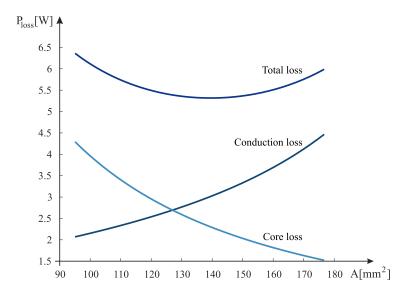

This chapter is focused on the capacitively coupled Stacket-Active-Bridge (SAB) converter shown in Fig. 3.1. The converter is comprised of n=4 series-stacked, capacitively coupled half-bridge inverter modules and m=2 parallel-connected full-bridge rectifier modules. As opposed to the similar approaches reported in [5, 40], the converter is operated well above the series resonance so that the operating waveforms and the control characteristics are similar to the DAB converter. All of the inverter modules are controlled with the same square-wave control signals, and all the output rectifier modules are controlled with the same square-wave control signals, while the power flow through the converter is controlled by the phase-shift between the inverter and the rectifier control signals. In addition to the simple, DAB-like operation of the SAB configuration shown in Fig. 3.1, the key contributions of this chapter include an analysis of the natural voltage-sharing property of the converter in the presence of timing mismatches, and a novel realization of the series inductors integrated on a custom magnetic core.

A detailed analysis is conducted to examine the effects of timing mismatches among the gatedriver control signals on the voltage sharing among the stacked inverter modules. Similar to [6], the analysis is carried out considering ZVTs of the inverter bridges. It is shown that in practice the converter does not require an active control to ensure voltage balancing.

Four options are considered for the series inductors placement and implementation, and the options are compared in terms of loss, while keeping the same boxed volume. The most effective solution, which is based on integration of the inductors on a custom core, is selected and

Figure 3.1: Stacked active bridge (SAB) dc-dc converter comprising n=4 series-stacked, capacitively coupled half-bridge inverter modules and m=2 parallel-connected full-bridge rectifier modules.

implemented in a hardware prototype.

The chapter is organized as follows. Section 3.1 describes operation of the SAB converter shown in Fig. 3.1. Section 3.2 focuses on the analysis of the input capacitor voltage balancing in the presence of timing mismatches among control signals. Various options for the realization of the

series inductors are discussed and compared in Section 3.3. Experimental results for a 400-to- $48\,\mathrm{V}$ ,  $3\,\mathrm{kW}$ ,  $400\,\mathrm{W/in^3}$  SAB prototype operating at  $400\,\mathrm{kHz}$  using GaN devices, and demonstrating a flat efficiency curve with 99% peak efficiency, are presented in Section 3.4. Section 3.5 concludes this chapter.

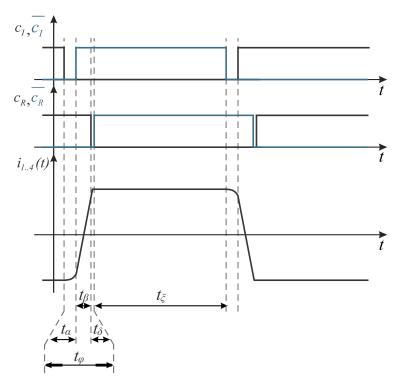

#### 3.1 SAB converter operation

In steady-state operation of the SAB converter shown in Fig. 3.1, the input voltage is ideally equally shared among the inverter modules,  $v_{1..n} = V_{in}/n$ . Similarly, the output current is equally shared among the rectifier modules. As shown in Fig. 3.2, complementary square-wave signals  $c_I$  and  $\overline{c_I}$  control the top and the bottom devices, respectively, in all the inverter active-bridges, while similarly  $c_R$  and  $\overline{c_R}$  control the rectifier active-bridge devices. Similar to the standard phase-shift control of DAB converters, there are only four control signals regardless of the numbers of inverter or rectifier modules, and the phase shift between the inverter and the rectifier bridges controls the power flow through the converter [20, 73]. It would also be possible to operate the inverter bridges with interleaved gate pulses, potentially allowing for reduced switching frequency or reduced ripples, but at the expense of increased number of control signals and complexity. Fig. 3.2 also shows a series inductor current waveform, where  $t_{\alpha}$  represents the inverter-side zero voltage transition (ZVT) interval of the inverter bridges,  $t_{\beta}$  is the ramp-up interval of the inductor current,  $t_{\delta}$  is the ZVT interval of the rectifier bridges, and  $t_{\xi}$  is the current flat-top interval.

Similar to a DAB converter, the power transfer characteristic is given by

$$P = \frac{nV_{OUT}^2}{2\pi f_{sw}L_S} \varphi \left(1 - \frac{\varphi}{\pi}\right), \tag{3.1}$$

where  $\varphi = t_{\varphi} 2\pi f_{sw}$  is the phase shift, and n is the number of inverter modules. With an appropriately controlled phase shift, the nominal conversion ratio is simply

$$M = \frac{V_{OUT}}{V_{IN}} = \frac{1}{2n}. (3.2)$$

The steady-state characteristics (3.1), (3.2) are shown for the SAB converter of Fig. 3.1 where the inverter modules employ half-bridge stages and the rectifier modules are based on full-bridge

Figure 3.2: Control signals  $c_I$ ,  $\overline{c_I}$  for the inverter modules, and  $c_R$ ,  $\overline{c_R}$ , for the rectifier modules, together with the inductor currents  $i_{1..4}$  in the SAB converter of Fig. 3.1.

stages. Variations of the SAB converter topology can be constructed where the inverter or the rectifier modules are based on either half-bridge or full-bridge stages.

A minimum power needed to achieve ZVS of the inverter-side devices can be found approximately as

$$P_{crit} \approx \frac{V_{IN}^2}{2n} \sqrt{\frac{C_{HB}}{L_S}},\tag{3.3}$$

where  $C_{HB}$  is the equivalent half-bridge switch-node capacitance [21], which is due to the device output capacitance and parasitic PCB capacitance, and  $L_S$  is the series inductance, which can be selected based on the ZVS condition in (3.3). A larger inductance leads to ZVS operation over a wider range of loads, but a larger size is required to realize the series inductor. This trade-off is exemplified in the experimental prototype addressed in Sections 3.3 and 3.4.

It is of interest to compare (3.3) to the ZVS condition expressed as the minimum power  $P_{crit,conv}$  for a conventional DAB configuration with a single inverter module and an n:1 step-

down transformer. Assuming the same  $C_{HB}$  capacitance, and the same switching frequency and phase shift for the same power transfer,

$$\frac{P_{crit}}{P_{crit,conv}} \approx \frac{1}{\sqrt{n}},$$

(3.4)

which shows an advantage of the stacked inverters in terms of the power required to achieve ZVS. This advantage can be utilized either to achieve an extended ZVS range, or to reduce the total energy stored in the series inductors. Furthermore, upon loss of ZVS, the hard-switching losses at light loads are reduced in the stacked-inverter configuration.

# 3.2 Capacitor voltage balancing

As mentioned in the previous section, all the inverter modules are controlled with the same control signals, and the input voltage is shared equally among the modules,  $v_{1..n} = V_{IN}/n$ . The control signals propagate from a controller through PCB traces, isolators and gate drivers. Any mismatches among propagation delays result in effective on/off timing mismatches among the inverter modules, which in turn may lead to an imbalance among the capacitor voltages  $v_{1..n}$ . Additionally, a mismatch between the inductances  $L_{1..n}$ , as well as halfbridge switch-node capacitances  $C_{HB}$ ,

Figure 3.3: SAB converter with two inverter modules having a timing mismatch between the control signals  $c_{I,1}$  and  $c_{I,2}$ .

Figure 3.4: Control signals  $c_{I,1}$ ,  $\overline{c_{I,1}}$  and  $c_{I,2}$ ,  $\overline{c_{I,2}}$  for the inverter modules, and  $c_R$ ,  $\overline{c_R}$ , for the rectifier modules, together with the input currents  $i_{IN,1}$ ,  $i_{IN,2}$ , and the switching node voltages  $v_{sw,1}$ ,  $v_{sw,2}$  in the SAB converter of Fig. 3.3 under imbalanced conditions due to timing mismatches.

cause imbalance among the voltages. In order to investigate the effects of these nonidealities, a simplified configuration with two inverter modules, as shown in Fig. 3.3, is considered for simplicity.

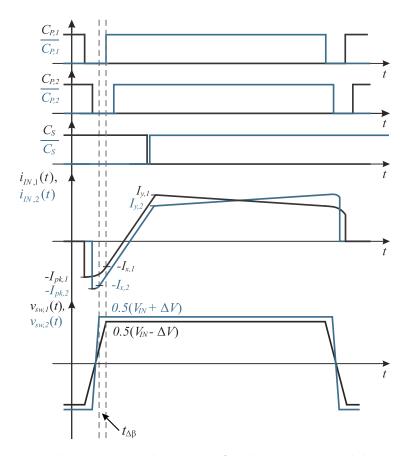

Fig. 3.4 shows theoretical waveforms of the mismatched gate pulses, and their effect on the switch-node voltages and the inductor currents. The timing mismatch acts as a mismatch between phase shifts of the modules with respect to the rectifier, which can be viewed as a difference between the  $t_{\beta}$  intervals of the two modules, shown as  $t_{\Delta\beta}$  in Fig. 3.4. Considering idealized waveforms, without taking into account the inverter-side zero-voltage transition (ZVT) intervals, the timing mismatch would result in diverging capacitor voltages. However, taking the resonant transitions into account, it is found that the capacitor voltages converge to steady-state values only slightly away from the ideal, balanced conditions.

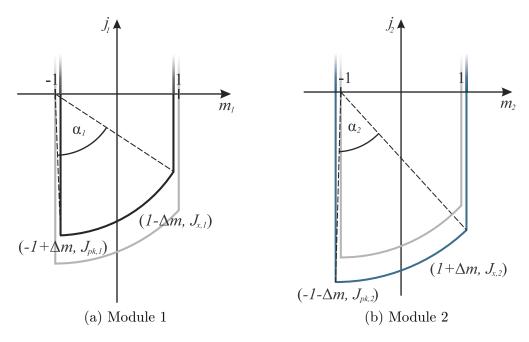

Figure 3.5: State-plane diagrams for the normalized switching node voltages  $v_{sw,1}$ ,  $v_{sw,2}$ , and inductor currents  $i_1$ ,  $i_2$ , corresponding to the waveforms under imbalanced condition shown in Fig. 3.4. The state-plane trajectories when the voltages are perfectly balanced are shown in light-gray color.

In order to find a steady-state solution for the imbalance  $\Delta V$  as a function of the timing mismatch  $\Delta t_{\beta}$ , each module can be considered separately using state-plane analysis, as shown in Fig. 3.5. In the state-plane analysis, a standard normalization is applied using the base values  $V_{base} = 2V_{OUT}$  and  $I_{base} = \frac{V_{base}}{R_0}$ , where  $R_0 = \sqrt{L_S/C_{HB}}$ .

A set of expressions derived from the state-plane diagrams is provided in Appendix A. For a given  $t_{\Delta\beta}$ ,  $\Delta V$  can be found from the charge balance conditions for the inverter input capacitors, i.e., by equating the average input currents of the two inverter modules,

$$I_{IN.1} = I_{IN.2}. (3.5)$$

The solution can be found using numerical iterations, as described in Appendix A.

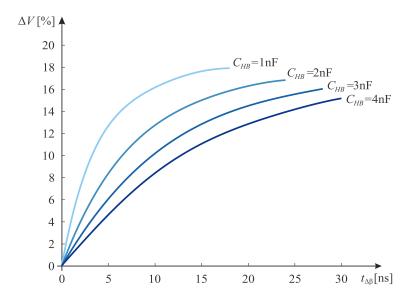

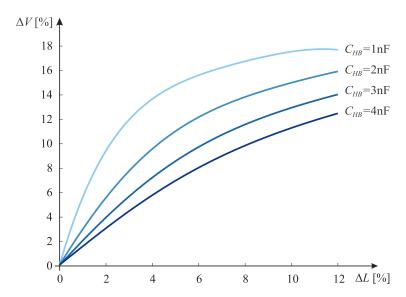

The analysis results are presented in Fig. 3.6 where  $\Delta V/(2V_{OUT})$  is shown as a function of the timing mismatch in nanoseconds, for several different values of the half-bridge switch-node capacitance  $C_{HB}$ . As expected, a longer mismatch results in a larger voltage imbalance. A larger

$C_{HB}$  capacitance results in a longer resonant transition interval, which in turn means that a larger timing mismatch can be tolerated.

The effect of the mismatch between the inductances on the imbalance among the voltages can be analyzed by setting  $t_{\Delta\beta}=0$  and using different characteristic impedances for normalizing the currents in the two cases,  $R_{0,1}=\sqrt{L_{S1}/C_{HB}}$  and  $R_{0,2}=\sqrt{L_{S2}/C_{HB}}$ , where  $L_{S1}=L_S+\Delta L_S/2$  and  $L_{S2}=L_S-\Delta L_S/2$ . Fig. 3.7 shows the results of the inductance mismatch analysis, where  $\Delta V/(2V_{OUT})$  is shown as a function of the percentage inductance mismatch  $\Delta L_S/L_s$ , for several different values of the half-bridge switch-node capacitance  $C_{HB}$ . Similar to the timing mismatch results, a larger half-bridge capacitance implies a larger tolerance to inductance mismatch.

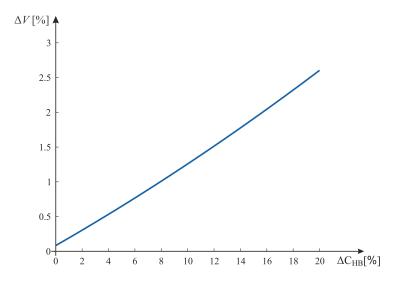

Similarly, the effect of the mismatch between the half-bridge switch-node capacitances on the imbalance among the voltages can be analyzed using different characteristic impedances for normalizing the currents,  $R_{0,1} = \sqrt{L/C_{HB1}}$  and  $R_{0,2} = \sqrt{L/C_{HB2}}$ , where  $C_{HB1} = C_{HB} - \Delta C_{HB}/2$  and  $C_{HB2} = C_{HB} + \Delta C_{HB}/2$ . The results are shown in Fig. 3.8 where  $\Delta V/(2V_{OUT})$  is shown as a function of the capacitance percent mismatch  $\Delta C_{HB}/C_{HB}$ .

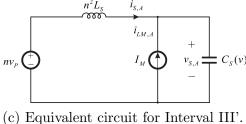

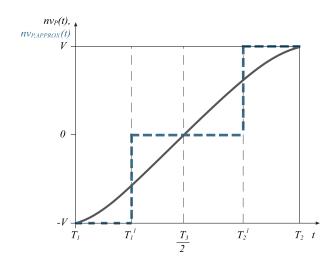

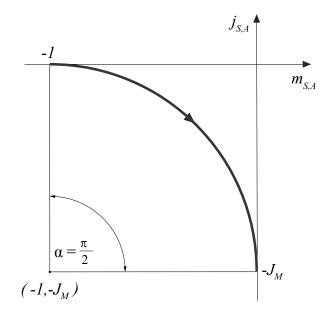

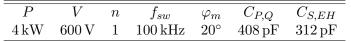

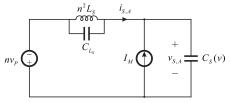

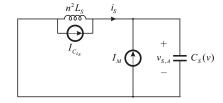

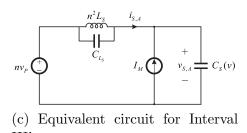

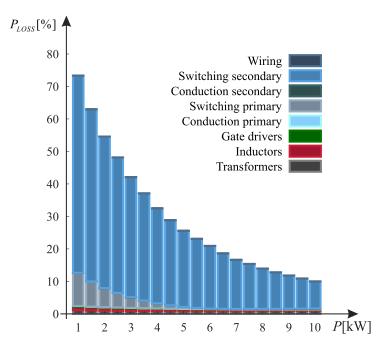

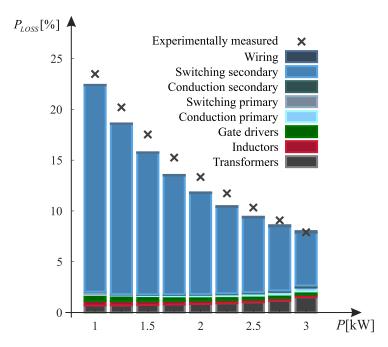

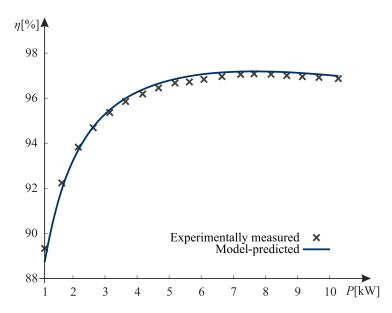

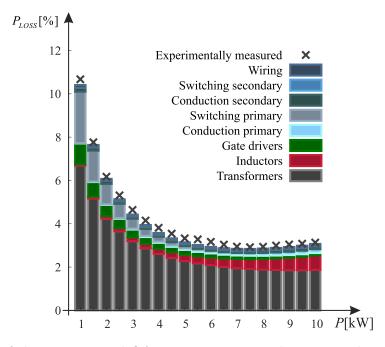

In practice, as discussed further in the context of the experimental prototype described in