# A Methodology for Characterizing and Modeling Inverters for Grid Integration Studies using Power Hardware-in-the-Loop

by

Daniel V. Terlip

B.S. Electrical Engineering University of Oklahoma, 2010

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL, COMPUTER AND ENERGY ENGINEERING IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

> MASTER OF SCIENCE IN ELECTRICAL ENGINEERING AT THE UNIVERSITY OF COLORADO

> > NOVEMBER 2011

This thesis entitled:

A Methodology for Characterizing and Modeling Inverters for Grid Integration Studies using Power Hardware-in-the-Loop

written by Daniel Terlip

has been approved for the Department of Electrical, Computer and Energy Engineering

Dragan Maksimovic, Committee Chair

Regan Zane, Committee Member

Date:\_\_\_\_\_

The final copy of this thesis has been examined by the signatories, and we find that both the content and the form meet acceptable presentation standards

of scholarly work in the above mentioned discipline.

## Abstract

Terlip, Daniel V. (Masters, Electrical Engineering, Department of Electrical, Computer and Energy Engineering)

A Methodology for Characterizing and Modeling Inverters for Grid Integration Studies using Power Hardware-in-the-Loop

This thesis directed by Professor Dragan Maksimovic

A methodology is proposed and executed to characterize and model inverters for grid integration studies using Power Hardware-in-the-Loop. A Hardware-in-the-Loop system is configured using a Real-Time Data System (RTDS), grid simulator, load bank, photovoltaic inverter and bus system. A characterization scheme is developed on the RTDS that is based on the abnormal grid conditions and tests outlined in IEEE 1547 Standard for Interconnecting Distributed Resources with Electric Power Systems. The RTDS is then used to control both the grid simulator and load bank. It was found that it is possible to characterize the inverter's grid protection controller's response to abnormal voltage, abnormal frequency and islanding conditions without prior knowledge of intimate control algorithms or hardware configuration.

A model of the system was then created in Matlab Simulink using the data obtained from the characterization process. The inverter is modeled on a high level as a controlled current source and a controller for the inverter model is developed such that the detection and response to the stated abnormal grid conditions of the model directly mimics that of the actual inverter.

## Dedication

This work is dedicated to those who expend tireless effort

making the world a more sustainable place,

for all living creatures.

## Acknowledgements

The author would like to acknowledge the contributions of everyone that helped make this work a reality.

Dr. Dragan Maksimovic and Dr. Regan Zane of the University of Colorado have an uncanny ability to find time in their incredibly busy schedules to help a working student.

Dr. Ben Kroposki of the National Renewable Energy Laboratory has incredible vision and was instrumental in the scope and design of this work. His advice was always helpful and grounding.

The crew at the Distributed Energy Resources Testing Facility at the National Renewable Energy Laboratoy, Mari Shirazi, Greg Martin, Kevin Harrison, Bob Hansen, Sudipta Chakraborty, Blake Lundstrom, Pete Gotseff, Mike Peters, Michael Coddington and Bill Kramer are like a family to me. They offered unyielding support and patience to an endlessly curious intern. I've never learned so much in such a short period of time.

My mom and dad have been great parents that not only made college possible for me, but were incredibly supportive in the decisions I've made. I can't thank them enough.

My friends were also very supportive, especially those that sat through my defense presentation trial runs, even though they had no prior knowledge of the topic.

Thank you all.

# Contents

| 1 Introduction |       |                 |                                                                                              |  |

|----------------|-------|-----------------|----------------------------------------------------------------------------------------------|--|

|                | 1.1   | The             | Changing Electric Power System1                                                              |  |

|                | 1.2   | Rele            | evant Research5                                                                              |  |

|                | 1.3   | Mot             | ivation7                                                                                     |  |

|                | 1.4   | HIL             | Overview                                                                                     |  |

|                | 1.5   | Stat            | ement of Work11                                                                              |  |

| 2              | Pho   | tovol           | taic Systems and IEEE Standard 154712                                                        |  |

|                | 2.1   | PV S            | Systems12                                                                                    |  |

|                | 2.1.  | 1               | Inverters                                                                                    |  |

|                | 2.2   | IEEE            | $\pm$ 1547 Standard for Interconnecting Distributed Resources with Electric Power Systems 17 |  |

|                | 2.2.1 |                 | Temperature Tests                                                                            |  |

|                | 2.2.  | 2               | Abnormal Voltage Tests                                                                       |  |

|                | 2.2.3 |                 | Abnormal Frequency Tests19                                                                   |  |

|                | 2.2.  | 4               | Synchronization20                                                                            |  |

|                | 2.2.5 |                 | Interconnection Integrity21                                                                  |  |

|                | 2.2.6 |                 | DC Injection                                                                                 |  |

|                | 2.2.7 |                 | Unintentional Islanding22                                                                    |  |

|                | 2.2.  | 8               | Reverse Power                                                                                |  |

|                | 2.2.9 |                 | Open Phase Test24                                                                            |  |

|                | 2.2.  | 10              | Reconnection                                                                                 |  |

|                | 2.2.  | 11              | Harmonics24                                                                                  |  |

| 3              | Har   | dwar            | e-in-the-Loop System Realization26                                                           |  |

|                | 3.1   | Ove             | rview                                                                                        |  |

|                | 3.2   | Grid            | l Simulator27                                                                                |  |

|                | 3.2.  | 1               | Hardware27                                                                                   |  |

|                | 3.2.  | 2               | Software                                                                                     |  |

|                | 3.3   | Load            | d Bank54                                                                                     |  |

|                | 3.4   | Rea             | I Time Data System68                                                                         |  |

|                | 3.5   | Inve            | rter70                                                                                       |  |

|                | 3.6   | 3.6 Connections |                                                                                              |  |

|                | 3.7   | Data            | a Acquisition                                                                                |  |

|   | 3.7.  | 1     | Measuring Devices           | 73 |

|---|-------|-------|-----------------------------|----|

|   | 3.7.  | 2     | Triggering                  | 74 |

|   | 3.8   | Inte  | gration of Components       | 74 |

|   | 3.8.  | 1     | Power Flow                  | 74 |

|   | 3.8.  | 2     | Control/Order of Operations | 76 |

|   | 3.9   | Sun   | nmary                       | 77 |

| 4 | Tes   | t Res | ults                        | 78 |

|   | 4.1   | Rec   | onnection Time              | 78 |

|   | 4.2   | Abr   | ormal Voltage               | 79 |

|   | 4.2.  | 1     | Magnitude                   | 79 |

|   | 4.2.  | 2     | Time                        | 82 |

|   | 4.3   | Abr   | ormal Frequency             |    |

|   | 4.3.  | 1     | Magnitude                   |    |

|   | 4.3.  | 2     | Time                        | 92 |

|   | 4.4   | Ant   | i-Islanding                 | 95 |

|   | 4.5   | Sun   | nmary of Test Results       | 96 |

| 5 | Mo    | delin | g the System                |    |

|   | 5.1.  | 1     | PHIL for Modeling           | 98 |

|   | 5.1.2 |       | Modeling Constraints        | 99 |

|   | 5.2   | Арр   | proach                      | 99 |

|   | 5.2.  | 1     | Modeling Software           | 99 |

|   | 5.2.  | 2     | Modeling the Grid Simulator |    |

|   | 5.2.  | 3     | Modeling the Inverter       |    |

|   | 5.3   | Res   | ults                        |    |

|   | 5.4   | Disc  | cussion of Results          |    |

|   | 5.5   | Мо    | difications to the Model    |    |

|   | 5.5.  | 1     | Frequency                   |    |

|   | 5.5.  | 2     | Voltage                     |    |

|   | 5.6   | Sun   | nmary                       |    |

| 6 | Con   | clusi | ons and Recommendations     |    |

|   | 6.1   | Con   | clusions                    |    |

|   | 6.2   | Rec   | ommendations                |    |

| 7 | Work  | rks Cited                        | 114 |

|---|-------|----------------------------------|-----|

| 8 | Appe  | endix                            | 118 |

|   | 8.1   | Index of Abbreviations           | 118 |

|   | 8.2   | Software code                    | 118 |

|   | 8.2.1 | 1 Anti-Islanding Analysis Script | 118 |

|   | 8.2.2 | 2 Frequency Ramp Analysis Script | 119 |

|   | 8.2.3 | 3 Frequency Step Analysis Script | 120 |

|   | 8.2.4 | 4 Voltage Ramp Analysis Script   | 122 |

|   | 8.2.5 | 5 Voltage Step Analysis Script   |     |

# List of Figures

| Figure 2-1 Residential Split-Phase Configuration              | 16 |

|---------------------------------------------------------------|----|

| Figure 2-2 Anti-Islanding Test Circuit                        | 23 |

| Figure 3-1 PHIL Set-Up                                        | 27 |

| Figure 3-2 HIL to UPC-32 Connection Diagram                   | 29 |

| Figure 3-3: Grid Simulator Master Subsystem                   |    |

| Figure 3-4: Test Selector Subsystem                           |    |

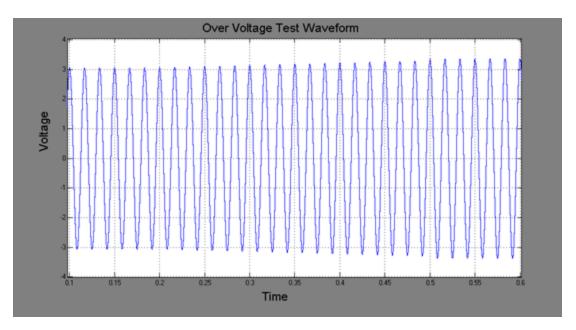

| Figure 3-5: Over Voltage Waveform generated in Simulink       | 41 |

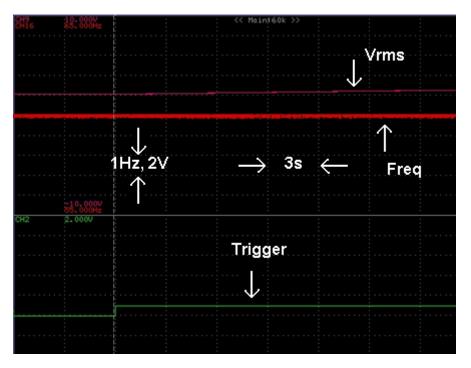

| Figure 3-6: HIL Overvoltage Output                            |    |

| Figure 3-7 Grid Simulator Output of Over Voltage Ramp         | 42 |

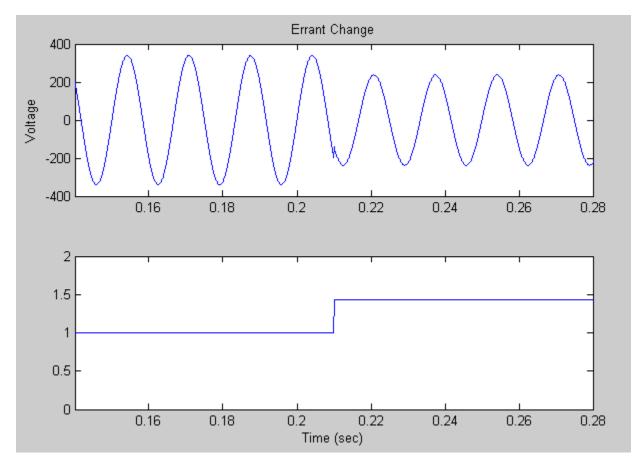

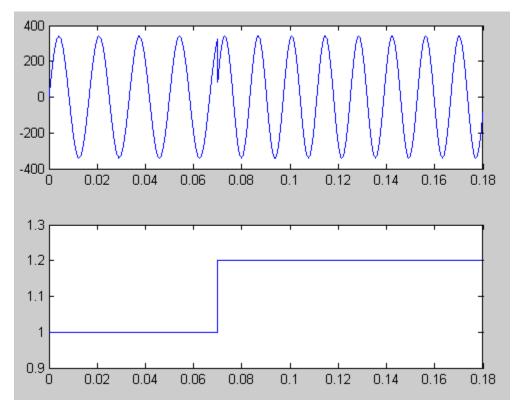

| Figure 3-8 Errant Undervoltage Step in Simulink               | 43 |

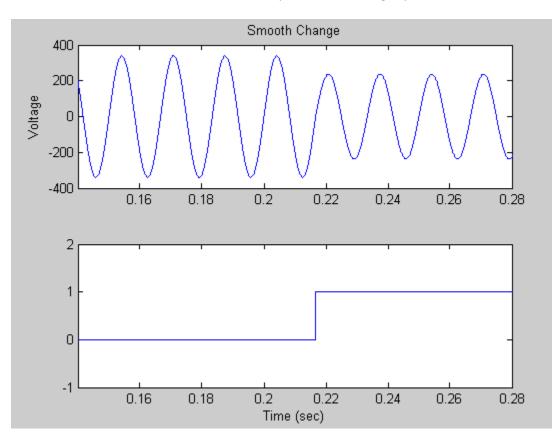

| Figure 3-9 Undervoltage Smooth Transition in Simulink         | 44 |

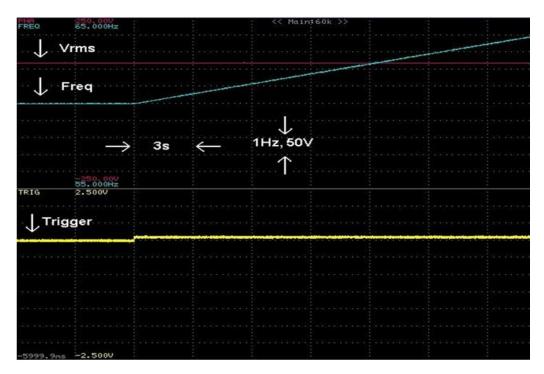

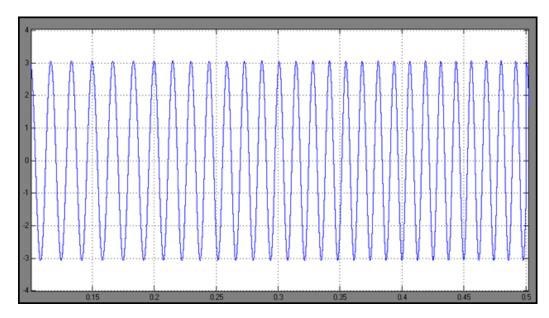

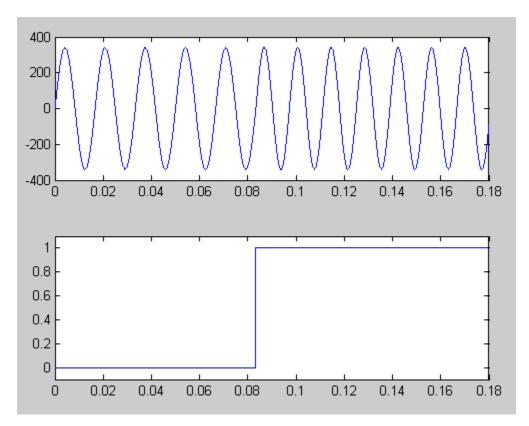

| Figure 3-10 Frequency Increase Smooth Transition              | 48 |

| Figure 3-11 Frequency Increase Sine Wave                      | 48 |

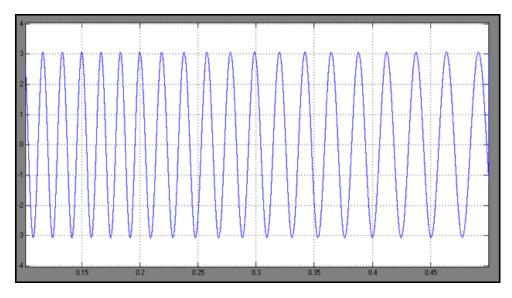

| Figure 3-12 Frequency Decrease Smooth Transition              | 49 |

| Figure 3-13 Frequency Decrease Smooth Transition              | 50 |

| Figure 3-14 Frequency Step Discontinuous Transition           | 52 |

| Figure 3-15 Frequency Step Smooth Transition                  | 53 |

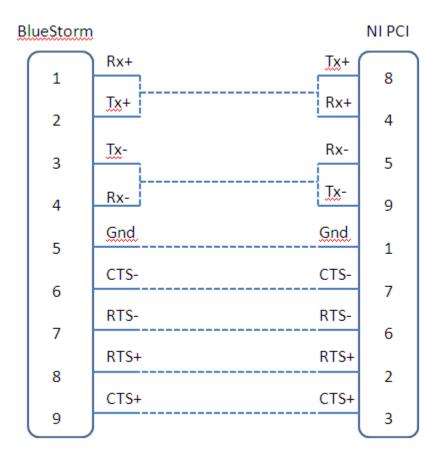

| Figure 3-16 BlueStorm and NI PCI Connection Diagram           | 56 |

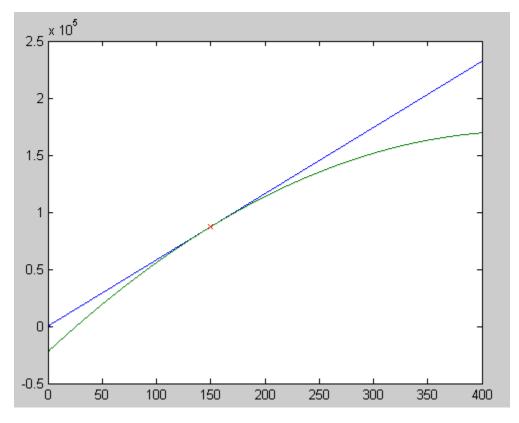

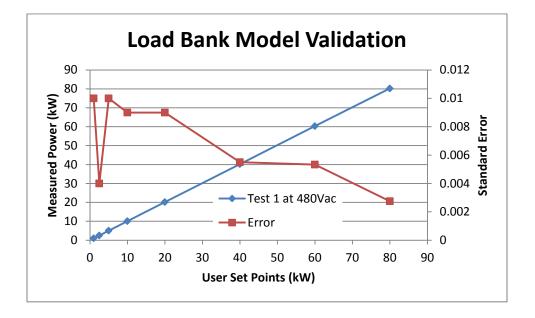

| Figure 3-17 Load Bank Model Validation                        | 60 |

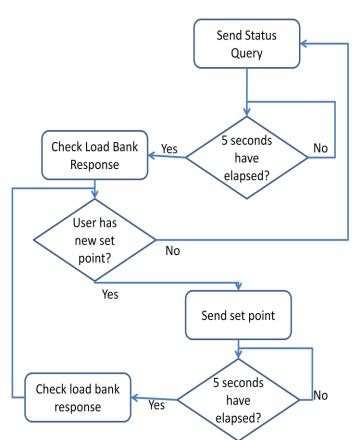

| Figure 3-18 Load Bank Program Operation Flow Diagram          | 62 |

| Figure 3-19 Typical 3-Phase Circuit with Delta-Connected Load | 65 |

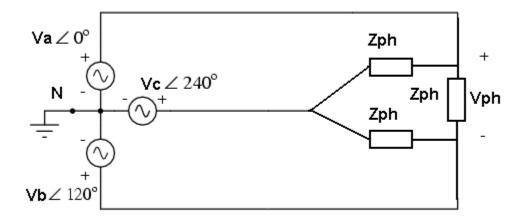

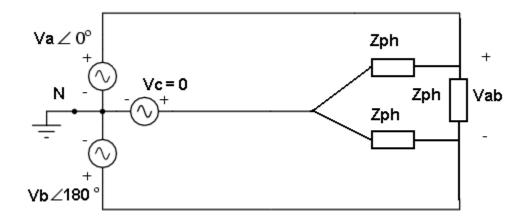

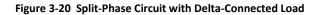

| Figure 3-20 Split-Phase Circuit with Delta-Connected Load     | 65 |

| Figure 3-21 Simulated EPS Power Connections                   | 72 |

| Figure 4-1 Abnormal Voltage Magnitude Test Script Image       | 81 |

| Figure 4-2 Overvoltage Step Change                            |    |

| Figure 4-3 Overvoltage Time Test Graph                        |    |

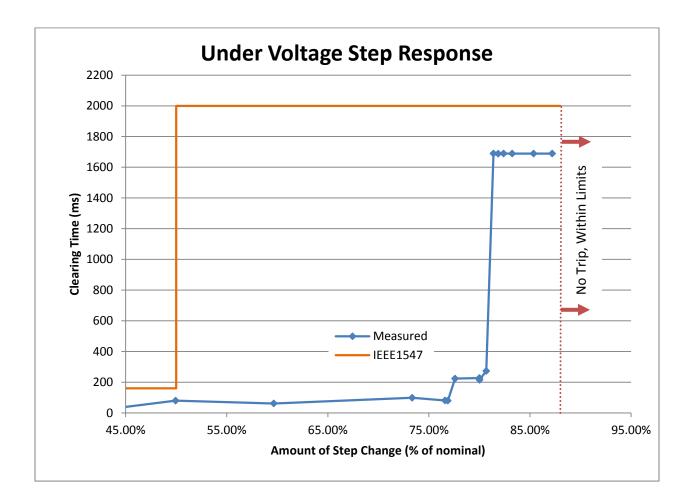

| Figure 4-4 Undervoltage Time Test Graph                       |    |

| Figure 4-5 Abnormal Frequency Magnitude Script Image          | 90 |

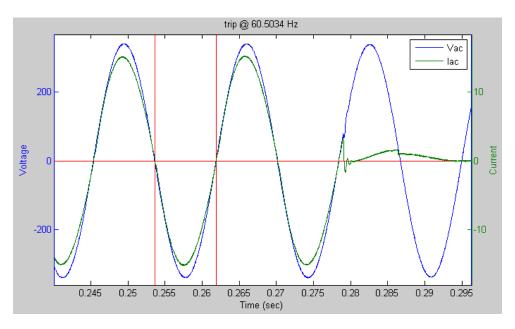

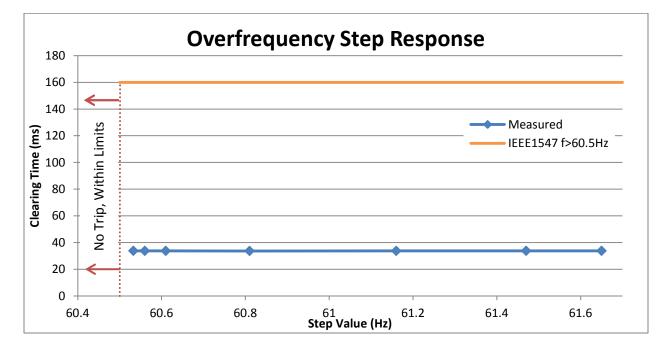

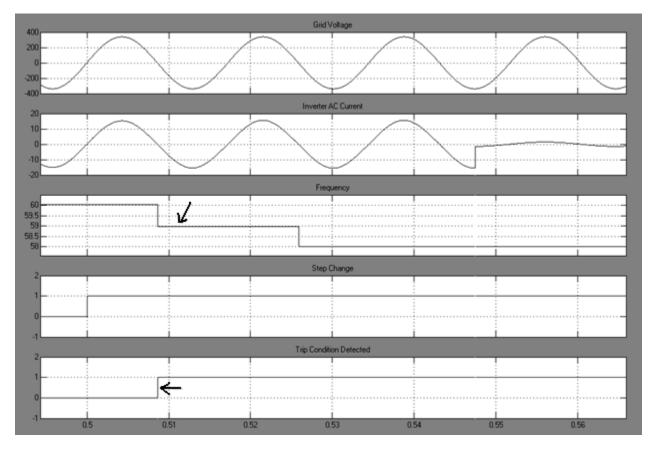

| Figure 4-6 Overfrequency Time Test Graph                      | 93 |

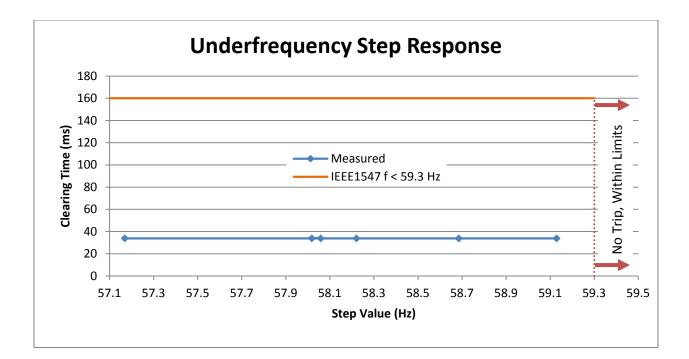

| Figure 4-7 Underfrequency Time Test Graph                     | 95 |

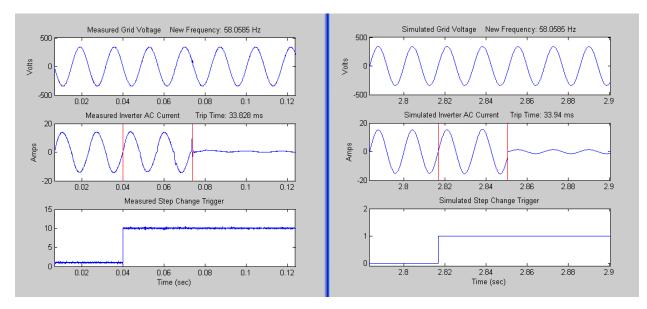

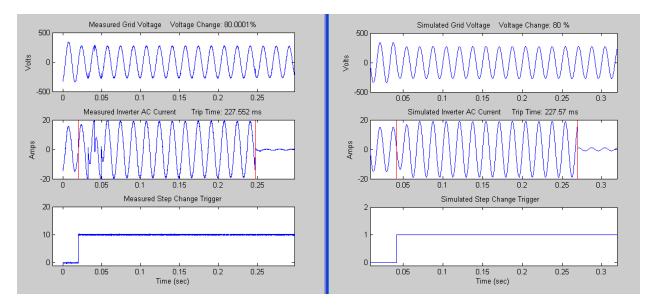

| Figure 5-1 Underfrequency Test Comparison                     |    |

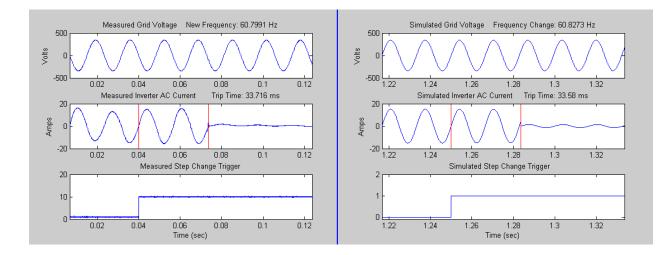

| Figure 5-2 Overfrequency Test Comparison                      |    |

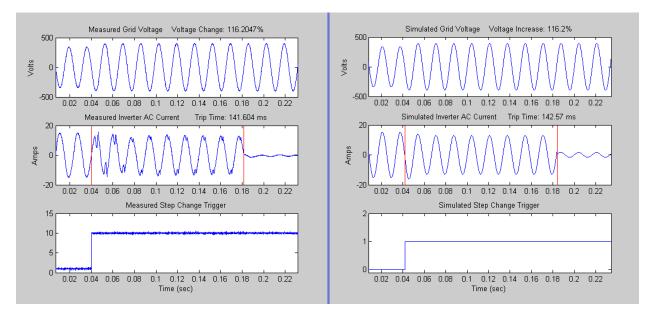

| Figure 5-3 Overvoltage Test Comparison                        |    |

| Figure 5-4 Undervoltage Test Comparison                       |    |

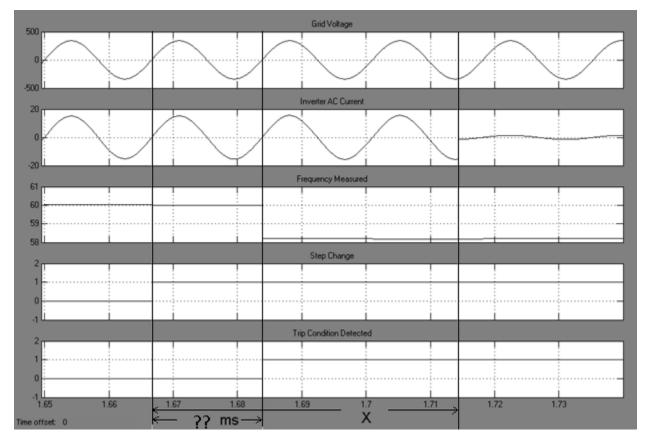

| Figure 5-5 Errant Frequency Measure Waveforms                 |    |

| Figure 5-6 Correct Frequency Measurement Waveforms            |    |

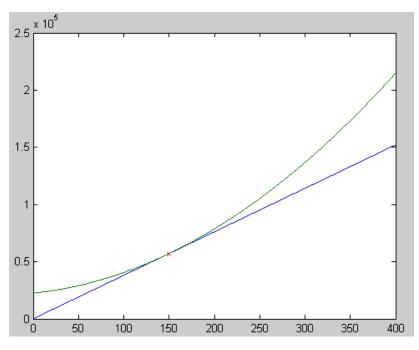

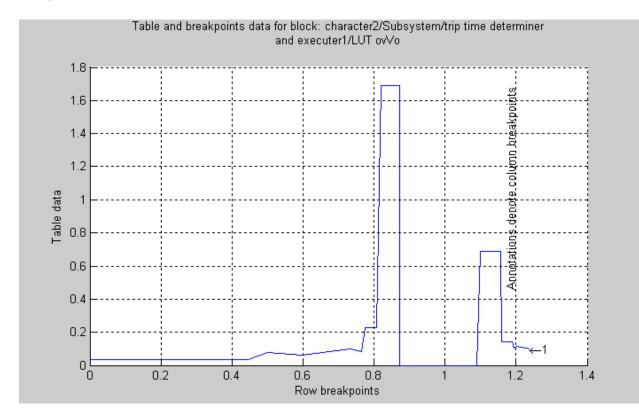

| Figure 5-7 Clearing Time Look-Up Table                        |    |

# List of Tables

| Table 2-1 IEEE 1547 Harmonic Limits                                    | 25 |

|------------------------------------------------------------------------|----|

| Table 3-1 Grid Simulator User Control Variables                        | 32 |

| Table 3-2 Typical Global Variable Values                               | 51 |

| Table 3-3 Titan 162kW Load Bank Specifications                         | 54 |

| Table 3-4 Load Bank Controller Serial Communication Parameters         | 57 |

| Table 3-5 Model Serial Communication Parameters                        | 57 |

| Table 3-6 RTDS Target Machine Specifications                           | 69 |

| Table 3-7 RTDS Patch Panel Connections                                 | 70 |

| Table 3-8 Fronius IG 3000 Specifications                               | 71 |

| Table 3-9 Fronius State Codes                                          | 71 |

| Table 3-10 PZ4000 Scope Channel Descriptions                           | 73 |

| Table 4-1 Reconnection Time Results                                    | 78 |

| Table 4-2 Overvoltage Magnitude Test Results                           | 81 |

| Table 4-3 Undervoltage Magnitude Test Results                          | 82 |

| Table 4-4 IEEE 1547 Clearing Time Requirements for Voltage Aberrations | 83 |

| Table 4-5 Overvoltage Time Test Results                                | 85 |

| Table 4-6 Undervoltage Time Test Results                               | 87 |

| Table 4-7 Overfrequency Magnitude Test Results                         | 91 |

| Table 4-8 Underfrequency Magnitude Test Results                        | 91 |

| Table 4-9 IEEE 1547 Clearing Times for Frequency Aberrations           | 92 |

| Table 4-10 Overfrequency Time Test Results                             | 93 |

| Table 4-11 Underfrequency Time Test Results                            | 94 |

| Table 4-12 Resonant Circuit Settings for Anti-Islanding                | 96 |

| Table 4-13 Anti-Islanding Test Results                                 | 96 |

### **1** Introduction

An area electric power system (EPS) has traditionally consisted of a primary generation source, such as a coal-fired power plant, a transmission and distribution system and a distributed load. Changes to this system have become more prevalent as distributed resources (DR), such as wind turbines, diesel generators, natural gas turbines and photovoltaics (PV) have become more available and affordable. In order to preserve the safety and reliability of the EPS, testing of grid-connected devices is essential. Standards, such as IEEE 1547 and UL 1741, have been developed to provide requirements for grid-connected DR systems. IEEE 1547.1 defines methods for testing devices to determine if they comply with the standards. These tests can be used to characterize a DR without any knowledge of the controller or hardware that causes the DR to function. Once the DR has been characterized, a software model can be constructed from the results and used in a multitude of environments to test issues related to grid integration. Many different methods can be used to perform these tests and characterize DRs, each having its benefits and drawbacks, but Hardware-In-the-Loop (HIL) provides a unique methodology that is extremely flexible and powerful.

This chapter will introduce issues associated with DR integration, relevant research that has been conducted, a brief overview of the system used for this thesis, the motivation for this project and a summary of what will be completed.

#### **1.1** The Changing Electric Power System

The electric grid was built in a way that strongly supports centralized generation. The high voltage lines that carry bulk power are focused around major generation centers. Regulation and financial incentives tend to benefit large-scale, consistent, dispatchable generation. These centralized generation sources use a narrow scope of fuels making them vulnerable to supply issues. A few of the

most prominent examples of fuel for electricity generation are coal, natural gas and nuclear. In 2010, coal accounted for 45% of electricity generation in the US. Natural Gas made up 23% and nuclear 20% for a total of at least 78% of electricity generation coming from centralized facilities [1]. The benefits of large-scale, reliable power plants are what has caused them to be such an attractive resource for so long. In the past, these fuels have been readily available and cheap, but wars in the Middle East and increased demand by quickly advancing nations, like China and India, are causing their supply to become stretched. Centralization reduces land permitting issues and eases operation and maintenance by having most of the machinery located in one place. Consistently available fuel yields a very controllable power source that can be increased or decreased on demand. These conditions have led to a successful EPS for most of the world for many years.

Environmental and security concerns are contributing to a change in the structure of EPS's. The Intergovernmental Panel on Climate Change, an international body of scientists, has been publishing reports since 1990 detailing the dangerous climactic impacts of burning large amounts of fossil fuels such as coal and natural gas. Also, procurement methods for coal, natural gas and nuclear fuel are well known environmental hazards. In addition to these environmental concerns, a number of securityrelated issues have become prominent. Unanticipated events, be they natural or unnatural, could have grave consequences for centralized generation sources because so many people rely on them. Of particular concern is the vulnerability of centralized generation sources to terrorists and mother nature. The recent earthquake in Japan demonstrated the vulnerability and repercussions of a failed nuclear power plant. In light of these issues, governments have begun to mandate increased usage of renewable energy resources through documents called Renewable Portfolio Standards in the US and Renewables Obligation in the UK. The goal of these policies is to mitigate many of the problems associated with centralized generation by increasing the amount of generation from renewable resources. These documents require a certain percentage of generation to come from renewable

resources such as solar, wind or geothermal. These resources, in addition to other generation and storage sources, are commonly labeled DRs because they are not part of a centralized power generation center. DRs are defined by IEEE 1547 as generation sources, such as synchronous machines, induction machines, or power inverters/converters with a power rating less than 10 MVA. Implementation of these DRs is contributing to a change in grid infrastructure and operation.

DRs are not meant to immediately replace centralized generation sources, but rather to gradually augment the system. They can have many benefits to the grid financially and technically. One example is load shaving. When the sun is shining during the day the temperatures are high and thus air-conditioner use is prevalent. The energy that the sun provides to heat the earth can also be captured to generate electricity, using Photovoltaics or Concentrated Solar Thermal Power (CSTP), and offset part of the high electricity demand used to cool buildings. This reduces the amount of costly ancillary services that are necessary to meet the load. Also, if the electricity produced by PV or CSTP from the sun was not being consumed, it may be stored and used at other times or as a backup resource during outages. Another example is easing augmentation of the grid. In a centralized generation scenario, if a new load center is built, transmission lines that have the capacity to support the demand of the new load center must be built. This can be a costly procedure that is complicated by land rights issues. DRs solve this by being easily geographically distributed. The energy can be generated on site, thus reducing the need for large transmission lines. This aspect, in addition to diversified fuel resources and modularity of generation systems, creates flexibility in power distribution and grid infrastructure.

Unfortunately, introduction of DRs to the grid can have unwanted effects that may jeopardize the reliability and quality of electricity on the grid. One area of distributed generation (DG) that is receiving a lot of attention is renewable. Recent political activity and public interest has caused an increase in the amount of renewable resources attached to the grid. The variability and

nondispatchable nature of these resources is a major concern to utility engineers. If the sun goes behind a cloud or the wind ceases to blow, generation will drop and if back up sources cannot react quickly enough grid instability could result and possibly causing the grid to fail. Many studies have been performed to identify and analyze the effects of DRs on the grid. One extensive report describes common grid problems such as, voltage fluctuations, voltage rise, reverse power flow, power fluctuation, impacts on power factor, frequency regulation, harmonics, unintentional islanding, fault currents and grounding issues and how they are associated with the interconnection of DRs [2]. This report also goes on to describe how DRs can be best implemented in the current grid structure with respect to said issues, though it states that much more research is needed. The National Renewable Energy Laboratory (NREL) commissioned a more technical report to analyze the impacts of high penetration of PV on the grid [3]. A wide range of relevant issues were studied including PV system design, effects on transmission, and distribution system voltage performance. Many gaps in the research are also identified. Other studies more focused on PV system design were also conducted. [4] examined the controls and storage necessary for optimization of PV systems. The common conclusion to all of these studies is that more research needs to be conducted to further determine the effects of higher penetrations of DRs. Each report specifically identifies inverters as a source of many unknowns. They state that more modeling tools to simulate these issues and determine their effects are required if high penetration of DRs is to be accomplished. Also, the amount of variability in an EPS with DRs is great. Since DRs can be installed at different points in the EPS, known as points of common coupling (PCC), an incredible number of variations in system configuration are possible. A model of one local EPS may not sufficiently model another. Testing must take place to prevent failures and identify issues introduced by DRs. A flexible testing and modeling system is needed to determine the effects of DRs on the grid.

Microgrids are another area where extensive modeling is required. A microgrid is a group of generation sources and loads that has the ability to disconnect from the EPS. The ability is referred to as islanding. Once the microgrid disconnects and becomes an island, the dynamics of power flow, power quality and control can change. Test beds have been constructed that model microgrids [5], [6]. It is clear that testing the variable configuration of microgrids is an issue that must be addressed by a flexible and powerful simulation system.

In an attempt to maintain quality and safety on the grid, IEEE and UL have both introduced standards, IEEE 1547 and UL 1741 that define regulations for grid-connected devices. These standards mandate that DRs must cease to energize the grid if various conditions such as abnormal voltages, abnormal frequencies or islanding conditions occur. DRs are not allowed to provide any type of voltage regulation [7]. This is a very important point as it requires DRs to act as current sources. The DRs are in effect, slaves to the voltage and frequency of the larger EPS. If a condition were to occur where the DRs were required to cease to energize the grid, a large drop in power could result and cause a cascading failure in other areas as described in [8]. These issues become more important as DRs become more wide spread. On the other hand, [3] suggest that if DRs were not required to disconnect whenever the grid experienced troubles they could provide support and possibly prevent outages. Before any new scheme can be implemented, though rigorous testing must take place to ensure that it will be safe, stable and reliable.

#### 1.2 Relevant Research

Various grid integration testing has been conducted on PV systems. The authors in [**9**] modeled and simulated a grid-connected PV inverter using IsSPICE with the purpose of studying strategies for reducing total harmonic distortion (THD) and increasing power factor. An AC power supply was used to simulate the grid. Two different grid voltage models were used to control the power supply, one based

on an ideal sine wave and the other based on sampling of the actual utility grid. THD was measured for various power outputs of the inverter.

A model of an inverter using key performance parameters was developed by researchers at Sandia National Laboratories [10]. These parameters, mainly consisting of power and voltage ratings, were determined both from manufacturer's specifications and lab and field testing. The model that resulted was intended to be used for systems analyses and determining degradation of field inverters in real-time.

Since actual utility grids can rarely be used for testing, grid simulators are a key component to testing grid-connected PV inverters. In [**11**] the authors designed, in PSCAD, and constructed a grid simulator to produce waveforms to test grid-connected renewable energy systems. It provides an indirect connection to the utility grid so that DR can be connected safely. It was shown that abnormal grid conditions, balanced transient grid conditions, and unbalanced transient grid conditions could all be simulated using the grid simulator constructed.

A detailed model of inverters for studying transient issues related to grid integration was developed in [12]. Functionalities such as PWM switching, a current controller, a power controller and anti-islanding detection were all modeled in PSCAD/EMTDC. Also modeled were the grid, grid interface and PV array. Maximum power point tracking (MPPT), anti-islanding, current harmonics and fault conditions of the model were all analyzed.

In [13], a protection device for a grid-connected, transformerless PV inverter was tested. A realtime data system (RTDS) was used to simulate the output of a PV array and the utility grid, though how this was done was not discussed. MPPT, anti-islanding and voltage degradation capabilities of the protection device were all tested with a real inverter.

An RTDS was also used to study the effects of PV integration into a relatively small grid on the island of Lanai in [14]. The 5.5 MW grid was modeled in Simulink and stability and power flow control tests were performed for various control schemes and weather conditions.

#### **1.3 Motivation**

Each of these projects seeks to serve the need for modeling or testing integration of PV onto the utility grid. Most provide detailed modeling of switching control or power control. These control schemes are rarely available to users not affiliated with the developers. There needs to be a way to model these inverters interaction with the grid without the need to obtain detailed models of the inverters so that grid integration studies can be performed and PV can be integrated safely.

DRs can have a wide range of characteristics and thus integration with the larger EPS is rife with complex issues. To mitigate these issues, a separate simulated system can be built to test the effects of connecting new devices. These simulated systems function the same way as the actual system so results from the testing system may be reliably applied to the original system. At the power levels necessary to achieve this, cost of the components, space required to build a simulated system and the time it would take to ensure a safe and reliable system are three main prohibitive factors. Also, integrating the components in a way that mimics an actual EPS could create significant problems. The actual hardware could be used to obtain exact results. But if this approach were to be taken, the system would most likely be inflexible and limited in the scope of variations in testing. In contrast, a Hardware in-the-Loop (HIL) system provides an easily configurable and very flexible way to simulate and test an EPS that correlates well with actual utility systems. Rather than use the actual components, power amplifiers and load banks that can be easily controlled through HIL can be used to simulate them. With the correct set-up other equipment can be seamlessly integrated as if the HIL system were an actual EPS. In addition to a flexible hardware configuration, HIL makes simulating the components of the EPS easily

achievable by using common programming languages and centralized command. This reduces costs, space and time requirements.

#### 1.4 HIL Overview

An HIL system generally consists of three main parts: the device being tested, the system being simulated and the interface between the two. An RTDS acts as the brain of the whole system. The simulation occurs in the RTDS which then outputs the simulated data or set points to the actual hardware. Power flow and feedback are two examples of parameters that can be controlled by the RTDS. HIL can be divided into two categories, Controller Hardware in the Loop (CHIL) and Power Hardware in the Loop (PHIL). CHIL systems generally simulate devices such as power electronics while keeping the controller hardware physically present in the loop. An example of which can be seen in [15]. PHIL systems differ from other HIL systems because the components require large amounts of power, generally in the kW range, which necessitates amplifiers and other interfacing devices capable of handling high voltage and current. An example of PHIL testing can be seen in [16]. Many different systems have been tested using HIL. Wind turbine controllers were tested in [15]. The HIL system allowed for these controllers to be tested with an actual wind turbine present. In [17] an HIL system was used to simulate dynamics in a DC zonal distribution system. Issues with scaling HIL systems up to high power are explored, as well as producing accurate time-domain software models of actual components. Another test using HIL was performed by a research team in France to determine the effects of distributed energy storage sources, such as ultra capacitors, on the power system of the small island of Guadeloupe [18]. Power electronics testing has also been performed using HIL in [13]. Finally, a study was conducted on the measurement accuracy of HIL [19].

The scope of a PHIL system is limited by the capabilities of individual components. Scaling systems up to larger power levels has been a topic of research since 1994 when one of the first PHIL

systems was developed by Mitsubishi and Tokyo Electric Power engineers. In [20], they describe the digital to analog interface between the power amplifiers and real-time digital simulator.

The large devices used to recreate an EPS for testing must be controlled in such a way that they act like the actual system. Programmable controllers with advanced user interfaces for system components such as a load bank or power amplifier have existed for a while. Unfortunately most contain their own proprietary software and are limited to controlling a specific piece of equipment. HIL eases the control of multiple devices by allowing the user to integrate all of these controllers into one program, using one software language, and one machine. The developer does not need to learn new programming languages or adapt to new interfaces with each new device. Control is centralized and comingled. Simple analog or digital input and output ports can be configured once and reused for multiple applications. Extensive libraries can be constructed and referenced easily by users with different skill levels and different application goals. These features make HIL a very attractive and approachable system for a wide range of users.

When the major components of an EPS have been successfully implemented in a simulated system, it is often desirable to introduce other elements. Power electronics, more specifically inverters, are of particular interest to many utility engineers due to the rapid increase of renewable resources. Conventional testing of renewable resources requires the presence a PV panel or wind turbine and sunshine or wind. The intermittent availability of solar irradiance or kinetic wind energy can greatly hinder testing. It also is very difficult to get repeatable scenarios. In HIL these systems can be characterized and modeled through software. Outputs from the software using a D/A channel can then be used to control an amplifier which will mimic the previously uncontrollable element. Many scenarios can then be simulated and repeated on command which will contribute to a flexible and powerful testing system. It is no longer necessary for PV or wind energy systems to be physically present or if

they are, for the weather to be in a desired state for testing to occur. This reduces infrastructure and reduces time required for testing, both of which save money.

Also, power electronics technology is constantly evolving at a rapid pace. New control algorithms and discrete components emerge constantly and must be tested before being implemented in an EPS. The inflexibility of utility scale test beds can be a great hindrance when it comes to frequent and somewhat unpredictable testing. With each new development in devices, the set-up may have to be modified, costing time and money. HIL provides a way to reduce these costs by using a software model developed for the power electronics. The model can be easily modified without making any costly hardware changes. The same applies for any generation source, etc. that can be modeled in software.

Device characterization and then modeling can be a tedious process that requires a lot of the person performing the characterization's time. For example, when characterizing a grid-connected inverter, there is a wait time before the inverter will make an electrical connection with the grid and begin to export power. This time can be on the order of five minutes for grid-tied PV inverters [21]. Each time a condition is created by the user that causes the inverter to trip offline, five more minutes must elapse before another test can be performed. This is valuable time that the engineer performing the tests could be using for other important tasks. HIL systems, through the use of scripting software, can fully automate tests. Feedback loops can be used to inform the software when to perform a new test or if the test needs to be repeated. A device can be characterized in a reduced amount of time because the machine will know exactly when to perform the tests. Also, minimal monitoring or interference is needed. Automation of the characterization process greatly reduces the amount of time and effort required.

In summation grid-interconnection characteristics must be tested to ensure safe and reliable operation of an EPS. Conventional testing systems can be bulky, costly and inflexible. HIL solves many

of these issues by creating a system where testing can be easily and efficiently performed. Characterization of hardware, and the software models that result, can greatly reduces cost in time, infrastructure, space and money. The impacts of these tests can lead to more robust and reliable systems. HIL provides an easy and flexible way to perform characterization. In addition to these benefits, HIL is also attractive because it has a wide range of applications, it is very versatile and it is easy to learn and develop powerful skills.

#### **1.5** Statement of Work

This thesis documents the hardware configuration, software coding, testing performed and characterization and modeling of a grid-connected PV inverter using PHIL. It begins with information on PV systems and the IEEE 1547 interconnection standard in Chapter 2. It then describes the HIL set up and how the various components were simulated in the first part of Chapter 3. Chapter 4 details the testing procedures and shows results from characterization tests. The PV inverter characterization data is used to create a model of the system in Chapter 5. The model is validated against the results from the characterization tests in the later part of Chapter 5. Finally, conclusions and recommendations are made in Chapter 6. Additional information, such as software code and an index of abbreviations, is available in the appendix. The information from this thesis can be used to obtain valuable grid-integration information that could be of great use to utility, power electronics and system design engineers.

### 2 Photovoltaic Systems and IEEE Standard 1547

PV systems have recently been installed in large numbers. The interface between a PV system and the EPS is typically an inverter with certain controls that facilitate power flow between the PV panels and the EPS. Due to the high penetration of PV systems, a PV inverter will be characterized for grid integration studies.

There are many different issues that could be studied with PV inverters. The scope of the characterization and modeling performed in this thesis will be limited to a few of the main issues discussed in IEEE 1547 Std. This document has become the industry standard for requirements for grid-tied DR and thus most grid-tied DR have some sort of protection that meets these standards.

This chapter provides background on PV systems and IEEE 1547. Integration issues, system configurations and requirements will be explored.

#### 2.1 PV Systems

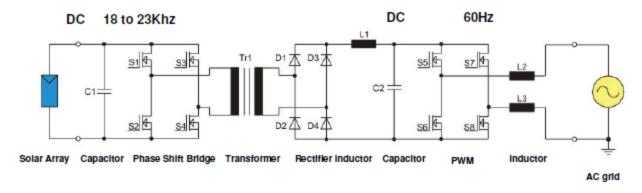

PV panels convert radiation from the sun into electricity using semiconductors. They can be arranged in strings to obtain different voltage levels. These strings are then arranged in parallel to form an array. The electricity they produce is in the form of DC. The PV output DC current must be shaped into an AC waveform by a PV inverter. Its voltage, frequency and phase angle must be synchronized with the 60 Hz waveform of the grid and the total demand distortion must be kept less than 5% [22]. A typical configuration for realizing a grid-tied PV inverter system is to use a DC/DC power converter to step-up the voltage from a PV array and provide maximum power point tracking (MPPT). This higher DC voltage is then shaped into an AC waveform using an inverter. The output is filtered and synchronized with the grid in the final stage before being connected. There have been systems developed that accomplish all of these functions in a single stage [23].

#### 2.1.1 Inverters

Inverters are electrical devices that convert direct current (DC) to alternating current (AC). They have a wide range of applications including, variable speed drives, power factor correction and grid-tied distributed resources. They also come in various configurations, such as single-level or multi-level, voltage source or current source, each yielding different features [24], [23]. One common application of inverters is with PV systems. The recent increase in penetration of PV generation on the EPS has driven higher levels of research and development of single-level grid-tied inverters [25].

#### 2.1.1.1 Hardware

Inverters come in a wide variety of topologies, each having its own weaknesses and strengths. There are three high level categories for inverter topologies: central, string and module integrated inverters [**26**]. Central inverters are the most basic. The PV system consist of an array of PV panels that all feed through one centralized inverter to the grid. While the simplicity of this topology has its benefits, it also has a number of disadvantages. The entire system hinges on one inverter. If there is a problem with the inverter, the system goes offline until the inverter can be repaired. Another drawback is the lack of effective MPPT. Each PV panel could be shaded differently, but the centralized MPPT only functions for the whole array. Also, the lack of any localized inverter requires expensive DC cables to transport power between panels [**27**].

String inverters solve some of the problems associated with centralized inverters; while at the same time, utilize their cost reducing configuration. This topology is realized by placing an inverter on each set of series connected PV panels. This allows for the inverter control to be tailored to each string, rather than the whole array. Though this is still a subject of research [**28**], it is generally accepted that shading effects are reduced and more power can be extracted from the array. String inverters also reduce the amount of DC wiring needed compared to centralized inverters since the DC to AC conversion takes place at each string. These topologies typically do not need transformers [**27**]. Since

the PV panels are placed in series, various voltage levels can be achieved. Multi-string configurations present another alternative [27]. This topology involves placing DC-DC converters on each string, then feeding multiple strings into one inverter, thus allowing for localized MPPT and reducing the number of inverters needed.

Module integrated inverters, also called microinverters are intended to be used with individual PV panels instead of the whole system or a string of panels. This allows for more specific control schemes, smaller components and higher flexibility with PV array configuration. MPPT can be unique to a single panel, providing greater power extraction. The lower power level at which they operate allows for smaller components to be used. One of the most recent developments in module integrated inverters is to incorporate all of the components needed into one board that can be installed on the back of a PV panel. For example, [**29**] presented a 3 mm tall, 95% efficient microinverter to interface building integrated PV to the 120 V<sub>ac</sub> single phase utility grid. As can be seen from this example, module integrated inverters operate at lower powers, but still yield high efficiencies.

Various types of transformers can be used in each of these topologies. Line frequency transformers are an older technology. They are used to step the output of the inverter up to utility scale voltages. Operating at line frequency, these transformers must be extremely bulky in order to prevent saturation. Also, line frequency transformers are known to operate with low power quality, which was a major factor in driving new topologies in inverters [**27**].

Another, more recent, design is to implement a multi-stage inverter that uses a DC-DC converter with a high frequency transformer. Multi-stage designs use DC-DC converters to boost PV panel voltages to utility voltages. This is especially useful in module integrated inverters that operate at lower voltages because it eliminates the need for larger line frequency transformers. The DC-DC stage can also be used for current shaping, as discussed in [**30**].

These converters can also be realized without a transformer. This is particularly attractive in string and multi-string inverters that already supply the necessary voltage to be put on the EPS. An unfortunate downside to transformerless topologies is that the design does not meet safety standards in some countries [**26**]. In the US, the NEC section 690 was recently updated to allow for ungrounded PV systems. This allows transformerless converters to be used, with a few protection requirements such as disconnects, overcurrent protection and ground-fault protection.

The grid-tied PV inverter, along with other devices, plays a crucial role in synchronization, protection, power quality and efficiency. Various interconnection issues must be addressed to protect the larger EPS from being affected by these inverters. IEEE 1547 outlines these issues and provides requirements for interconnection of distributed resources [22]. Number of stages, grid interconnection, and transformer type are considerations that allow for a multitude of inverter topologies. Many single phase inverter topologies can be found in [23], [27] and [26]. Converters are summarized in [27] and the most effective are identified for different situations. It recommends high frequency transformers for almost all topologies. Multi-stage configurations are recommended for inverters that need to increase the voltage output of PV panels or strings such as module integrated or string inverters.

#### 2.1.1.2 Connection to EPS

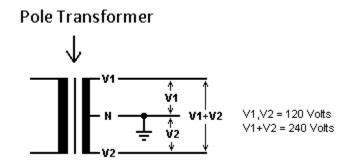

Another issue that must be taken into consideration when designing a grid-tied PV system is how the inverter will connect to the grid. The type of connection dictates what kind of inverter can be used. Typical inverter configurations are single-phase and 3-phase. Single phase inverters are used for low power and residential applications. Homes are typically fed by a pole transformer that utilizes a split-phase configuration. Pole transformers are fed with a single phase of the 3-phase distribution system. Split-phase operation involves connecting three wires to the single phase transformer. Two wires are connected across the secondary and a third is connected to a center-tap on the winding. The waveforms V1 and V2 are 120 V<sub>rms</sub> and 180° out of phase. Therefore, when they are summed 240 V<sub>rms</sub>

results. This higher voltage reduces the current rating and thus the size of the wires necessary. A diagram of this concept can be seen in Figure 2-1.

Figure 2-1 Residential Split-Phase Configuration

Larger installations, like solar farms, generate larger amounts of power. Also, they may have access to a 3-phase connection and thus can utilize a 3-phase inverter configuration. 3-phase inverters can be composed of three single phase inverters to handle larger amounts of power.

#### 2.1.1.3 Controller

Grid-tied inverters also must have special control systems that constantly monitor grid conditions. IEEE 1547 explicitly states that inverters are not permitted to provide voltage regulation. If the EPS fails and an islanding condition occurs, the inverter must detect the failure and disconnect from the EPS. They accomplish this through an anti-islanding controller. These controllers may be either passive or active. Passive protection involves monitoring grid conditions while active protection involves injecting errors and measuring the response [**31**]. In the case of a microgrid, islanding inverters may be implemented. These inverters do not employ anti-islanding controls and will continue to provide power to the microgrid if the EPS fails.

A complete EPS failure is not the only reason a PV inverter must disconnect. Abnormal operation conditions can indicate problems. Limits on the amount of variation in operating conditions are defined by IEEE 1547. The inverter controllers must be able to detect, to a certain degree of

accuracy, parameters such as voltage and frequency and determine when to trip. In certain scenarios, where the voltage doesn't deviate a great deal, the inverter is allow to continue normal operation for a longer period of time. This function is called ride-through. The assumption is that this aberration is minor and likely temporary and therefore not sufficient enough to necessitate a disconnection.

## 2.2 IEEE 1547 Standard for Interconnecting Distributed Resources with Electric Power Systems

The recent interest in incorporating an increasing amount of DR such as, wind turbines, solar PV, natural gas generators, power electronics and batteries into the electric power grid has necessitated standards to ensure safety and power quality are maintained. IEEE published a family of these standards beginning in 2003 with the intention of consolidating the various standards and testing requirements for DR. The highest level standard is IEEE 1547-2003 The Standard for Interconnecting Distributed Resources with Electric Power Systems. It is accompanied by IEEE 1547.1 Standard Conformance Test Procedures for Equipment Interconnecting Distributed Resources with Electric Power Systems, IEEE 1547.2 Draft Application Guide for IEEE Std 1547-2003, IEEE 1547.3 Draft Guide for Monitoring, Information Exchange, and Control of Distributed Resources Interconnected with Electric Power Systems and IEEE 1547.4 Guide for Design, Operation and Integration of Distributed Resource Island Systems with Electric Power Systems. The requirements defined by IEEE 1547 and testing defined by IEEE 1547.1 are relevant to this thesis and thus will be discussed in further detail.

The requirements of IEEE 1547, found in chapter 4 of the document, are divided into four sections, General Requirements such as Voltage Regulation, Synchronization and Isolation, Response to Abnormal Conditions, Power Quality and Islanding. The tests used to determine the level of compliance with the standard are listed in chapter 5. They are the Design tests, Production tests, Interconnection Installation Evaluation, Commissioning tests and Periodic Interconnection tests. The Design, or Type, tests are intended to be performed on a representative unit in the lab or field. Production tests are not

meant to test IEEE Std 1547 requirements, but rather to verify the manufacturer's ratings. Interconnection Installation Evaluations are meant to verify that system designs meet IEEE Std 1547 requirements for grounding, fault detection, monitoring, reclosure functionality and isolation. Commissioning tests are to be performed before the initial connection is made or when any software or hardware changes are made to the system. They include testing the isolation device, the unintentionalislanding capabilities and cease to energize functionality. Finally, the group with authority over the DR is required to define Periodic Interconnection tests.

The requirements and tests defined above must be met at the connection point with the local EPS. Devices connected at this point could include the DR, local load, and the area EPS. This interconnection is more commonly known as the point of common coupling. IEEE 1547 assumes the EPS operates at 60 Hz and the DR is a synchronous machine, induction machine or static power inverter/converter less than 10 MVA.

#### 2.2.1 Temperature Tests

Temperature stability is the first test listed in the Design category. There are two purposes of this test. The first is to confirm that the equipment under test (EUT) operates to a reasonable degree of accuracy within the manufacturer's specified temperature range. The second is to confirm that the EUT can still function properly after being stored in an environment where the temperatures remain in the manufacturer's specified range. Proper functionality during fluctuating temperatures is essential to DR because, by their nature, they will be operated in diverse environments.

#### 2.2.2 Abnormal Voltage Tests

The next test assesses the EUT's response to abnormal voltage conditions. Overvoltage and undervoltage are deviations from nominal operating conditions that may occur on an area EPS. The EUT must be able to detect a certain amount of voltage deviation and it must respond in a reasonable

amount of time. In order to test for the response to voltage deviation, the magnitude of the EPS's voltage is slowly ramped at the terminals of the EUT. The rate of this ramp, m, is specified in Appendix A of IEEE 1547.1. The equation is shown below,

$$m = \frac{(0.5) * a}{2 * z}$$

Equation 2-1

where,

a is manufacturer's stated accuracy,

z is manufacturer's stated clearing time.

The magnitude at which the EUT trips is recorded and compared with the manufacturer's stated trip value.

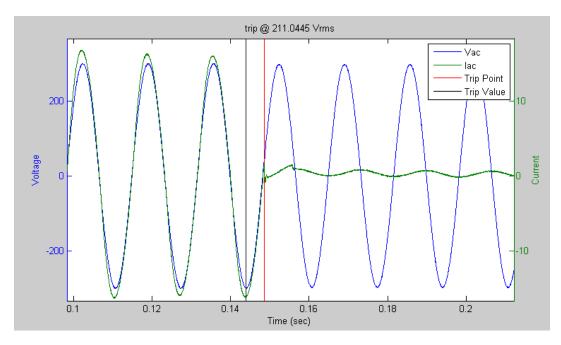

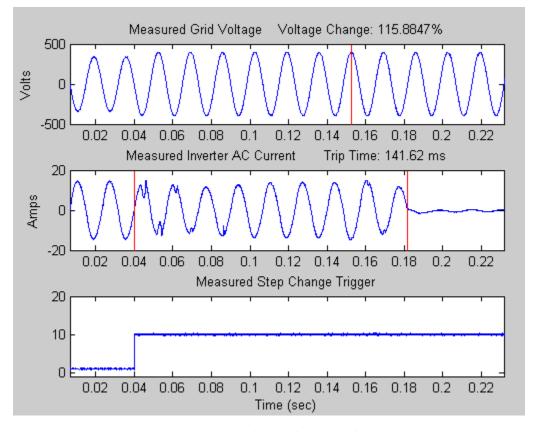

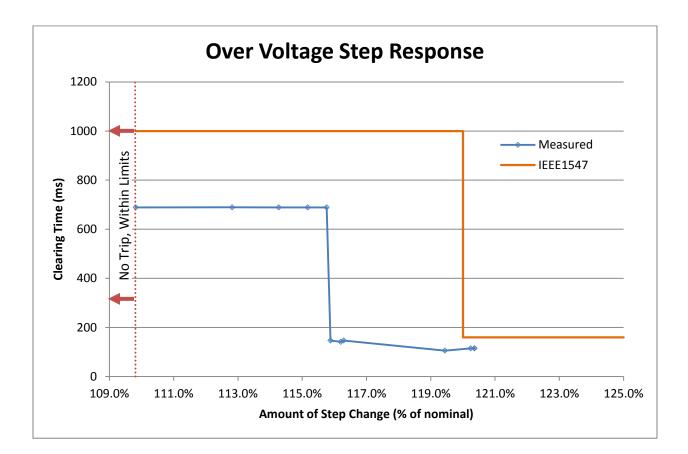

The time response is tested by applying a stepped signal to the EUT and recording the duration of time between the step and EUT trip point. The clearing time must be between 0.16 – 2 seconds, depending on the voltage variation as a fraction of the base voltage. If multiphase units are to be tested, each phase must be tested individually. It is important when performing this test that only the voltage is modified to ensure that the DR does not trip for any other reason.

#### 2.2.3 Abnormal Frequency Tests

Abnormal frequency conditions must also be tested. As in the abnormal voltage test, it is required that the EUT cease energizing the EPS if overfrequency or underfrequency conditions are detected. The magnitude response is tested by varying the frequency of the EPS waveform in one direction at a rate defined in equation 2.1, then recording the frequency at which the EUT trips.

The time response is tested by applying a step change in frequency and recording the time it takes for the EUT to trip. If multiphase units are to be tested, each phase must be tested individually. It

is important when performing this test that only the frequency is modified to ensure that the DR does not trip for any other reason.

The DR must detect these conditions and discontinue energizing the EPS, because the EPS is well regulated and if these conditions occur, it is likely that there is a serious problem, such as a fault. If the DR continues to supply power, dangerous conditions could become present that system operators or repairmen may not be aware of.

#### 2.2.4 Synchronization

Synchronization is the next major test required. This test separates DR into two categories, devices that can generate voltage without using the grid, such as stand-alone inverters, and devices that must use the grid, such as induction machines. Each category of devices requires a specific form of testing. For independently excited equipment, it is required that the voltage, frequency and phase angle are synchronized with the EPS voltage, frequency and phase angle before a connection is made. Three different methods are specified for testing these conditions because different equipment synchronizes differently. A multifunction device that has the option of using a synchronizing function and controls when a connection is made can be tested with a simulated grid using method one. Synchronous generators are tested using method two. An actual grid interconnection is made and the paralleling device is monitored along with the generator and EPS voltage, frequency and phase angle. Devices that synchronize automatically, and cannot be disabled are tested using the third method.

In the second category, grid excited equipment, the concern lies with the magnitude of startup current. It must not create too much of a voltage fluctuation in the EPS when the device begins to energize the grid. The EUT is fed with a power source and startup currents are monitored to ensure they are within range. The EPS operates at a certain voltage, frequency and phase angle. In order to maintain power quality, interconnected devices must conform to this voltage magnitude, frequency and phase angle. Depending on the power rating of the DR, frequency must be within 0.1-0.3 Hz, voltage

within 3-10% and phase angle within 10-20° of the EPS. Deviations in any of these elements could damage equipment on the grid or on the DR.

#### 2.2.5 Interconnection Integrity

The Interconnection Integrity test validates that the EUT conforms to standards in three areas, electromagnetic interference (EMI) protection, surge withstand performance and dielectric test. EMI is common in all electrical systems. It can interfere with the operation of equipment and potentially cause it to malfunction. Tests and standards for EMI performance are defined in IEEE Std C37.90.2. Surge withstand performance is another common feature that grid connected equipment must have. Surges can be unpredictable, such as those caused by lightning and can lead to very dangerous situations resulting from high currents. Control circuitry is tested using IEEE Std C37.90.1. Power circuitry is tested using IEEE Std C62.41.2 and IEEE Std C62.45. The dielectric test is defined for equipment that operates below 1000 V. It investigates performance at 1000 V<sub>rms</sub> plus 220% of the rms nominal voltage. A 500 VA transform is used to apply the voltage for 60 seconds. The standard states that no flashover or damage can occurring during the test.

#### 2.2.6 DC Injection

The next test regards the amount of DC injection allowed for non-isolated inverters. The EPS is designed for AC operation. It is important to limit DC current in the EPS because certain components, such as transformers or meters, can become damaged by excessive DC currents. The test specified for this standard requires measuring the DC current (< 1 Hz) of the EUT while the EUT operates under nominal conditions. The averaging window of the measurement must be no shorter than one line cycle and no longer than sixty line cycles. The average DC current over a five minute period must be less than 0.5% of the rated output current.

#### 2.2.7 Unintentional Islanding

One of the most important tests defined in IEEE 1547 is the Unintentional Islanding test. Islanding is a condition that occurs when a local EPS operates independently of the area EPS. The local EPS regulates its own frequency and voltage in an islanded state and does not interact with the area EPS at all. While islanding can have many benefits such as security, improving power quality and reducing load of the area EPS, it can lead to dangerous conditions if the proper protection is not utilized. Since DRs are, by definition, distributed, no centralized control exists and therefore if the area EPS is deenergized, it is still possible that a local circuit could be energized by a DR. For example, if the area EPS suffers from a problem, it may be shut down so that it is safe for a technician to work on equipment. But if a solar panel and inverter connected to the area EPS continue to export power to the area EPS after it has gone down, the technician could be exposed to unexpected, dangerous conditions. Some DRs are specifically designed to operate in an islanded configuration, while others are not. The nonislanding DRs must therefore be tested to ensure that they disconnect from an EPS if an island is formed.

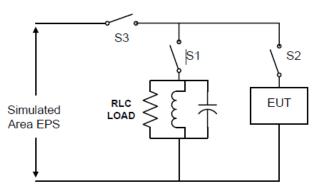

A simple test circuit is proposed in IEEE 1547.1 in which the EUT and an RLC load for a local EPS. They are then connected in parallel with a simulated area EPS. A switch (S3), inserted between the simulated area EPS and the local EPS, is used to simulate an islanding configuration by disconnecting the simulated EPS from the local EPS.

Since the local load could vary widely, the worst case condition must be tested. The load components must be chosen such that the resonant frequency of the RLC load is as close to the nominal operating frequency as possible. This will force the EUT to differentiate between a resonant circuit that mimics the EPS and the actual EPS. Constraints for the load are given in section 5.7.1.2 of IEEE 1547.1. They state that the quality factor of the load, calculated as

$$Q_f = \frac{\sqrt{P_{qC} * P_{qL}}}{P}$$

Equation 2-2

where,

$P_{qC}$  is per phase inductive reactive power,

$P_{qL}$  is per phase capacitive reactive power,

*P* is per phase real power.

must be equal to 1 + - 0.05.

To perform the test, all switches are closed, the area EPS is simulated and the EUT is allowed to energized the circuit. Once this point is reached, S3 is opened and the time it takes for the EUT to deenergize must be less than two seconds. A diagram of this circuit taken from IEEE 1547 is shown in Figure 2-2. A similar test is defined for synchronous machines, but S1 and S2 are replaced with direct connections.

Figure 2-2 Anti-Islanding Test Circuit

#### 2.2.8 Reverse Power

The reverse power technique requires that the EUT detect a change in the direction of power flow once it is disconnected from the EPS. This protection is tested by gradually changing the phase angle of the current powering the EUT until 180° is reached. The current is then ramped until the EUT

trips. A similar test, using a step instead of a ramp, can be performed to determine the amount of time it takes the EUT to trip.

#### 2.2.9 Open Phase Test

Another test requiring the EUT to de-energize is the Open Phase test. If a device is operating on a three phase system and one phase is opened, it is necessary for the EUT to cease to energize the EPS on all phases. Unbalanced operation on a three phase system leads to harmonics and a reduction of power quality.

#### 2.2.10 Reconnection

A majority of these tests have described the conditions that require the EUT to disconnect from the grid. Section 5.10 details the conditions required for the EUT to reconnect to the EPS. In this test, the EUT is allowed to operate under nominal conditions. A step change in the voltage is then applied to cause the EUT to trip and de-energize. The voltage is then returned to within the normal limits and the time it takes for the EUT to reconnect is measured. The voltage and frequency must both be within limits for the EUT to reconnect. To ensure that there is no malfunction with the reconnect circuitry once it is installed permanently, another test is required. As before, a parameter such as voltage is changed to a value outside of acceptable limits. Then, while the EUT is counting down to reconnection, the voltage is stepped outside of the limits. The device's reconnect timer should reset and start counting again. The reconnecting timer is critical because it allows for possible temporary excursions in voltage or frequency to be cleared before the device reconnects and begins energizing the grid again.

#### 2.2.11 Harmonics

Waveform harmonics are phenomena that lead to reduced power quality due to increased distortion. These conditions lead to reduced efficiency and can damage equipment. Section 5.11 describes the tests used to determine the amount of both individual current harmonics and total rated-

current distortion for a DR. Multiple methods for testing are needed for different DR. While different tests set-ups are required, the requirements remain the same. The magnitude of the first 40 harmonics is to be measured. Acceptable values are listed in IEEE Std 1547 Section 4.3. The values are reproduced in Table 2-1 below.

| Individual<br>harmonic order h<br>(odd harmonics) <sup>a</sup> | h < 11 | 11 ≤ h < 17 | 17 ≤ h < 23 | 23 ≤ h < 35 | 35 ≤ h | Total<br>demand<br>distortion |

|----------------------------------------------------------------|--------|-------------|-------------|-------------|--------|-------------------------------|

| Percent (%)                                                    | 4.0    | 2.0         | 1.5         | 0.6         | 0.3    | 5.0                           |

| Table 2-1 | <b>IEEE 1547</b> | Harmonic Li | imits |

|-----------|------------------|-------------|-------|

|-----------|------------------|-------------|-------|

<sup>a</sup>Even harmonics are limited to 25% of the odd harmonic limits above

The IEEE Std 1547, 1547.1 and 1547.2 are essential for maintaining safe and efficient EPSs. These standards define interconnection criteria for various types of distributed resources. Appendix A of 1547.1 defines specific test waveforms that are to be used to verify proper operation. While each test is important for proper functionality, this research will focus on testing abnormal voltage and frequency conditions, and anti-islanding.

## 3 Hardware-in-the-Loop System Realization

Introducing new elements onto the utility grid can be dangerous if these elements are untested for the many conditions that may occur. In order to perform these tests a system is needed that can simulate possible grid conditions repeatedly and accurately. HIL offers a unique and flexible way to simulate a grid environment in real time. During testing, the operator is able to retain control of system conditions and perform repeatable tests in an isolated environment, thus avoiding any damage to the utility grid that many consumers depend on. This chapter will describe how HIL can be used to simulate a grid environment in real-time.

#### 3.1 Overview

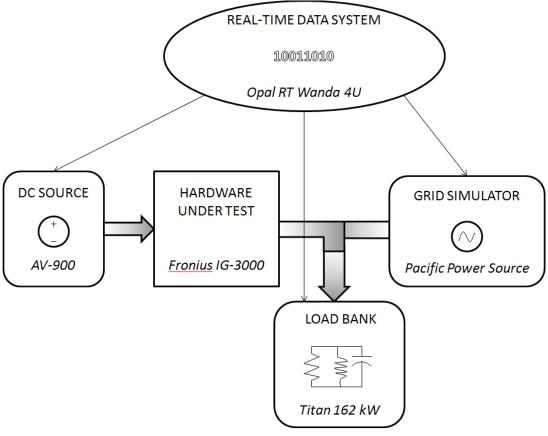

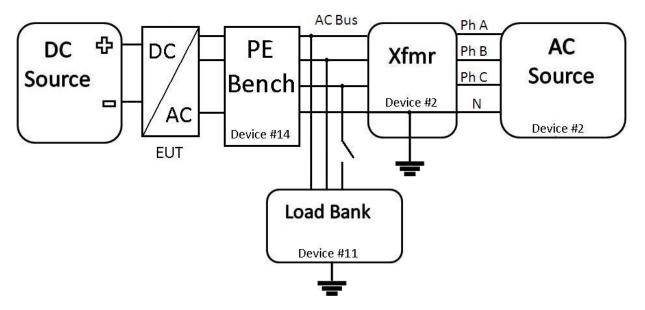

The HIL system of this thesis consists of a power amplifier to simulate the utility grid, load bank, PV inverter, DC power source and RTDS. Four power amplifiers are present in the lab where this thesis was conducted in. They are each rated to 50 kW for a total of 200 kW. For the purposes of this thesis, 6 kW will be sufficient to test and characterize an inverter. A 162 kW RLC load bank is also present and is used to sink power. The real-time data system (RTDS) was developed by Opal-RT Technologies and consists of a Wanda 4U target machine and a Windows based host machine. The DC power source was constructed by AeroVironment, model AV-900. A block diagram of the PHIL system used in this thesis can be seen in Figure 3-1.

Figure 3-1 PHIL Set-Up

Thin lines coming from the RTDS represent control signals. Thick, gradient lines represent actual power flow between components.

# 3.2 Grid Simulator

Simulating generation sources is a key element of this project. In order to achieve the power levels and controllability required, one 50 kW Pacific Power Source power amplifier was used to simulate the utility grid. While four of these exist at the DERTF and may be operated in parallel to achieve 200 kW, only one was necessary for this project.

# 3.2.1 Hardware

The Pacific Power Source amplifier, model 3060-MS, is a 3-phase unidirectional power flow amplifier capable of up to 62.5 kVA and 50 kW. Input AC power from the actual utility grid is rectified, conditioned and then converted back to AC output power efficiently. This method allows for very

accurate and high quality power output with 1% regulation and 1% total harmonic distortion. It is a very fast system with response times of 300  $\mu$ s for 100% load changes. Precision and controllability are crucial aspects when it comes to simulating an electric grid. Frequency and voltage deviations from set points must be minimal and harmonic content must be low in order to obtain valid results for interconnection testing. The 3060-MS will maintain output frequency within 0.01% and will regulate individual phase voltages within 0.5%. It has a frequency range of 47-500 Hz and a voltage range of 0-132 V<sub>L-N</sub> and a slew rate of 1 V/ $\mu$ s [**32**].

Another important aspect for grid integration testing is the apparent stiffness of the simulated grid. A stiffness ratio is defined by the Electric Power Research Institute as the ratio of available utility fault current to maximum rated output current of the DR [**33**]. This value is important because some DR will determine islanding conditions by attempting to control the grid voltage or frequency [**34**]. The grid simulator must be powerful enough to source enough power for the given loads and not allow anything else to regulate the voltage or frequency. In the set-up for this thesis, the utility grid is simulated by an AC bus. It is fed by the grid simulator through three, single phase autotransformers connected in a grounded wye-configuration. The transformer ratio is 2.216, yielding a maximum output voltage of 292.5  $V_{L-N}$ .

The grid simulator can be controlled locally or remotely. Local, front panel operation of the grid simulator, utilizes a knob to provide three discrete frequency settings and a screw to provide fine, per phase, voltage adjustment. This form of control is limited since frequency must remain constant and the variation of the voltage is constrained by how fast and precisely a screw can be turned by hand. For advanced testing, a greater deal of control is required. Remote control of the grid simulators is much more functional and can be implemented by use of an external oscillator input or serial communication. The Universal Programmable Controller, UPC-32, offers much more powerful control by means of analog and digital outputs from a remote location. Waveforms can be preprogrammed on the controller or

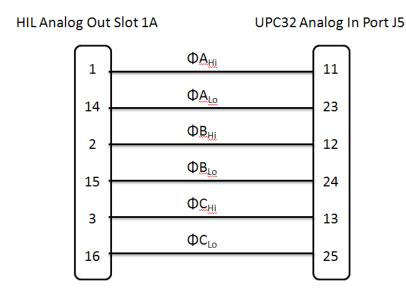

voltage levels can be modified in real-time. Limits can be set and metering is displayed on the front panel of the controller. During execution, the controller sends a scaled analog version of the waveforms to the 3060-MS external oscillator input which then amplifies the waveforms to actual power levels. In order to use this system as part of a larger HIL system, the UPC must be controlled by the RTDS. Waveforms from the RTDS are converted using a digital to analog converter and then sent to the UPC's auxiliary input port. These control signals are then sent from the UPC to the 3060-MS and amplified. A connection diagram showing the interface between the HIL Analog Out port and UPC Analog In port is shown below.

Figure 3-2 HIL to UPC-32 Connection Diagram

### 3.2.2 Software

Control of a simulated utility grid is necessary for performing integration tests. The grid, at the residential level where DRs less than 30 kVA might be installed, is normally a single phase 60 Hz sine wave at 120  $V_{L-N}$ . If this waveform was all that was necessary for testing, the grid simulators could be controlled from the front panel and no further interaction would be necessary. In order to simulate abnormal conditions though, some type of predetermined programmatic input is required. In this HIL system, control of the amplifier ultimately stems from a software program that was developed for this

thesis. The development environment for the program was MATLAB's Simulink [**35**]. It was used because the models built in Simulink can be compiled into C code and then executed on the RTDS. Also the software environment is extremely powerful and easy to use.

The user connects blocks which represent signals, math functions or communication with peripherals to create a program. Large libraries with various waveforms and math functions come builtin and more specific libraries, such as SimPowerSystems which contains elements such as power electronics, transmission lines, generators, etc., can be added. Blocks are also available for custom C code if the user desires a certain function that is not available from the Simulink libraries. Once these blocks' inputs and outputs have been connected, they can be grouped into subsystems to facilitate organization and other functions such as enabling or triggering. This creates an extremely powerful and flexible environment for developing models of different devices.

Each block contains some parameters that the user may set. At times though, more control is needed. Some modifications to the standard blocks were necessary to generate the signals that were necessary for IEEE 1547 testing. These modifications are described in the following sections.

The Simulink program developed for this thesis consists of two subsystems and a set of global variables at the top level.

### 3.2.2.1 Global Variables

The global variables set both simulation parameters and testing parameters. They are the main point of control, along with choice of which test to perform, the user has in the program.

The simulation parameters are simulation step size and end time. The simulation step size is important for resolution. Since this program will be run in real-time on a digital simulator, a fixed step size and fixed step size solver is required. While the RTDS is capable of a step size as small as 10  $\mu$ s [**36**], a 50  $\mu$ s step size was sufficient for this project since smooth waveforms with a minimum period of 16.13 ms were used.

Test parameters include operating voltage, ramp rates, step amount and steady-state duration. The user may define operating voltages within the range of the power amplifier. The program and grid simulator are capable of three phase operation, but the inverter used for this thesis connects to the grid in a split-phase configuration. Therefore, the user will set the operating voltage variable, *V<sub>rms</sub>*, to one half of the desired operating voltage, as dictated by the inverter specifications. The program is currently configured to control the grid simulator in split-phase automatically.

The ramp rate variables are used when either the frequency or voltage need to be ramped. Ramp rates are completely customizable in the program, though certain testing schemes generally set requirements. IEEE 1547.1 imposes constraints on the slopes in order to guarantee that the correct protection is tested. The formula for the slope is shown in Equation 2-1.

The steady-state duration parameter, *delay*, defines the amount of time, minus initial ramping (5 seconds), that a 60 Hz sine wave at the user-defined voltage will be output. The reconnect time setting on DRs is the reason for this variable. It a setting that prevents DRs from energizing the grid unless a quality (within voltage, frequency, harmonics, etc. limits) steady-state waveform is observed for that duration of the reconnect time. Once that constraint has been satisfied, a DR may begin energizing the grid and then testing can commence.

The duration of the test is defined by the end time variable, *endTime* minus the steady-state variable, *delay*. Once the simulation time is greater than the end time, the grid simulator waveforms are ramped down to zero so that re-energization by the inverter does not occur. Though there is protection built into the software, the user should still calculate what end waveform will result for the defined test duration and ramp rate to avoid any damage to equipment.

#### 3.2.2.2 Subsystems

The network of subsystems in this program can be reduced to two high-level subsystems, the console and the master. This configuration is dictated by the RTDS. They are differentiated by their

functionality and purpose. The console is run from the host machine and is intended to be a user interface. The master is run on the target machine and is intended to perform computations and interface with peripherals such as an field programmable gate array (FPGA) or controller area network (CAN) communication card. Data is interchanged between the two subsystems via a connection between the target machine and the host machine. This allows the user to see feedback and perform control functions.

### 3.2.2.2.1 Console Subsystem

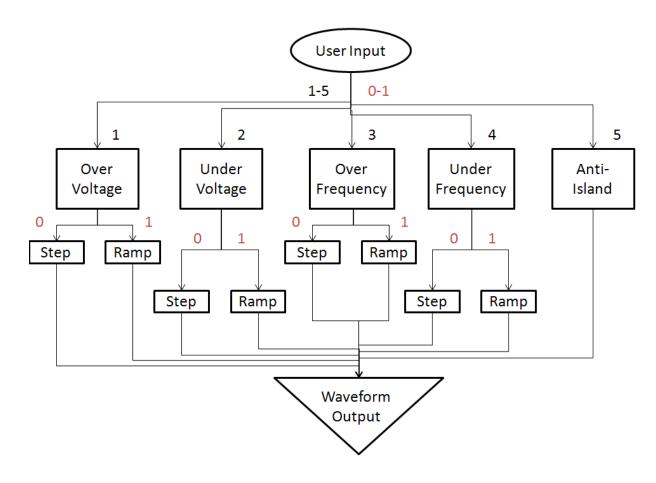

The console is the user interface. It is intended strictly for control signals and feedback displays. It is the only window that the user sees when the program is running in real-time. The console is used in this program for defining which test will be performed and to display errors that have occurred. There are two values that must be set by the user to determine which IEEE 1547 test will be run. One determines the parameter to be tested and the other determines what type of test will be performed. Instructions for the possible inputs are displayed on the console. Table 3-1 details the options that are available.

|       | User Input | Corresponding Test |  |

|-------|------------|--------------------|--|

|       | 1          | Over Voltage       |  |

|       | 2          | Under Voltage      |  |

| Box 1 | 3          | Over Frequency     |  |

|       | 4          | Under Frequency    |  |

|       | 5          | Anti-Islanding     |  |

| Box 2 | 0<br>1     | Step<br>Ramp       |  |

Table 3-1 Grid Simulator User Control Variables

Also included in the console are displays for each phase that show possible errors that could occur. An error is displayed when the waveforms output by the RTDS do not conform to protection specifications defined in the program. The analog outputs of the RTDS that control the grid simulators are looped-back to the analog inputs of the RTDS and then passed through an error checking block in the master subsystem. The errors include upper and lower frequency limits, upper voltage limits and volt second balance. These errors are derived from the capabilities of the grid simulator and output transformer.

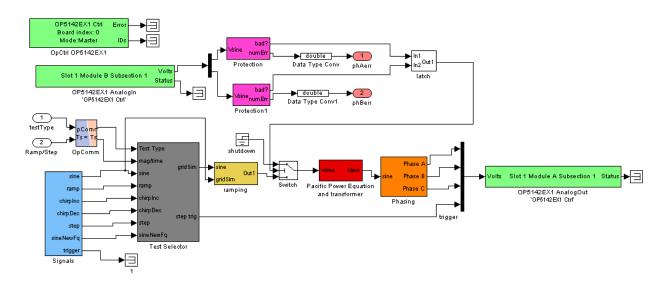

### 3.2.2.3 Master Subsystem