# Low Profile, High Power Density and High Efficiency DC-DC Converters

by

# Yushi Liu

B.A., University of Electronic Science and Technology of China, 2011

M.S., University of Electronic Science and Technology of China, 2014

M.S., University of Colorado Boulder, 2016

A thesis submitted to the Faculty of the Graduate School of the University of Colorado in partial fulfillment of the requirements for the degree of Doctor of Philosophy Department of Electrical Electrical, Computer, and Energy Engineering

2018

This thesis entitled: Low Profile, High Power Density and High Efficiency DC-DC Converters written by Yushi Liu has been approved for the Department of Electrical Electrical, Computer, and Energy Engineering

Prof. Khurram K. Afridi

Prof. Dragan Maksimovic

Date \_\_\_\_\_

The final copy of this thesis has been examined by the signatories, and we find that both the content and the form meet acceptable presentation standards of scholarly work in the above mentioned discipline. Liu, Yushi (Ph.D., Electrical, Computer, and Energy Engineering)

Low Profile, High Power Density and High Efficiency DC-DC Converters

Thesis directed by Prof. Khurram K. Afridi

Due to the ever decreasing thickness and increasing battery size of modern cellphones, battery chargers inside cellphones are required to meet increasingly stringent power density requirements, including small printed circuit board (PCB) area and component height. This thesis is focused on low-profile, high-power-density, and high-efficiency dc-dc converters for battery charging applications.

This thesis investigates five topologies, including ZVS-QSW buck converter, threelevel buck converter, four-level buck converter, a resonant switched capacitor converter, and a new reconfigurable hybrid switched capacitor converter. The operation principle of each topology is described, and the advantages and disadvantages of each topology are analyzed and compared in terms of efficiency and power density. To accurately evaluate the performance of each topology, this thesis utilizes the augmented state-space modeling method that efficiently calculates the steady-state waveforms of a converter. To accurately predict losses, the dynamic on-resistance of GaN transistors and core loss of inductors have been modeled. Furthermore, a comprehensive optimization methodology is utilized to select circuit and component parameters.

First, for nominal 2:1 step-down conversion ratio application for which the three-level buck converter is best suited, two prototypes of the three-level buck converter, one using GaN transistors and the other using low-voltage Silicon MOSFETs are designed, built and tested. Both converters are designed for an input voltage range of 5 V to 20 V, an output voltage range of 3 V to 4.2 V, and a maximum output current of 10 A. The prototype with the GaN transistors (EPC2023) occupies a PCB area of 358 mm<sup>2</sup> and has a component height of 1 mm. To maximize efficiency, the converter is designed to achieve ZVS at lightto-medium loads, while sacrificing ZVS to reduce transistor conduction and inductor losses. This GaN-based prototype converter achieves a peak efficiency of 98.5% at 2:1 conversion ration and high efficiency at other operating conditions with a power density of 704 W/in<sup>3</sup>. The prototype using low-voltage Silicon MOSFETs (CPF03433) has a slightly smaller PCB area of 310 mm<sup>2</sup>, but its efficiency at high output currents is substantially lower than that of the GaN-based prototype. Next, for a nominal 3:1 step-down conversion ratio application for which the four-level buck converter is best suited, a prototype of four-level buck converter with a PCB area of 410 mm<sup>2</sup> and a component height of 1mm, optimized for 3:1 step-down, is built and tested. Finally, for an extreme-power-density application, where the converter is required to deliver a maximum output power of 40 W at an output voltage in the range of 3 V to 4.2 V and an input voltage in the range of 5 V to 20 V, with its PCB footprint limited to only 80 mm<sup>2</sup> and its component height limited to 1 mm, a prototype 1-MHz ZVS-QSW buck converter is built and tested. This prototype converter achieves a peak efficiency of 96.7% and a power density of 3230 W/in<sup>3</sup>.

Dedication

To all who have helped me.

### Acknowledgements

I would like to express my sincere gratitude to my advisor, Prof. Khurram Afridi, for his guidance and support through out my Ph.D program at CU Boulder. He has very deep knowledge and understanding of various facets of power electronics, especially related to high-frequency resonant converters. He encouraged me to do hard work and be relentless. He has also taught me with academic writing and presentation. I would also like to thank my co-advisor Prof. Dragan Makismovic for importing his knowledge and providing guidance through my Ph.D years. His approach to isolating and solving problems really inspired me.

I would also like to acknowledge the support from the other members of my thesis committee: Prof. Robert Erickson, Prof. Hanh-Phuc Le and Prof. Daniel Costinett. Their advice has helped make this thesis stronger. I am also grateful to the sponsors of my research: Texas Instruments and Huawei Technologies. Of my colleagues at CoPEC, I especially thank Ashish Kurmar for his constant help in my Ph.D years. We have spent so many nights in discussions, conducting experiments and writing. This thesis would not be possible without his help. I also thank Fenglong Lu, Jie lu, Hua Chen, Yuanzhe Zhang, Fan Zhang, Yucheng Gao and Tianshi Xie for the discussions on power electronics. I also thank Saad Pervaiz, Prasanta Achanta, Sreyam Sinha, Ratul Das and Brandon Regensburger for their support in the lab, and thanks to Casey Hardy and Colin McHugh for their help on analog IC design.

I also thank Zhe Feng, Duanfeng Gao, my roomate Bo Ding and my other friends in Colorado for making the last few years so much more fun. Finally, I thank my parents for their help and support through out my entire life.

# Contents

# Chapter

| 1        | Intr | oductio  | n                                                     | 1  |

|----------|------|----------|-------------------------------------------------------|----|

|          | 1.1  | Backg    | round and Motivation                                  | 1  |

|          | 1.2  | State    | of the Art and Thesis Objectives                      | 2  |

|          | 1.3  | Contra   | ibutions of the Thesis                                | 3  |

|          | 1.4  | Thesis   | organization                                          | 6  |

| <b>2</b> | Alte | ernative | Battery Charger Topologies                            | 8  |

|          | 2.1  | Zero-V   | Voltage Switching Quasi-Square-Wave Buck Converter    | 8  |

|          | 2.2  | Three    | -Level Buck Converter                                 | 9  |

|          | 2.3  | Reson    | ant Switched Capacitor Converter                      | 11 |

|          | 2.4  | Four-I   | Level Buck Converter                                  | 14 |

|          | 2.5  | Recon    | figurable Hybrid Switched Capacitor Converter         | 16 |

| 3        | Desi | ign Tecl | hniques                                               | 19 |

|          | 3.1  | Augm     | ented State-Space Modeling                            | 19 |

|          | 3.2  | Loss N   | Models for the DC-DC Converter                        | 24 |

|          |      | 3.2.1    | Theoretical Loss Model for the DC-DC Converter        | 25 |

|          |      | 3.2.2    | Thermal Resistance of Switch, Inductor and PCB Traces | 28 |

|          |      | 3.2.3    | Dynamic On Resistance of GaN Transistors              | 32 |

|          |      | 3.2.4    | Steinmetz Parameters for Core Loss                    | 34 |

|          | 3.3  | Predicted Efficiency Across Wide Input Voltage Range                     | 38 |

|----------|------|--------------------------------------------------------------------------|----|

| 4        | High | n-Efficiency Nominal 2-to-1 Step-Down Converter Design                   | 41 |

|          | 4.1  | Three-Level Buck Converter Topology and Operating Principles             | 42 |

|          |      | 4.1.1 ZVS Operation of Three-Level Buck Converter                        | 43 |

|          | 4.2  | Modeling, Design and Optimization Methodology                            | 44 |

|          |      | 4.2.1 Augmented State-Space Modeling                                     | 44 |

|          |      | 4.2.2 Design and Optimization Procedure                                  | 47 |

|          | 4.3  | Experimental Results                                                     | 50 |

|          |      | 4.3.1 Three-Level Buck Converter with GaN Transistor                     | 50 |

|          |      | 4.3.2 Three-Level Buck Converter with Low-Voltage Silicon MOSFET         | 52 |

| <b>5</b> | High | n-Efficiency Nominal 3-to-1 Step Down Converter Design                   | 61 |

|          | 5.1  | Four-Level Buck Converter Topology and Operating Principles              | 62 |

|          | 5.2  | Augmented State-Space Modeling of Four-Level Buck Converter              | 64 |

|          | 5.3  | Reconfigurable Switched Capacitor Converter Topology and Operating Prin- |    |

|          |      | ciples                                                                   | 67 |

|          | 5.4  | Augmented State-Space Modeling of Reconfigurable Switched Capacitor Con- |    |

|          |      | verter                                                                   | 70 |

|          | 5.5  | Comparison of Four-Level Buck and Reconfigurable Switched Capacitor Con- |    |

|          |      | verter                                                                   | 74 |

|          | 5.6  | Prototype and Experimental Results                                       | 76 |

| 6        | Extr | eme-Power-Density Battery Charger Design                                 | 81 |

|          | 6.1  | Design Methodology                                                       | 82 |

|          | 6.2  | Performance Comparison                                                   | 85 |

|          | 6.3  | Experimental Result                                                      | 86 |

viii

| Cond | clusions and Future Work | 90                                                    |

|------|--------------------------|-------------------------------------------------------|

| 7.1  | Summary                  | 90                                                    |

| 7.2  | Conclusions              | 92                                                    |

| 7.3  | Future Work              | 96                                                    |

|      | 7.1<br>7.2               | Conclusions and Future Work         7.1       Summary |

ix

99

# Bibliography

# Appendix

| Α | Mat | lab Script for Augmented State Space Modeling for Each Topology      | 104 |

|---|-----|----------------------------------------------------------------------|-----|

|   | A.1 | Matlab Script for QSW-ZVS Buck Converter                             | 104 |

|   | A.2 | Matlab Script for Three-level Buck Converter                         | 106 |

|   | A.3 | Matlab Script for Four-Level Buck Converter                          | 111 |

|   | A.4 | Matlab Script for Reconfigurable Hybrid Switched Capacitor Converter | 123 |

# Tables

Table

| 1.1 | Commercial Power Inductor Product List                                                          | 3  |

|-----|-------------------------------------------------------------------------------------------------|----|

| 3.1 | Temperature of switches, planar inductor and PCB trace when the $ZVS$ - $QSW$                   |    |

|     | buck converter is operated at input voltage $V_{\rm IN} = 5 V$ , output voltage $V_{\rm OUT} =$ |    |

|     | 4V, for various output current conditions, with room temperature is 22.8°C.                     | 31 |

| 3.2 | Measured dynamic on-resistance of EPC2023 GaN switch operated at $1 \mathrm{MHz}$               |    |

|     | switching frequency with different drain to source voltage: $V_{ds} = 5V, V_{ds} =$             |    |

|     | $8V$ , and $V_{ds} = 12V$ , compared with datasheet value                                       | 34 |

| 3.3 | Core loss $P_{core}$ , ac flux density $\Delta B$ and maximum flux density $B_{max}$ at input   |    |

|     | voltage $V_{\rm IN} = 5 V$ , output voltage $V_{\rm OUT} = 4 V$ , and switching frequency       |    |

|     | $f_s = 1250 \mathrm{kHz}.$                                                                      | 37 |

| 3.4 | Core loss $P_{core}$ , ac flux density $\Delta B$ and maximum flux density $B_{max}$ at input   |    |

|     | voltage $V_{\rm IN} = 8 V$ , output voltage $V_{\rm OUT} = 4 V$ , and switching frequency       |    |

|     | $f_s = 2000 \mathrm{kHz}.$                                                                      | 37 |

| 3.5 | Core loss $P_{core}$ , ac flux density $\Delta B$ and maximum flux density $B_{max}$ at input   |    |

|     | voltage $V_{\rm IN} = 12 V$ , output voltage $V_{\rm OUT} = 4 V$ , and switching frequency      |    |

|     | $f_s = 1750 \mathrm{kHz}.$                                                                      | 37 |

| 4.1 | Components used in the power stage of the GaN prototype three-level buck                        |    |

|     | converter.                                                                                      | 51 |

|     |                                                                                                 |    |

| 4.2 | Components used in the power stage of the prototype three-level buck con-                         |    |

|-----|---------------------------------------------------------------------------------------------------|----|

|     | verter with low-voltage silicon MOSFET                                                            | 52 |

| 4.3 | The comparison of two prototypes with GaN transistor (EPC2023) and low-                           |    |

|     | voltage silicon MOSFET (CPF03433).                                                                | 53 |

| 5.1 | Components used in the power stage of the four-level buck converter prototype.                    | 77 |

| 6.1 | Predicted performance of the ZVS-QSW buck, three-level buck and resonant                          |    |

|     | switched capacitor converters at the nominal operating point of input voltage                     |    |

|     | $V_{\rm IN}=12$ V, output voltage $V_{\rm OUT}=4$ V, and output current $I_{\rm OUT}=10$ A. $~$ . | 85 |

| 6.2 | Components used in the power stage of the prototype ZVS-QSW buck converter                        | 88 |

| 7.1 | Comparison of TI's bq25910 and EPC2023 based prototype                                            | 91 |

# Figures

# Figure

| 1.1 | State-of-the-art commercial DC-DC converters, suitable for cellphone battery         |    |

|-----|--------------------------------------------------------------------------------------|----|

|     | charging application. Indicated efficiency is with input voltage of 12 V, output     |    |

|     | voltage of 4 V and output current of 10 A                                            | 2  |

| 2.1 | Zero-Voltage Switching Quasi-Square-Wave Buck (ZVS-QSW) converter topol-             |    |

|     | ogy                                                                                  | 8  |

| 2.2 | The three level buck converter topology.                                             | 9  |

| 2.3 | Gate signals of $Q_1, Q_2, Q_3, Q_4$ switch-node voltage and inductor current for    |    |

|     | duty ratio $D < 0.5, D = 0.5$ , and $D > 0.5$ .                                      | 10 |

| 2.4 | Four-switch ladder resonant switched capacitor converter topology                    | 11 |

| 2.5 | Gate signals of $Q_1, Q_2, Q_3, Q_4$ of the four-switch ladder resonant switched     |    |

|     | capacitor converter.                                                                 | 12 |

| 2.6 | Comparison between the output voltage of the four-switch ladder resonant             |    |

|     | switched capacitor converter, as predicted by the conventional lossless analysis     |    |

|     | and augmented state-space analysis including losses                                  | 13 |

| 2.7 | Four-level buck converter topology.                                                  | 14 |

| 2.8 | Gate signals of $Q_1, Q_2, Q_3, Q_4, Q_5, Q_6$ and switch-node voltage of four level |    |

|     | buck converter when duty ratio $D < 1/3$ and $1/3 < D < 2/3$                         | 15 |

| 2.9 | Reconfigurable hybrid switched capacitor converter topology.                         | 16 |

| 2.10 | Gate signals of $Q_1, Q_2, Q_3, Q_4, Q_5, Q_6$ and switch-node voltage of reconfig-                         |    |

|------|-------------------------------------------------------------------------------------------------------------|----|

|      | urable hybrid switched capacitor converter when output voltage $V_{\text{OUT}} < \frac{V_{\text{IN}}}{3}$ . | 17 |

| 3.1  | The three-level topology                                                                                    | 20 |

| 3.2  | Operation and corresponding states of three level buck converter when $D < 0.5$ .                           | 21 |

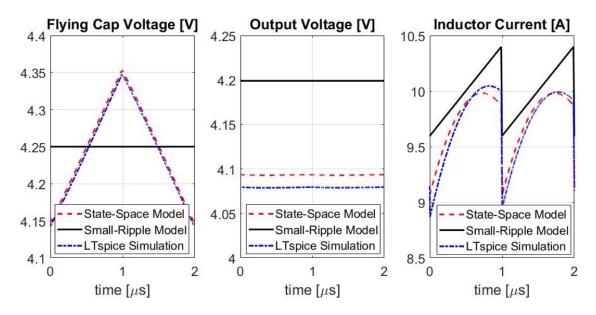

| 3.3  | Comparison between example waveforms of three-level buck converter as pre-                                  |    |

|      | dicted by augmented state-space modeling, small-ripple approximation and                                    |    |

|      | LTSpice simulations at input voltage $V_{\rm IN} = 12 V$ , output voltage $V_{\rm OUT} = 4 V$ ,             |    |

|      | and output current $I_{\text{OUT}} = 10 A$                                                                  | 25 |

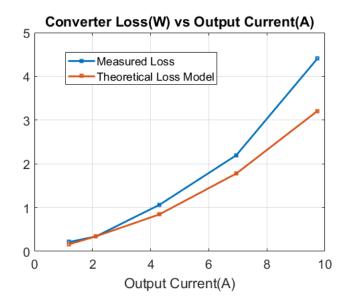

| 3.4  | Comparison of loss model predicted and measured efficiency for QSW-ZVS                                      |    |

|      | buck converter over full range of output current                                                            | 28 |

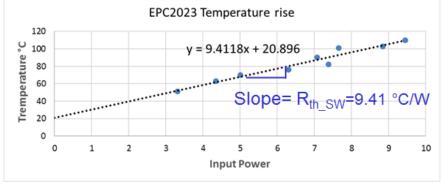

| 3.5  | GaN transistor (EPC2023) thermal resistance measurement results                                             | 29 |

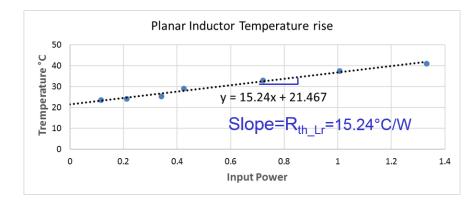

| 3.6  | Customized planar inductor thermal resistance measurement results                                           | 29 |

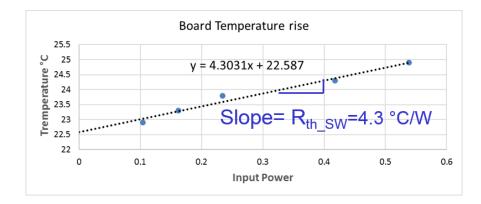

| 3.7  | Printed circuit board thermal resistance measurement results                                                | 30 |

| 3.8  | QSW-ZVS buck converter with switches and inductor thermally decoupled                                       | 30 |

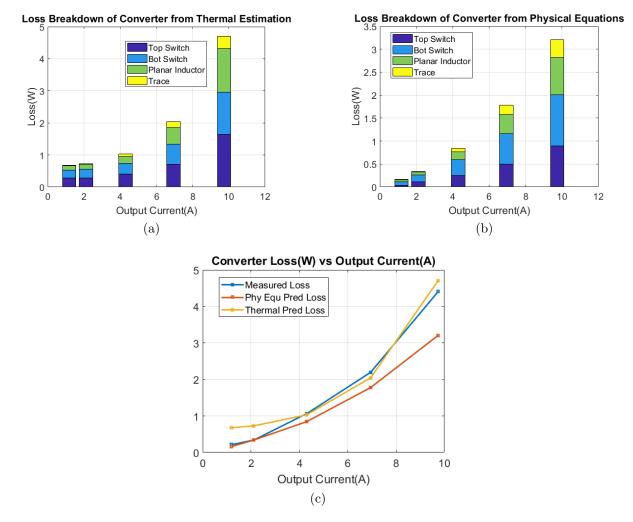

| 3.9  | Loss breakdown of the ZVS-QSW buck based on (a) thermal results and (b)                                     |    |

|      | theoretical loss model and (c) the comparision with measured loss, when the                                 |    |

|      | converter is operating at input voltage $V_{\rm IN} = 5 V$ , output voltage $V_{\rm OUT} = 4 V$ ,           |    |

|      | for various load conditions                                                                                 | 31 |

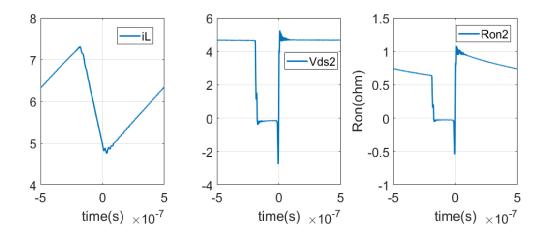

| 3.10 | The GaN switch drain to source voltage $V_{ds}$ , current $i_{ds}$ and on resistance                        |    |

|      | $R_{ds,on}$ at the operating point of input voltage $V_{\rm IN} = 5 V$ , output voltage                     |    |

|      | $V_{\text{OUT}} = 4 V$ , and output current $I_{\text{OUT}} = 6A$                                           | 34 |

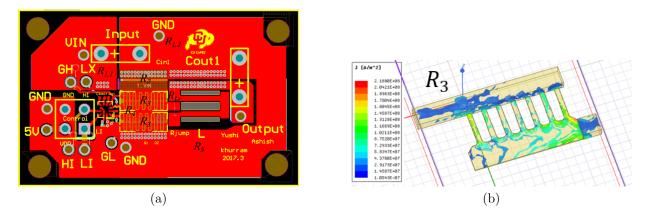

| 3.11 | PCB trace on-resistance of the ZVS-QSW buck (a) PCB layout of buck con-                                     |    |

|      | verter (b) Finite-element analysis of PCB trace on-resitance                                                | 34 |

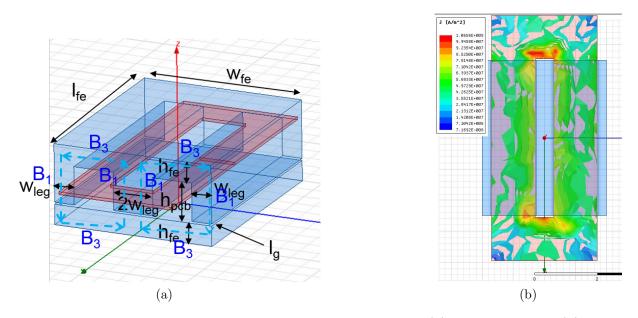

| 3.12 | Planar inductor ac resistance simulation result: (a) core geometry; (b) finite-                             |    |

|      | element analysis of winding ac resistance at 1MHz                                                           | 35 |

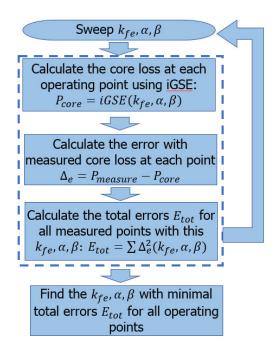

| 3.13 | Flowchart detailing the proposed methodology to get steinmetz parameter                          |    |

|------|--------------------------------------------------------------------------------------------------|----|

|      | $k_{fe}$ , $\alpha$ and $\beta$ for 3F46 ferrite material                                        | 38 |

| 3.14 | Calibrated steinmetz parameter $k_{fe}$ , $\alpha$ and $\beta$ for 3F46 material                 | 38 |

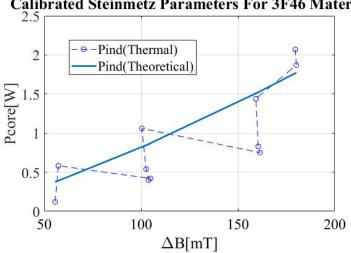

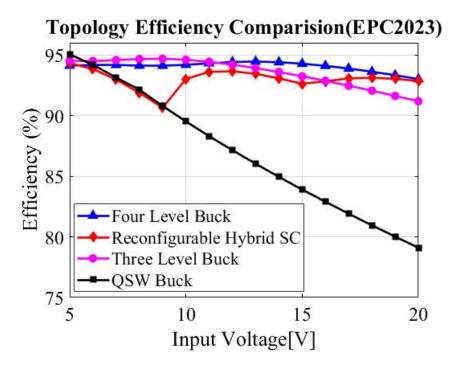

| 3.15 | Predicted efficiency of QSW buck, three-level buck, reconfigurable hybrid                        |    |

|      | switched capacitor and four level buck converter, across full input voltage                      |    |

|      | range at output voltage $V_{\text{OUT}} = 4 V$ , output current $I_{\text{OUT}} = 10 A$          | 39 |

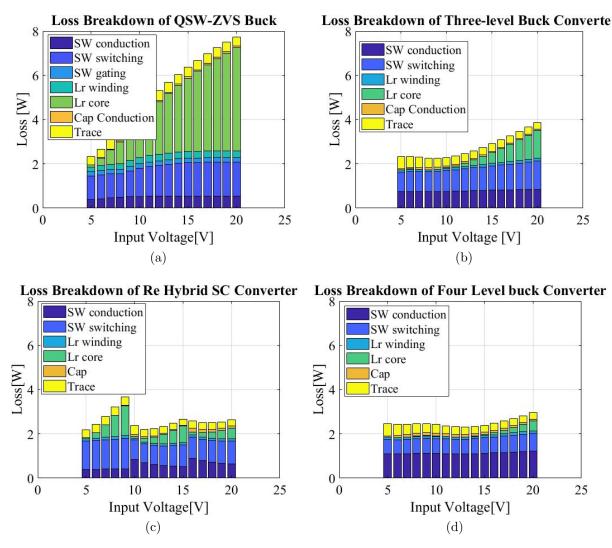

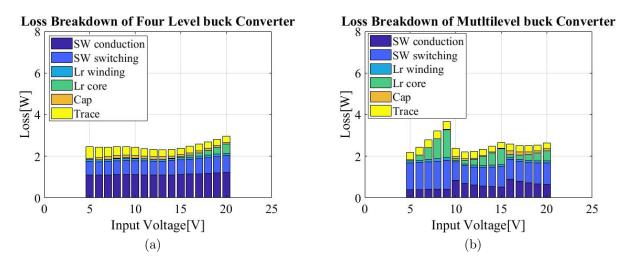

| 3.16 | Loss breakdown of four buck converter topologies across full input voltage                       |    |

|      | range at output voltage $V_{\text{OUT}} = 4$ V, output current $I_{\text{OUT}} = 10$ A: (a) QSW- |    |

|      | ZVS Buck Converter; (b) Three-Level Buck Converter; (c) Reconfigurable                           |    |

|      | Hybrid Switched Capacitor Converter; (d) Four-Level Buck Converter                               | 40 |

| 4.1  | The three level buck converter topology.                                                         | 42 |

| 4.2  | Gate signals of $Q_1, Q_2, Q_3, Q_4$ switch-node voltage and inductor current for                |    |

|      | duty ratio $D < 0.5, D = 0.5$ , and $D > 0.5$ .                                                  | 44 |

| 4.3  | Operation and corresponding states of three level buck converter when duty                       |    |

|      | ratio $D < 0.5.$                                                                                 | 45 |

| 4.4  | Comparison between example waveforms of three-level buck converter as pre-                       |    |

|      | dicted by augmented state-space modeling, small-ripple approximation and                         |    |

|      | LTSpice simulations at input voltage $V_{\rm IN} = 8.5$ V, output voltage $V_{\rm OUT} = 4$      |    |

|      | V, and output current $I_{OUT} = 10 \text{ A}$                                                   | 46 |

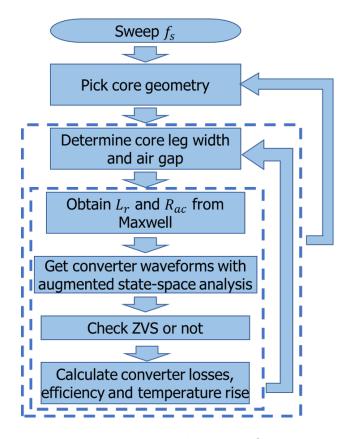

| 4.5  | Design methodology flow chart.                                                                   | 47 |

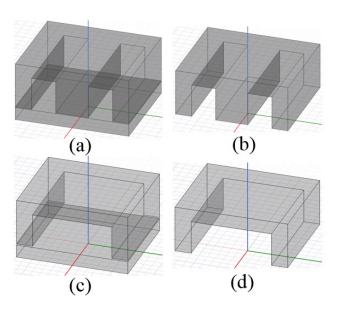

| 4.6  | Four core geometries considered: (a) EI core; (b) E core; (c) UI core; (d) U                     |    |

|      | core                                                                                             | 48 |

| 4.7  | ZVS turn-on transition of $Q_1$                                                                  | 49 |

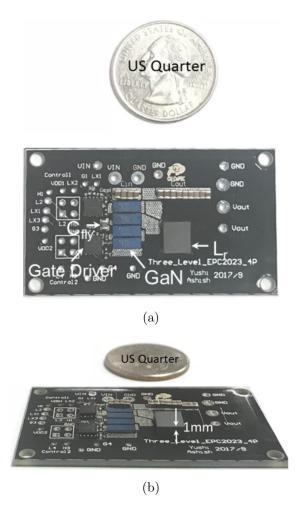

| 4.8  | Photograph of the prototype three-level buck converter with EPC2023: (a)                         |    |

|      | top view, and (b) side view.                                                                     | 50 |

|      |                                                                                                  |    |

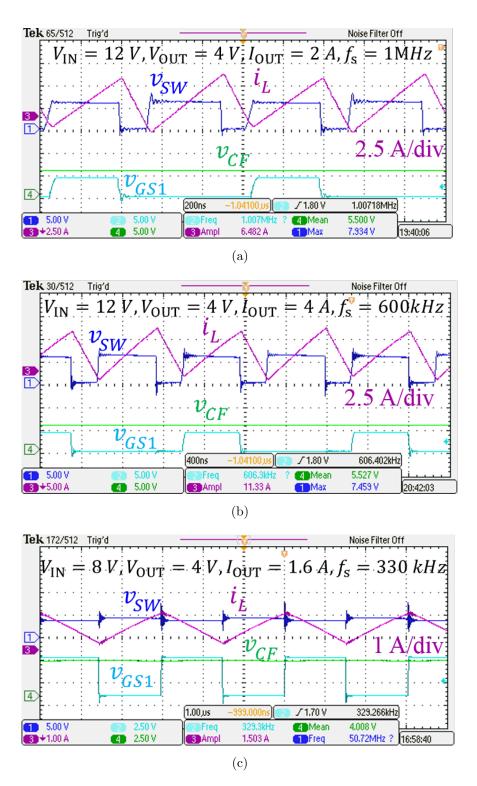

| 4.9  | Measured waveforms of the three-level buck converter: (a) ZVS performance                                   |    |

|------|-------------------------------------------------------------------------------------------------------------|----|

|      | of the converter at input voltage $V_{\rm IN}=12$ V, output voltage $V_{\rm OUT}=4$ V, and                  |    |

|      | output current $I_{\text{OUT}}=2$ A. (b) ZVS performance of the converter at input                          |    |

|      | voltage $V_{\text{IN}}=12$ V, output voltage $V_{\text{OUT}}=4$ V, and output current $I_{\text{OUT}}=4$ A. |    |

|      | (c) Measured waveforms of the converter at input voltage $V_{\rm IN}=8$ V, output                           |    |

|      | voltage $V_{\text{OUT}}=4$ V, and output current $I_{\text{OUT}}=1.6$ A                                     | 55 |

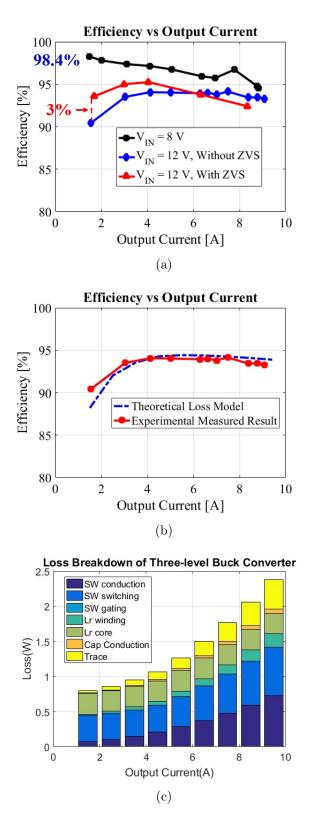

| 4.10 | Measured efficiency and loss breakdown of the three-level buck converter: (a)                               |    |

|      | measured efficiency at different operating conditions; (b) comparison of loss                               |    |

|      | model predicted and measured efficiency; (c) loss breakdown of the converter                                |    |

|      | at input voltage $V_{\text{IN}}=12$ V, output voltage $V_{\text{OUT}}=4$ V over full range of output        |    |

|      | current.                                                                                                    | 56 |

| 4.11 | Photograph of the prototype three-level buck converter with silicon MOSFETs                                 |    |

|      | (CPF03433)                                                                                                  | 57 |

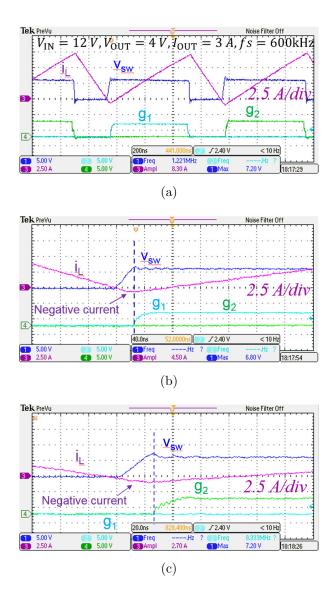

| 4.12 | Measured waveforms of the three-level buck converter with CPF03433: (a)                                     |    |

|      | ZVS performance of the converter at input voltage $V_{\rm IN}=12$ V, output voltage                         |    |

|      | $V_{\rm OUT}=4$ V, and output current $I_{\rm OUT}=3$ A. (b) Expanded waveforms confirm-                    |    |

|      | ing ZVS turn-on of $Q_1$ . (c) Expanded waveforms confirming ZVS turn-on of                                 |    |

|      | $Q_2$                                                                                                       | 58 |

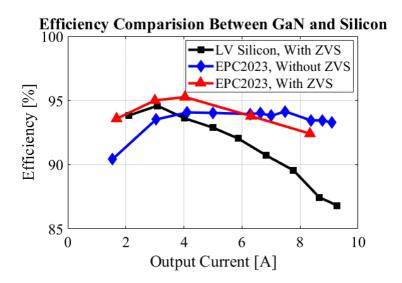

| 4.13 | Efficiency comparison between GaN and silicon prototype at input voltage                                    |    |

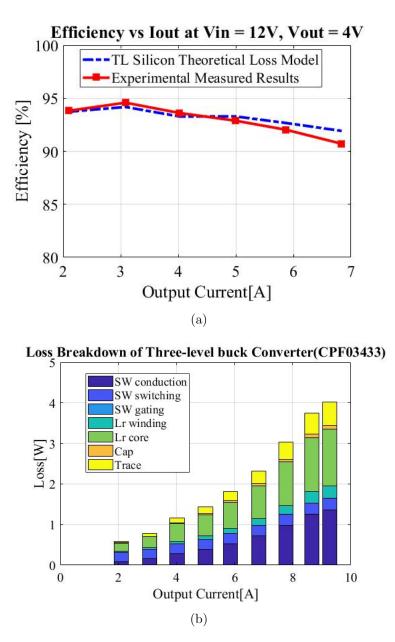

|      | $V_{\rm IN} = 12$ V, output voltage $V_{\rm OUT} = 4$ V for full load condition                             | 59 |

| 4.14 | Measured efficiency and loss breakdown of the three-level buck converter with                               |    |

|      | CPF03433: (a) Comparison of loss model predicted and measured efficiency.                                   |    |

|      | (c) Loss breakdown of the converter at input voltage $V_{\rm IN}=12$ V, output voltage                      |    |

|      | $V_{\rm OUT}=4$ V over full range of output current                                                         | 60 |

| 5.1  | Four-level buck converter topology.                                                                         | 62 |

| 5.2  | Gate signals of $Q_1, Q_2, Q_3, Q_4, Q_5, Q_6$ and switch-node voltage of four level                               |    |

|------|--------------------------------------------------------------------------------------------------------------------|----|

|      | buck converter when duty ratio $D < 1/3$ and $1/3 < D < 2/3$                                                       | 63 |

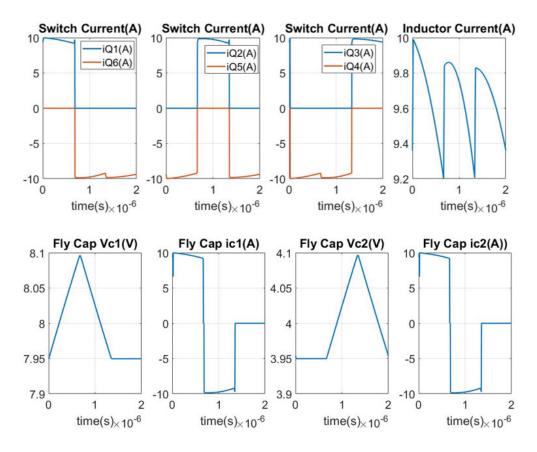

| 5.3  | Equivalent circuits when switches $Q_1, Q_2$ and $Q_3$ are on                                                      | 66 |

| 5.4  | Operation and corresponding states of four-level buck converter for different                                      |    |

|      | duty ratio                                                                                                         | 66 |

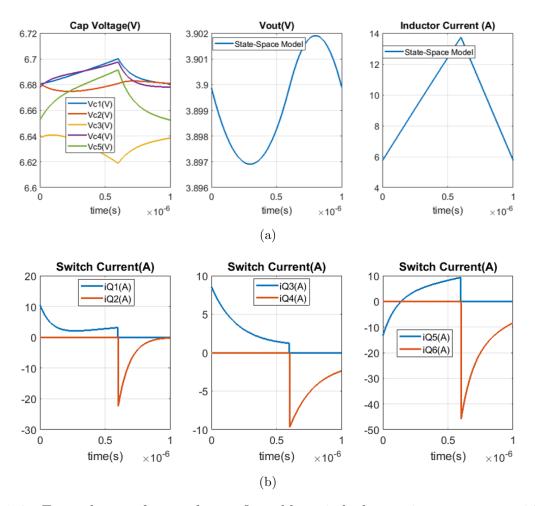

| 5.5  | Example waveforms of four-level buck converter with augmented state-space                                          |    |

|      | modeling at input voltage $V_{\rm IN} = 12 V$ , output voltage $V_{\rm OUT} = 4 V$ , and output                    |    |

|      | current $I_{\text{OUT}} = 10 A$                                                                                    | 68 |

| 5.6  | Proposed reconfigurable switched capacitor converter topology                                                      | 69 |

| 5.7  | Gate signals of $Q_1, Q_2, Q_3, Q_4, Q_5, Q_6$ and switch-node voltage of reconfig-                                |    |

|      | urable switched capacitor converter when $V_{\text{OUT}} < \frac{V_{\text{IN}}}{3}$                                | 69 |

| 5.8  | The equivalent circuit of (a) $Mode_{135}$ and (b) $Mode_{246}$ .                                                  | 71 |

| 5.9  | Example waveforms of reconfigurable switched capacitor converter with aug-                                         |    |

|      | mented state-space modeling at input voltage $V_{\rm IN} = 20V$ , output voltage                                   |    |

|      | $V_{\rm OUT} = 4V$ , and output current $I_{\rm OUT} = 10A$ : (a) flying capacitor voltage                         |    |

|      | $(V_{c1}, V_{c2} \text{ and } V_{c5})$ , output voltage $V_{OUT}$ , and inductor current $i_L$ ; (b) each          |    |

|      | switch current $(i_{Q1}, i_{Q2} \text{ and } i_{Q6})$                                                              | 74 |

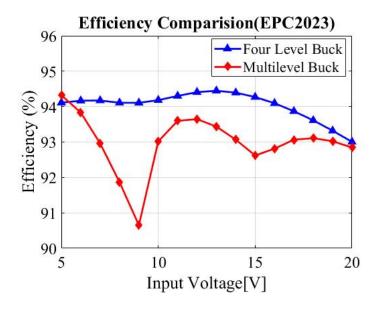

| 5.10 | Predicted efficiency of reconfigurable switched capacitor and four level buck                                      |    |

|      | converter, across full input voltage range at output voltage $V_{\text{OUT}} = 4 V$ , out-                         |    |

|      | put current $I_{OUT} = 10 A.$                                                                                      | 75 |

| 5.11 | Loss breakdown of two buck converter topologies across full input voltage                                          |    |

|      | range at output voltage $V_{\text{OUT}} = 4V$ , output current $I_{\text{OUT}} = 10A$ : (a) Four-                  |    |

|      | Level Buck Converter; (b) Reconfigurable Switched Capacitor Converter                                              | 75 |

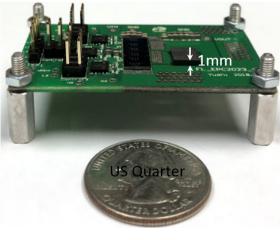

| 5.12 | Photograph of the prototype four-level buck converter with EPC2023: (a) top                                        |    |

|      | view, and (b) side view. $\ldots$ | 76 |

|      |                                                                                                                    |    |

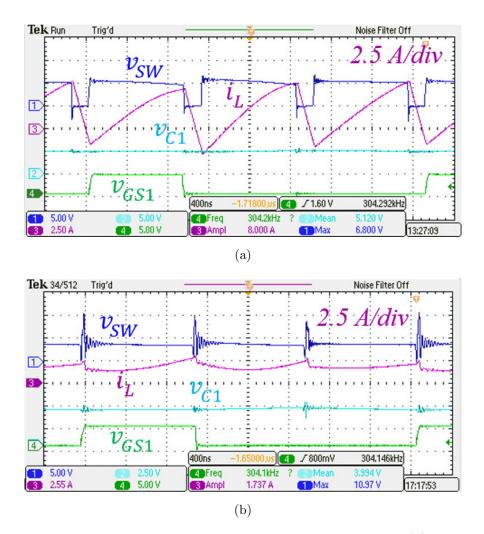

| 5.13 | B Measured waveforms of the four-level buck converter: (a) ZVS performance of                                |    |

|------|--------------------------------------------------------------------------------------------------------------|----|

|      | the converter at input voltage $V_{\rm IN}=15$ V, output voltage $V_{\rm OUT}=4$ V, output                   |    |

|      | current and $I_{\rm OUT}=2$ A. (b) Measured waveforms of the converter at input                              |    |

|      | voltage $V_{\text{IN}}=12$ V, output voltage $V_{\text{OUT}}=4$ V, and output current $I_{\text{OUT}}=2$ A.  | 78 |

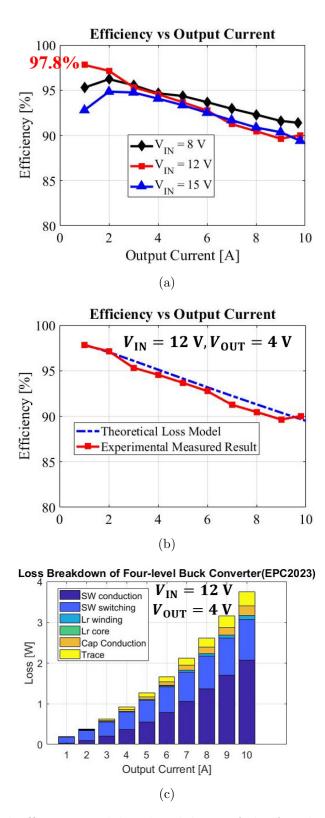

| 5.14 | Measured efficiency and loss breakdown of the four-level buck converter: (a)                                 |    |

|      | measured efficiency at different operating conditions. (b) Comparison of loss                                |    |

|      | model predicted and measured efficiency. (c) Loss breakdown of the converter                                 |    |

|      | at input voltage $V_{\text{IN}}=12$ V, output voltage $V_{\text{OUT}}=4$ V over full range of output         |    |

|      | current.                                                                                                     | 79 |

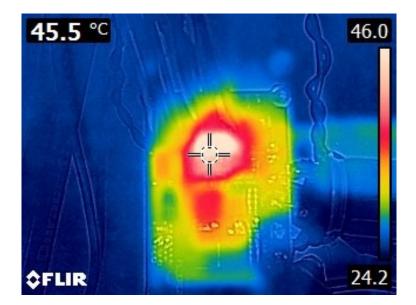

| 5.15 | 5 The measured thermal image of four-level buck converter when operating at in-                              |    |

|      | put voltage $V_{\text{IN}}=12$ V, output voltage $V_{\text{OUT}}=4$ V, and output current $I_{\text{OUT}}=8$ |    |

|      | A                                                                                                            | 80 |

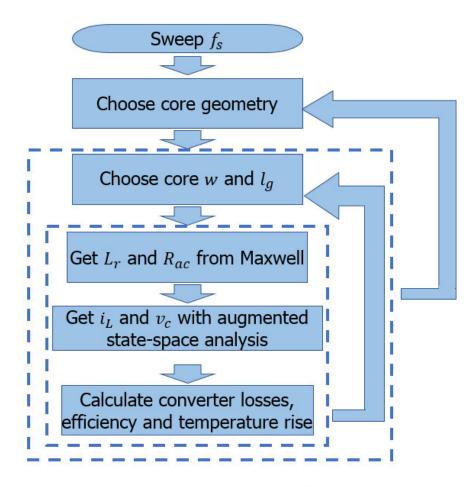

| 6.1  | Design methodology for 80 $\text{mm}^2$ battery charger design                                               | 82 |

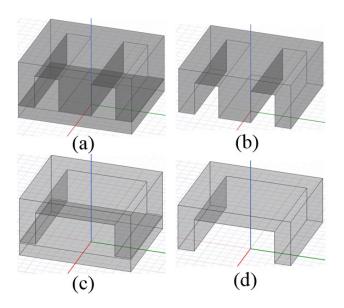

| 6.2  | Four core geometries considered: (a) EI core; (b) E core; (c) UI core; (d) U                                 |    |

|      | core                                                                                                         | 84 |

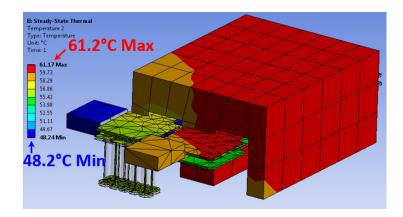

| 6.3  | Finite-element analysis based thermal map of an example inductor design.                                     | 84 |

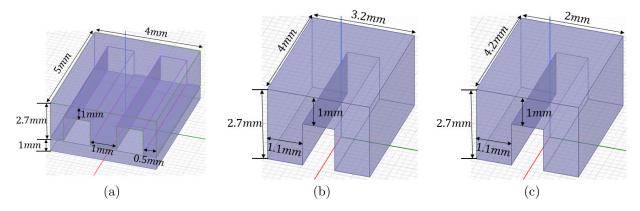

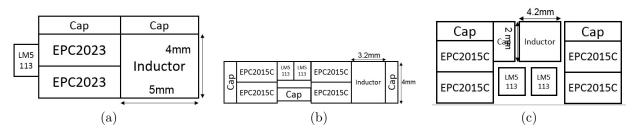

| 6.4  | Inductor geometry for (a)ZVS-QSW buck, (b)three-level buck and (c)resonant                                   |    |

|      | switched capacitor converters.                                                                               | 86 |

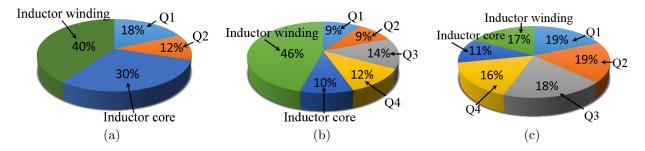

| 6.5  | Floor plan of the (a)ZVS-QSW buck, (b)three-level buck, and (c)resonant                                      |    |

|      | switched capacitor converters                                                                                | 86 |

| 6.6  | Loss breakdown of the (a)ZVS-QSW buck, (b)<br>three-level buck and (c)<br>resonant                           |    |

|      | switched capacitor converters at the nominal operating point of input voltage                                |    |

|      | $V_{\rm IN} = 12$ V, output voltage $V_{\rm OUT} = 4$ V, and output current $I_{\rm OUT} = 10$ A.            | 86 |

| 6.7  | Photograph of the prototype ZVS-QSW buck converter: (a) top view, and (b)                                    |    |

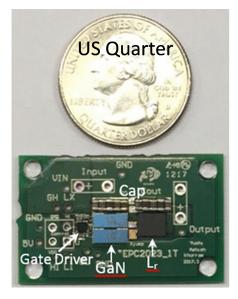

|      | side view. Also shown for size comparison is a US Quarter                                                    | 87 |

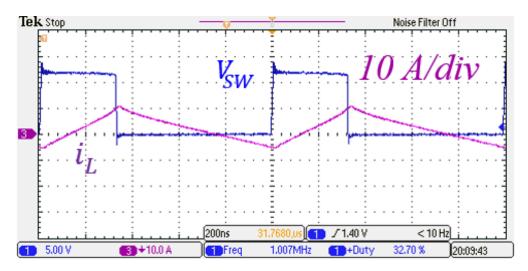

| Measured waveforms of switch node voltage and inductor current when oper-                                                                                   |                                                                                                                 |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|

| ating at input voltage $V_{\rm IN} = 12$ V, output voltage $V_{\rm OUT} = 4$ V, and output                                                                  |                                                                                                                 |  |  |  |

| current $I_{\text{OUT}} = 3.5 \text{ A.} \dots \dots$ | 88                                                                                                              |  |  |  |

| Measured efficiency of the prototype ZVS-QSW buck converter at different                                                                                    |                                                                                                                 |  |  |  |

| input voltage with output voltage $V_{\rm OUT}=4$ V across full load conditions                                                                             | 89                                                                                                              |  |  |  |

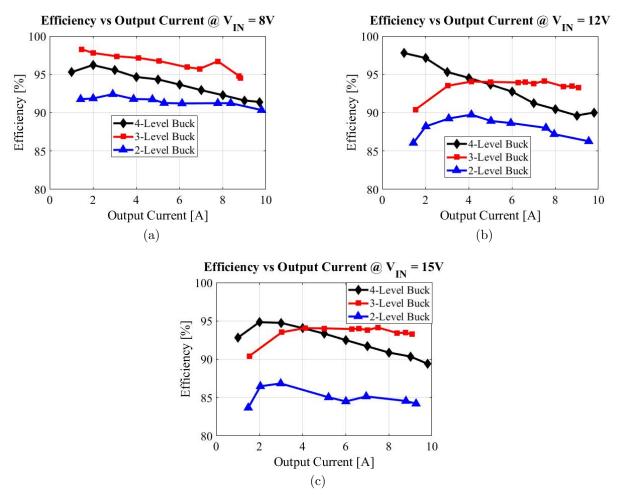

| The measured efficiency of GaN-based 2-level (ZVS-QSW) buck, 3-level buck                                                                                   |                                                                                                                 |  |  |  |

| and 4-level buck converters at different operating conditions over full load                                                                                |                                                                                                                 |  |  |  |

| range: (a) input voltage $V_{\rm IN} = 8$ V, output voltage $V_{\rm OUT} = 4$ V; (b) input                                                                  |                                                                                                                 |  |  |  |

| voltage $V_{\rm IN} = 12$ V, output voltage $V_{\rm OUT} = 4$ V; (c) input voltage $V_{\rm IN} = 15$                                                        |                                                                                                                 |  |  |  |

| V, output voltage $V_{\text{OUT}} = 4$ V                                                                                                                    | 92                                                                                                              |  |  |  |

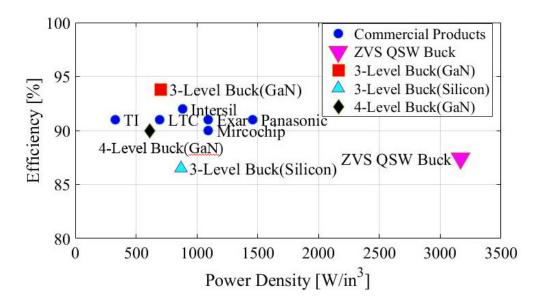

| Comparison of state-of-the-art commercial DC-DC converter with the proto-                                                                                   |                                                                                                                 |  |  |  |

| types proposed in this thesis: ZVS-QSW buck, 3-level buck using GaN tran-                                                                                   |                                                                                                                 |  |  |  |

| sistor, 3-level buck using Silicon MOSFET, 4-level buck using GaN transistor.                                                                               |                                                                                                                 |  |  |  |

| Indicated efficiency is with input voltage of 12 V, output voltage of 4 V and                                                                               |                                                                                                                 |  |  |  |

| output current of 10 A                                                                                                                                      | 93                                                                                                              |  |  |  |

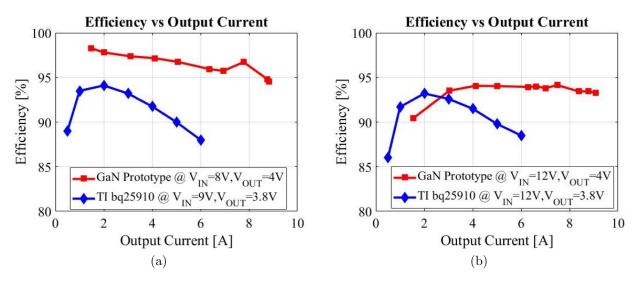

| The efficiency comparison of TI's bq25910 and GaN transistor (EPC2023) $$                                                                                   |                                                                                                                 |  |  |  |

| based prototype for two operating conditions across different load current at                                                                               |                                                                                                                 |  |  |  |

| (a) input voltage $V_{\rm IN} = 8 V$ , output voltage $V_{\rm OUT} = 4 V$ ; (b) input voltage                                                               |                                                                                                                 |  |  |  |

| $V_{\rm IN} = 12 V$ , output voltage $V_{\rm OUT} = 4 V$                                                                                                    | 93                                                                                                              |  |  |  |

|                                                                                                                                                             | ating at input voltage $V_{IN} = 12$ V, output voltage $V_{OUT} = 4$ V, and output<br>current $I_{OUT} = 3.5$ A |  |  |  |

## Chapter 1

### Introduction

### 1.1 Background and Motivation

Nowadays, in the highly competitive consumer electronics market, customers favor thinner cellphones with larger battery capacity. The battery chargers inside cellphones are required to meet increasingly stringent power density requirements, including small printed circuit board (PCB) area and limited component height. These battery chargers also need to maintain very high efficiency, since customers are very sensitive to the heat generated by the conversion power loss. Additionally, this high efficiency must be maintained across a wide range of input voltages, as enabled by the latest USB standard [1]. The new standard allows for fast charging using substantially higher charging power.

The power density of a converter is defined as the power delivered by the converter per unit of its volume. The volume of a switched-mode converter is dominated by its passive energy storage and transformation components, that is capacitors, inductors and transformers. To shrink the volume of the converter and meet the low-profile requirements, small yet efficient planar inductors need to be designed. One way to decrease the size of inductors and capacitors is to increase the switching frequency, which reduces the required inductance and capacitance values. However, increasing the switching frequency exacerbates switching losses, which are proportional to switching frequency [2–4]. Also, as the size of the power converter is reduced, it is more important to achieve high efficiency in order to maintain thermal stability of the converter as the surface area through wich the heat can be extracted reduces [5]. Therefore, the design and optimization of high-power-density converters requires accurately loss and thermal models for its various components.

### 1.2 State of the Art and Thesis Objectives

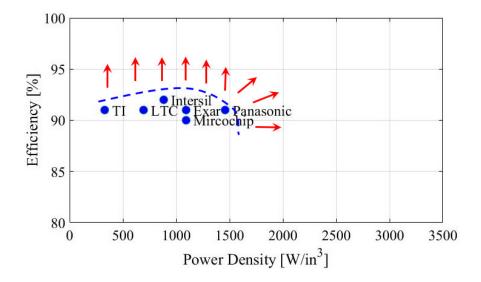

Cellphone battery chargers need to achieve high power density and provide regulation capability, while remaining low profile, highly efficient across wide-range operating conditions in terms of input voltage, output voltage and output power. Conventional dc-dc converters suitable for cellphone battery charging applications do not simultaneously satisfy these three requirements. For instance, [6] achieves high power density and high efficiency, but does not provide the regulation capability. Others [7,8] provide regulation and can achieve relatively high power density, but do not maintain high wide-range efficiency. Enabled by the latest USB standard for fast charging, this battery charger is designed for an input voltage range of 5 V to 20 V, an output voltage range of 3 V to 4.2 V, and a maximum output current of 10 A. Many semiconductor companies have proposed their products of DC-DC converter for this battery charging application, as shown in Fig. 1.1.

Figure 1.1: State-of-the-art commercial DC-DC converters, suitable for cellphone battery charging application. Indicated efficiency is with input voltage of 12 V, output voltage of 4 V and output current of 10 A.

This thesis aims to push the limit of power density and efficiency of battery charger and focus on the design of DC-DC converter that achieves both high power density (including low profile) and high efficiency across a wide range of input voltages. The main challenge is the topology selection and magnetics design. There are so many topologies available for DC-DC converter, and each of them has its own advantages and disadvantages. The magnetics design is even more demanding, since the converter's component height is restricted within 1 mm and the inductor needs to handle large input voltage range (5 V to 20 V) and large output current (10 A). A thorough search of off-the-shelf inductors has been done, as listed in Tale. 1.1. It can be seen that for large current capability (RMS current over 13 A), there is no inductor of height within 1 mm available. Therefore, we have to design the customized inductor, while choosing the proper topology to achieve the goal of high power density and high efficiency.

| Manufacture      | Part Number | Inductance    | I <sub>rms</sub> | Dimension (mm)                |

|------------------|-------------|---------------|------------------|-------------------------------|

| Wurth Eletronics | 732-773-010 | $1 \ \mu H$   | 4 A              | $4 \times 4.5 \times 3.2$     |

| Wurth Eletronics | 732-773-003 | 330 nH        | 10.8 A           | $5.2 \times 5.8 \times 4.5$   |

| Wurth Eletronics | 110-001-150 | $1 \ \mu H$   | 22.5 A           | $11.6 \times 7.8 \times 7.1$  |

| Wurth Eletronics | WW006       | $1 \ \mu H$   | 30 A             | $10 \times 10 \times 8.1$     |

| Coil Craft       | FA2769-AL   | 26 nH         | 5 A              | $3.65 \times 3.65 \times 1.5$ |

| Coil Craft       | XAL4020-221 | 220 nH        | 5 A              | $4.3 \times 4.3 \times 1.8$   |

| Coil Craft       | KA5013-AE   | $1.5 \ \mu H$ | 5 A              | $4.3 \times 4.3 \times 1.8$   |

| Coil Craft       | XEL4012-920 | 92 nH         | 16.2 A           | $4.3 \times 4.3 \times 1.5$   |

| Coil Craft       | XEL3515-720 | 72 nH         | 18 A             | $3.65 \times 3.65 \times 1.5$ |

| Coil Craft       | XEL4030-101 | 100 nH        | 18 A             | $3.65 \times 3.65 \times 1.5$ |

Table 1.1: Commercial Power Inductor Product List

### 1.3 Contributions of the Thesis

This thesis aims to design a low-profile, high-power-density and high-efficiency cellphone battery charger. This converter delivers 40 W across input voltage range of 5 V to 20 V, with output voltage range of 3 V to 4.2 V. Five alternative topologies: zero-voltage switching quasi-square-wave (ZVS-QSW) buck converter, three-level buck converter, resonant switched capacitor converter, reconfigurable hybrid switched capacitor converter and four-level buck converter are analyzed and compared in terms of efficiency and power density in this application.

The design methodology for these five converter topologies presented here utilizes the augmented state-space modeling approach to predict converter waveforms with high accuracy and computational efficiency. Conventional analytical method uses small-ripple approximation assuming that the capacitor voltage ripples are negligible, which sacrifices the accuracy. For topology such as resonant switched capacitor converter, it's very difficult to get the switch and inductor current analytical expression with small-ripple approximation. Another common way of predicting the converter waveforms is to utilize Spice simulation tools, such as LTSpice, Pspice, PLECS. With refined component model provided, the simulation results can be highly accurate. However, starting from initial conditions, the simulation takes considerable computation time to get settled and obtain the steady-state waveforms of the converter. This thesis introduces the augmented state-space modeling to predict steady-state waveforms, while requiring only 1/60 of the computation time. This enables a comprehensive optimization of the converters design by sweeping parameters such as switching frequency and inductor geometry over wide ranges.

Next, this thesis introduces loss model for the DC-DC converter, transistor loss, inductor loss, capacitor loss and trace loss. The transistor loss includes gating loss, switching loss and conduction loss. The planar inductor loss includes winding loss and core loss. To get a more accurate loss model for GaN transistors and inductor, this thesis utilizes converter waveforms measurement and component thermal measurement to calibrate the dynamic on-resistance of the GaN switch at high frequency(MHz) and planar inductor steinmetz parameters operated at large flux density( $B_{max} > 500 \text{ mT}$ ) scenario. Finite-Element-Analysis simulation tool Ansys Maxwell has also been used to calculate the inductor ac resistance and PCB trace loss. With the modeling method and refined loss model, this thesis proposes converter design for three application scenarios: 2-to-1 conversion ratio, 3-to-1 conversion ratio, and extreme-power-density design.

The three-level buck converter achieves highest efficiency at 2:1 conversion ratio scenario (input voltage  $V_{\rm IN} = 8 V$ , output voltage  $V_{\rm OUT} = 4 V$ ). The augmented state-space modeling has been utilized to predict the three-level buck converter waveforms, check the zero-voltage-switching (ZVS), and calculate the converter losses. To achieve high power density, a custom-shaped planar PCB-integrated inductor is designed, whose geometry is optimized using 3D finite-element analysis (FEA) to minimize losses. Two prototype threelevel buck converter have been built. One prototype using EPC2023 GaN device with a PCB area of  $358 \text{ mm}^2$  and component height of 1 mm designed is built and tested. This prototype converter achieves a peak efficiency of 98.5% at 2:1 conversion ratio and high overall efficiency at other operating conditions with a power density of 704  $W/in^3$ . The other prototype using low-voltage silicon MOSFET (CPF03433) with a PCB area of 310  $\rm mm^2$  is also built and tested. For GaN device prototype, to maximize efficiency, the converter is designed to achieve zero-voltage switching (ZVS) at light-to-medium loads, while sacrificing ZVS to reduce transistor conduction and inductor losses. For low-voltage silicon device proto type, ZVS is achieved across all load condition at  $(V_{IN} = 12 V, V_{OUT} = 4 V)$  to reduce the voltage stress on the device. Also, The on-resistance and output capacitance of the Silicon MOSFET (CPF03433) have been calibrated with experimental results, and the comparison of GaN transistor(EPC2023) GaN and Silicon MOSFET (CPF03433) has also been done.

The four-level buck converter and reconfigurable hybrid switched capacitor converter using six switches achieve high efficiency when the input voltage is high. The four-level buck converter reaches its maximum efficiency at 3:1 conversion ratio (input voltage  $V_{\rm IN} = 12 V$ , output voltage  $V_{\rm OUT} = 4 V$ ), due to its minimized inductor current ripple. The augmented state-space modeling method is utilized to accurately predict the two types of converters' waveforms and calculate the loss. Also, a custom-shaped planar PCB-integrated inductor is designed to achieve high power density and high efficiency. Based on the analysis, a prototype of four-level buck converter with EPC2023 GaN transistors has been built and tested.

Finally, this thesis introduces the design of a extreme-power-density battery charger. Specifically, the converter is required to deliver a maximum output power of 40 W across a 4:1 input voltage range, with its PCB footprint limited to 80 mm<sup>2</sup> and its component height limited to 1 mm. Due to the stringent area (80mm<sup>2</sup>) requirement, three alternative topologies a zero-voltage-switching quasi-square-wave (ZVS-QSW) buck converter, a three-level buck converter, and a resonant switched capacitor converter are analyzed, designed and compared in terms of efficiency and power density in this application. Four-level buck converter and reconfigurable hybrid switched capacitor converter are not considered in this design for their overabundant switches quantity. The inductors in the three converter topologies are designed as planar PCB-integrated structures with custom-shaped ferrite cores, optimized using a 3D finite-element analysis (FEA) tool. The ZVS-QSW buck converter is predicted to achieve the highest efficiency under the specified area and height constraints. A prototype 40-W 1-MHz buck converter with a PCB area of 79.6 mm<sup>2</sup> and component height of 1 mm is built and tested. The prototype converter achieves a peak efficiency of 96.7% and a power density of 3230 W/in<sup>3</sup>.

### 1.4 Thesis Organization

The remainder of this thesis is organized as follows: Chapter 2 introduces five alternative topologies: zero-voltage switching quasi-square-wave (ZVS-QSW) buck converter, threelevel buck converter, resonant switched capacitor converter, reconfigurable hybrid switched capacitor converter and four-level buck converter for this battery charging application. The operation principle, advantage and disadvantage of each topology is stated in Chapter 2. Chapter 3 presents two design techniques, including augmented state-space modeling method and loss model for the dc-dc converter with calibrated dynamic on resistance for GaN device and Steinmetz parameters for 3F46 ferrite material to accurately predict the converter waveforms and estimate its loss. Chapter 4 describes a low-profile, high-power-density, and high-efficiency three-level buck converter fit for 2:1 conversion ratio. Two prototype of threelevel buck converter have been built and tested, including one using GaN switches and the other using silicon MOSFET. Chapter 6 presents a high-efficiency four-level buck converter optimized for 3:1 conversion ratio application, with the prototype built. Chapter 7 shows the design of very tiny battery charger with PCB footprint limited to 80 mm<sup>2</sup>. Finally, the summary and conclusions of the thesis are presented in Chapter 8.

# Chapter 2

### **Alternative Battery Charger Topologies**

The stringent area and height specifications of the battery charging application considered in this thesis favor dc-dc converter topologies with limited switch count and small passive (inductor and capacitor) volume. This thesis considers five dc-dc converter topologies, described below. They are zero-voltage switching quasi-square-wave (ZVS-QSW) buck converter, three-level buck converter, resonant switched capacitor converter, four-level buck converter and reconfigurable hybrid switched capacitor converter. Advantages and disadvantages of each topology have been stated. The operation principle of each topology is also described in this chapter.

### 2.1 Zero-Voltage Switching Quasi-Square-Wave Buck Converter

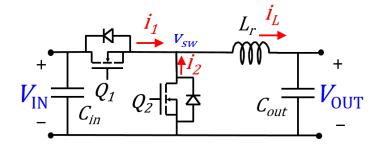

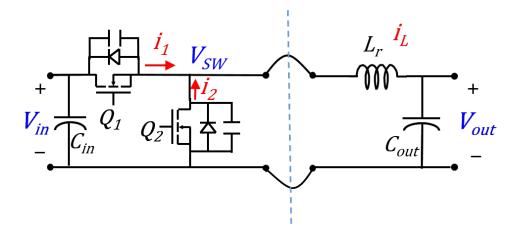

Figure 2.1: Zero-Voltage Switching Quasi-Square-Wave Buck (ZVS-QSW) converter topology.

The synchronous buck converter, shown in Fig. 2.1, utilizes only two switches, one

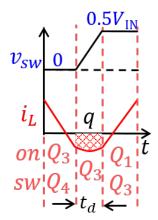

inductor and two capacitors, and is hence potentially volume-efficient. The size of this converters passive components can be reduced by operating at high switching frequencies. To achieve high efficiency at these high frequencies, a ZVS-QSW version of the buck converter can be employed, in which the converters inductance is small enough to allow the inductor current to go negative, enabling ZVS of the high-side transistor [9]. Similar to its conventional counterpart, the ZVS-QSW buck converter can regulate its output voltage using duty-ratio control. However, the increase in inductor current ripple required to achieve ZVS introduces additional inductor winding losses and transistor conduction losses. To maintain high efficiency in the presence of this tradeoff, a methodology to optimize the design of a ZVS-QSW buck converter in terms of its switching frequency and inductance is described in later chapter.

### 2.2 Three-Level Buck Converter

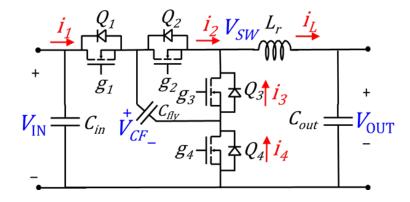

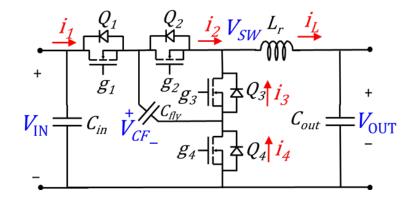

Figure 2.2: The three level buck converter topology.

The topology of a three-level buck converter is shown in Fig. 2.2. Compared to the synchronous buck converter, this converter utilizes three additional components two switches and a flying capacitor. The output voltage of this converter is also regulated using duty-ratio control. As can be seen from Fig. 2.3, the switches  $Q_1$  and  $Q_4$  are operated in a complementary manner with a duty ratio D. Similarly, the switches  $Q_2$  and  $Q_3$  operate in a complementary fashion with the same duty ratio. These two groups of switches,  $(Q_1, Q_4)$

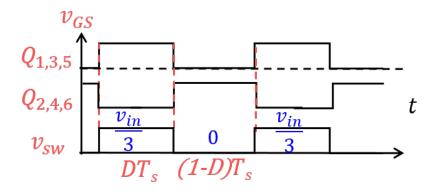

Figure 2.3: Gate signals of  $Q_1, Q_2, Q_3, Q_4$  switch-node voltage and inductor current for duty ratio D < 0.5, D = 0.5, and D > 0.5.

) and  $(Q_2, Q_3)$ , are switched with a time-shift of half a switching period  $\frac{T_s}{2}$ . The output voltage of the three-level buck converter is given by:

$$V_{\rm OUT} = DV_{\rm IN} \tag{2.1}$$

Here,  $V_{\rm IN}$  and  $V_{\rm OUT}$  are the dc input and output voltages of the converter, respectively. With the switches operated as described above, the three-level buck converter operates in two different modes, as shown in Fig. 2.3: when the required conversion ratio  $(V_{\rm OUT}/V_{\rm IN})$ is less than half, the duty ratio D as computed using (2.1) is also less than half, and the switch-node voltage  $v_{sw}$  alternates between 0 and  $V_{\rm IN}/2$ . When the conversion ratio, and hence the duty ratio D, is greater than half, the switch-node voltage alternates between  $V_{\rm IN}/2$  and  $V_{\rm IN}$ . In applications where a wide range of conversion ratios is required, such as the battery charging application considered here, this multi-mode operation of the three-level buck converter reduces the volt-seconds applied to the inductor, potentially reducing its losses and size. Furthermore, by transferring some of the losses to the two additional transistors, this converter can offer a better thermal distribution than a synchronous buck converter. However, due to its three additional components compared to the buck converter, the three-level buck converter is more challenging to design for a high-power-density application, such as the one considered here. The design of a three-level buck converter is optimized and its performance compared to the ZVS-QSW buck converter in Chapter 6. Additional details of the operation and control of the three-level buck converter, including its soft-switching capabilities, can be found in [9–13].

### 2.3 Resonant Switched Capacitor Converter

Figure 2.4: Four-switch ladder resonant switched capacitor converter topology.

Switched capacitor converters are a popular solution for high power density converter design, since these converters do not utilize any magnetic components. However, conventional switched capacitor converters are efficient only near the fixed conversion ratios inherent to their topologies. Adding a small appropriately-located inductor to a switched capacitor converter enables it to provide a wider range of conversion ratios while maintaining high efficiency [14–20]. Among such hybrid switched capacitor topologies, the four-switch ladder resonant switched capacitor (ReSC) converter, shown in Fig. 2.4, is a suitable alternative

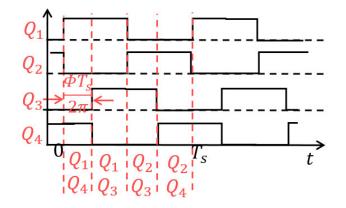

Figure 2.5: Gate signals of  $Q_1, Q_2, Q_3, Q_4$  of the four-switch ladder resonant switched capacitor converter.

for the volume-limited application considered here. The output voltage of this converter can be regulated by controlling the phase-shift between its top and bottom half-bridges (as shown in Fig. 2.5), and/or by controlling its switching frequency [15, 16]. Using state plane analysis, and assuming lossless power conversion, the output voltage of this converter can be expressed as:

$$V_{\rm OUT} = \frac{V_{\rm IN} F_s}{2\pi Z_0} \left[ \sin\left(\frac{\Phi}{F_s}\right) \tan\left(\frac{\pi}{2F_s}\right) - 1 \right] R \tag{2.2}$$

Here,  $F_s$  is the normalized switching frequency of the converter, given by  $F_s = \frac{J_s}{f_0}$ , where  $f_s$  is the switching frequency and  $f_0$  is the resonant frequency of the tank formed by the inductor  $L_r$  and flying capacitor  $C_r$  in the ReSC converter of Fig. 2.4;  $Z_0$  is the characteristic impedance of this resonant tank;  $\Phi$  is the phase shift between the top and bottom half-bridges of the converter; and R is the value of the resistance modeling the converters load.

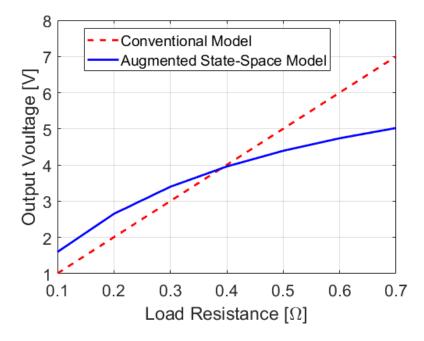

In practice, owing to the on resistance of the switches and inductor, the actual output voltage may deviate substantially from the ideal value given in (2.2). The augmented statespace modeling can be applied in the case of the resonant switched capacitor converter, wherein circuit behavior is conventionally predicted assuming lossless power conversion, as stated in (2.2). However, the augmented state-space analysis utilized here demonstrates that the output voltage of this converter can be substantially different from that predicted by the conventional analysis, as shown in Fig. 2.6.

Figure 2.6: Comparison between the output voltage of the four-switch ladder resonant switched capacitor converter, as predicted by the conventional lossless analysis and augmented state-space analysis including losses.

Compared to the ZVS-QSW buck and three-level buck converters, the resonant switched capacitor converter requires a significantly smaller inductance. However, at conversion ratio other than 2:1, the energy is circulating in the converter tank thus the peak and RMS currents are significantly higher than those in the buck and three-level buck converters owing to its resonant nature. Thus this converter is suitable for application with fixed conversion ratio. The design of a four-switch ladder resonant switched capacitor converter is optimized and its performance is compared to the other two candidate topologies in later chapter. Additional details of the operation and control of this converter can be found in [14–18].

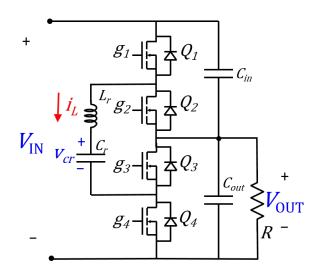

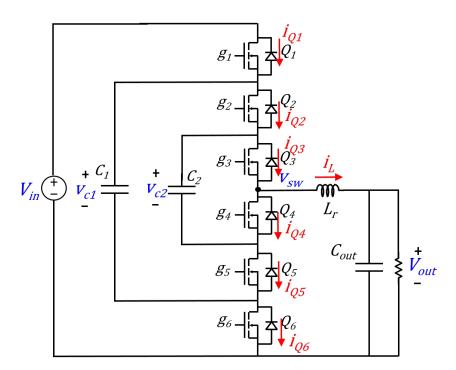

Figure 2.7: Four-level buck converter topology.

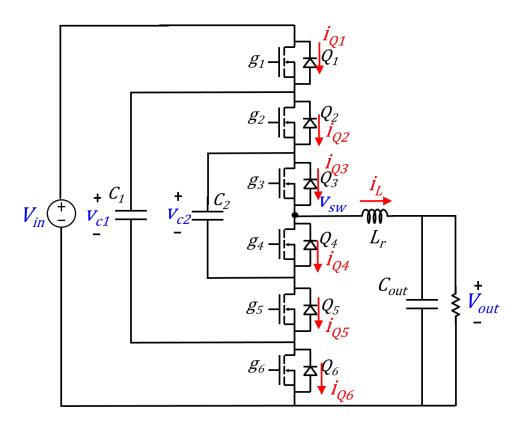

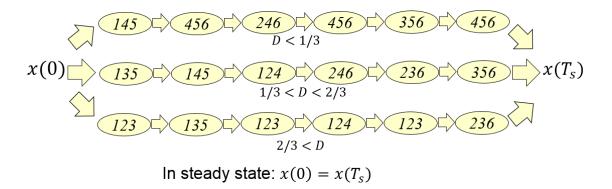

# 2.4 Four-Level Buck Converter

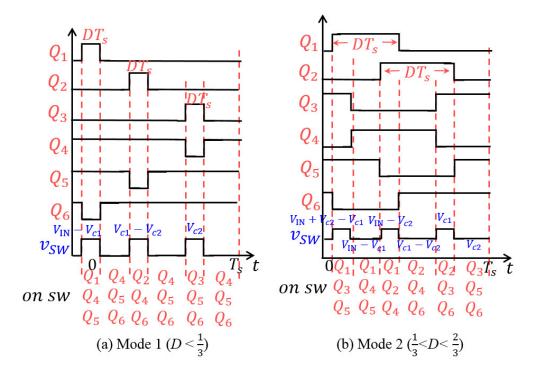

The topology of a four-level buck converter is shown in Fig. 2.7. Compared to the three-level buck converter, this converter utilizes three additional components two switches and a flying capacitor. The output voltage of this converter is also regulated using duty-ratio control. As can be seen from Fig. 2.8, the switches  $Q_1$  and  $Q_6$  are operated in a complementary manner with a duty ratio D. Similarly, the switches  $Q_2$ ,  $Q_5$  and  $Q_3$ ,  $Q_4$  operate in a complementary fashion with the same duty ratio. These three groups of switches,  $(Q_1,Q_6), (Q_2,Q_5)$  and  $(Q_3,Q_4)$  are switched with a mutual time-shift of a third of a switching period  $\frac{T_s}{3}$ . The output voltage of the four-level buck converter is given by:

$$V_{\rm OUT} = D V_{\rm IN} \tag{2.3}$$

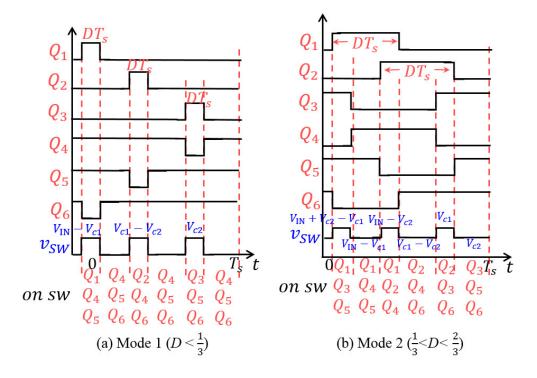

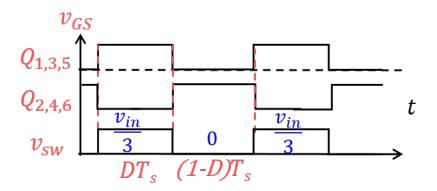

Figure 2.8: Gate signals of  $Q_1, Q_2, Q_3, Q_4, Q_5, Q_6$  and switch-node voltage of four level buck converter when duty ratio D < 1/3 and 1/3 < D < 2/3.

Here,  $V_{\rm IN}$  and  $V_{\rm OUT}$  are the dc input and output voltages of the converter, respectively.  $V_{c1} = 2/3V_{\rm IN}, V_{c2} = V_{\rm IN}/3$ . With the switches operated as described above, the fourlevel buck converter operates in three different modes: when the required conversion ratio  $(V_{\rm OUT}/V_{\rm IN})$  is less than 1/3, the duty ratio D as computed using (2.3) is also less than 1/3, and the switch-node voltage  $v_{sw}$  alternates between 0 and  $V_{\rm IN}/3$ . When the conversion ratio, and hence the duty ratio 1/3 < D < 2/3, the switch-node voltage alternates between  $V_{\rm IN}/3$ and  $2/3V_{\rm IN}$ , as shown in Fig. 2.8. When the conversion ratio, and hence the duty ratio D > 2/3, the switch-node voltage alternates between  $2/3V_{\rm IN}$  and  $V_{\rm IN}$ .

The inductor switching node  $V_{sw}$  varies from 0,  $V_{IN}/3$ ,  $2/3V_{IN}$  and  $V_{IN}$  for four levels. Compared with three-level buck converter, the four-level buck converter further reduces the voltage stress on the inductor and also triple the switching node frequency, thus minimizes the inductor current ripple and the volt-seconds applied to the inductor, potentially reducing its losses and size. But the extra two switches result in more transistor conduction loss and occupies more area. Therefore the four level buck converter is suitable for application with extremely small inductor, and not sensitive to the switches areas. Additional details of the operation and control of the four-level buck converter, can be found in [21–23]. More details of four-level buck converter, including augmented state-space modeling and loss model analysis and optimization will be provided in the Chapter 6.

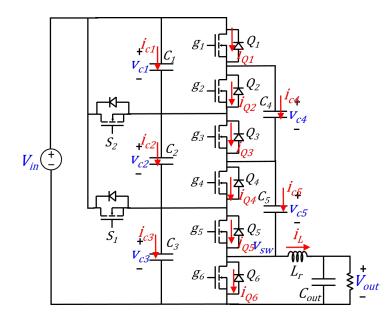

# $V_{in} \stackrel{t}{=} \qquad \begin{array}{c} i_{c1} & g_{1} \\ V_{c1} \\ V_{c1} \\ V_{c1} \\ g_{2} \\ V_{c2} \\ g_{3} \\ V_{c2} \\ g_{3} \\ V_{c2} \\ g_{4} \\ V_{c4} \\ g_{5} \\ V_{c4} \\ V_{c5} \\ V_{c6} \\ V_{c6} \\ V_{c5} \\ V_{c5} \\ V_{c6} \\ V_{c6} \\ V_{c5} \\ V_{c5} \\ V_{c6} \\ V_{c5} \\ V_{c6} \\ V_{c5} \\ V_{c5} \\ V_{c6} \\ V_{c6} \\ V_{c5} \\ V_{c6} \\ V_{c6} \\ V_{c5} \\ V_{c6} \\ V_{c5} \\ V_{c6} \\ V_{c5} \\ V_{c6} \\ V_{c6} \\ V_{c5} \\ V_{c6} \\ V_{$

### 2.5 Reconfigurable Hybrid Switched Capacitor Converter

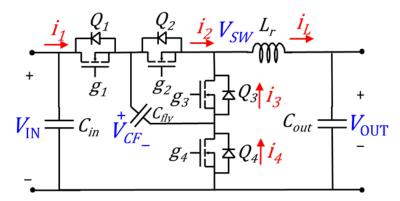

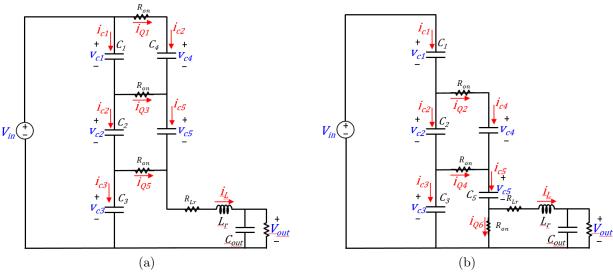

Figure 2.9: Reconfigurable hybrid switched capacitor converter topology.

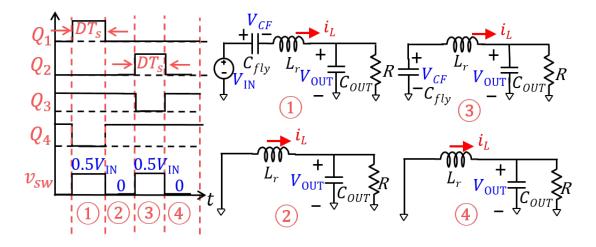

This thesis also presents a new reconfigurable hybrid switched capacitor converter topology shown in Fig. 2.9. This converter is designed for various step-down ratio scenarios and operates in three different modes to achieves favorable trade-off between switch losses and inductor losses. When  $V_{\rm OUT} < \frac{V_{\rm IN}}{3}$ , mode selection switches  $S_1$  and  $S_2$  are off, These three groups of switches,  $(Q_1,Q_2)$ ,  $(Q_3,Q_4)$  and  $(Q_5,Q_6)$  operates in complimentary mode, with duty ration D. Three capacitors  $C_1$ ,  $C_2$ , and  $C_3$  equally split the input voltage  $V_{\rm IN}$ , so

Figure 2.10: Gate signals of  $Q_1, Q_2, Q_3, Q_4, Q_5, Q_6$  and switch-node voltage of reconfigurable hybrid switched capacitor converter when output voltage  $V_{\text{OUT}} < \frac{V_{\text{IN}}}{3}$ .

that  $V_{c1} = V_{c2} = V_{c3} = \frac{V_{IN}}{3}$ .  $V_{sw}$  toggles between 0 and  $\frac{V_{IN}}{3}$  with a duty ratio of D, as shown in Fig. 2.10. The output voltage of the reconfigurable hybrid switched capacitor converter is given by:

$$V_{\rm OUT} = D \frac{V_{\rm IN}}{3} \tag{2.4}$$

When  $\frac{V_{\text{IN}}}{3} < V_{\text{OUT}} < \frac{1}{2}V_{\text{IN}}$ , mode selection switch  $S_1$  is off,  $S_2$  is on and  $(Q_1,Q_2)$  are off. Two groups of switches,  $(Q_3,Q_4)$  and  $(Q_5,Q_6)$  operate in complimentary mode, with duty ration D. Two capacitors  $C_2$ , and  $C_3$  equally splits the input voltage  $V_{\text{IN}}$ , so that  $V_{c2} = V_{c3} = \frac{V_{\text{IN}}}{2}$ .  $V_{sw}$  toggles between 0 and  $\frac{V_{\text{IN}}}{2}$  with a duty ratio of D. The output voltage of the reconfigurable hybrid switched capacitor converter is given by:

$$V_{\rm OUT} = D \frac{V_{\rm IN}}{2} \tag{2.5}$$

When  $\frac{V_{\text{IN}}}{2} < V_{\text{OUT}} < V_{\text{IN}}$ , mode selection switch  $S_2$  is off, and  $S_1$  is on.  $(Q_5, Q_6)$  operates in complimentary mode, with duty ratio D. The input voltage  $V_{\text{IN}}$  is applied on the  $C_3$ , therefore  $V_{sw}$  toggles between 0 and  $V_{\text{IN}}$  with a duty ratio of D. The output voltage of the reconfigurable hybrid switched capacitor converter is given by:

$$V_{\rm OUT} = D V_{\rm IN} \tag{2.6}$$

Depending on the output voltage and input voltage ratio, this reconfigurable hybrid switched capacitor converter operates in three modes and  $V_{sw}$  toggles between  $V_{IN}$ ,  $V_{IN}/2$ , or  $V_{IN}/3$  and 0. This multi-mode operation mitigates inductor volt-seconds and loss. Compared with four-level buck converter, it uses less switches in series when  $D = V_{IN}/V_{OUT}$  is high, thus reduce the switch conduction loss. More details regarding this reconfigurable hybrid switched capacitor converter, including its loss modeling, optimization, and a comparison with the four-level buck converter will be provided in the Chapter 5.

# Chapter 3

#### **Design Techniques**

To evaluate and compare the performance of the different topologies identified in Chapter 2, design techniques to accurately estimate the performance of the converter are needed. This chapter discusses the two design techniques used in this thesis. One is the augmented state-space modeling method to accurately calculate the converter waveforms, such as inductor current and capacitor voltage; the other is loss model for the dc-dc converter, specifically with calibrated GaN device dynamic on-resistance and Steinmetz parameters for 3F46 ferrite material. Based on these two design techniques, the efficiency and loss breakdown of converters with different topologies, including QSW buck, three-level buck, reconfigurable hybrid switched capacitor and four level buck converter, over full input voltage range is predicted and presented in the later section.

# 3.1 Augmented State-Space Modeling

Commonly, there are two ways to predict the waveforms of a converter. Conventional analytical method uses small-ripple approximation, which assumes that the capacitor voltage and inductor current ripples are small enough. This method is widely used in design, as it requires the designer to fully understand how the converter operates and how the parameters, such as frequency, phase shift and duty cycle, change the waveforms of the converter. There are two main drawback of the analytical method. One is that sometimes it sacrifices accuracy to get analytically solvable equations. For example, in PWM converters, it neglects voltage ripple on the capacitor. The other issue is that in resonant and switched capacitor converter, the inductor current or capacitor voltage analytical expressions are very complicated and even sometimes impossible to get. Another common way to predict the converter waveforms is utilizing Spice simulation tools, including LTSpice, Pspice, PLECS and so on. The main advantage of the simulation method is its high accuracy. With accurate component model provided, the simulation results match the experimental results pretty well. The drawback of the simulation method is that it consumes considerable computation time and resources. To obtain the steady-state waveforms of the converter, the Spice simulation takes substantial time from initial condition to get settled. In cases when numerous values need to be swept, the total computation time of simulation might be unacceptable.

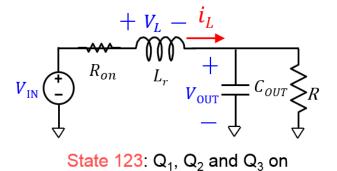

Figure 3.1: The three-level topology.

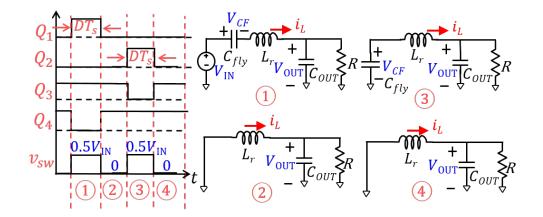

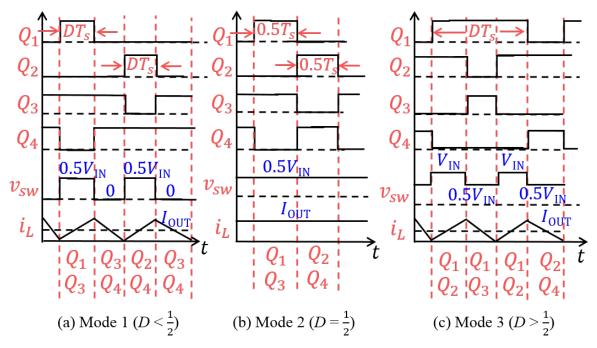

In this thesis, all the converter topologies utilize the augmented state-space modeling approach to predict converter waveforms with high accuracy and computational efficiency. A three-level buck converter is shown in Fig. 3.1 as an example.

The three-level buck converter has three modes (D < 0.5, D = 0.5, D > 0.5). In each mode, the converter's operation can be described using a sequence of equivalent linear circuits, with each equivalent circuit corresponding to a particular configuration (on/off) of the switches. As an example, the operation and corresponding equivalent circuits of the three-level buck converter operating in the D < 0.5 mode are shown in Fig. 3.2. To analyze these circuits, three state variables are considered: flying capacitor voltage  $V_{CF}$ , output

Figure 3.2: Operation and corresponding states of three level buck converter when D < 0.5.

voltage  $V_{OUT}$  and inductor current  $i_L$  and state equations are written for each equivalent circuit. For instance, for the first equivalent circuit, the state bn-space equation is given by:

$$\begin{bmatrix}

\dot{V_{CF}} \\

\dot{V_{OUT}} \\

\dot{i_L}

\end{bmatrix} = \begin{bmatrix}

0 & 0 & 1/C_f \\

0 & -1/(RC_{OUT}) & 1/C_{OUT} \\

-1/L_r & -1/L_r & -R_{on}/L_r

\end{bmatrix}

\begin{bmatrix}

V_{CF} \\

V_{OUT} \\

\dot{i_L}

\end{bmatrix} + \begin{bmatrix}

0 \\

0 \\

V_{IN}/L_r

\end{bmatrix} (3.1)$$

Here  $L_r$  is the inductance,  $C_f$  is the flying capacitance,  $C_{OUT}$  is the output capacitance,  $V_{\rm IN}$  is the input voltage, R is the load resistance, and  $R_{tot}$  is the sum of the on-resistance of two of the converters switches, the ac resistance of the inductor and the equivalent series resistance (ESR) of the flying capacitor. Similar state-space equations can be written for the other three equivalent circuits. Therefore the converter behavior can be expressed in state-space equation as:

$$\dot{x} = Ax + B \tag{3.2}$$

For each state, there is  $A_1, A_2...A_4, B_1, B_2...B_4$  state matrix. For D < 0.5 mode, the state matrix A and B can be expressed as:

$$A_{1} = \begin{bmatrix} 0 & 0 & \frac{1}{C_{f}} \\ 0 & \frac{-1}{RC_{OUT}} & \frac{1}{C_{OUT}} \\ \frac{-1}{L_{r}} & \frac{-1}{L_{r}} & \frac{-R_{on}}{L_{r}} \end{bmatrix}, A_{2} = \begin{bmatrix} 0 & 0 & 0 \\ 0 & \frac{-1}{RC_{OUT}} & \frac{1}{C_{OUT}} \\ 0 & \frac{-1}{L_{r}} & \frac{-R_{on}}{L_{r}} \end{bmatrix}$$

(3.3)

$$A_{3} = \begin{bmatrix} 0 & 0 & \frac{1}{C_{f}} \\ 0 & \frac{-1}{RC_{OUT}} & \frac{1}{C_{OUT}} \\ \frac{1}{L_{r}} & \frac{-1}{L_{r}} & \frac{-R_{on}}{L_{r}} \end{bmatrix}, A_{4} = \begin{bmatrix} 0 & 0 & 0 \\ 0 & \frac{-1}{RC_{OUT}} & \frac{1}{C_{OUT}} \\ \frac{-1}{L_{r}} & \frac{-1}{L_{r}} & \frac{-R_{on}}{L_{r}} \end{bmatrix}$$

(3.4)

$$B_{1} = \begin{bmatrix} 0 \\ 0 \\ \frac{V_{IN}}{L_{r}} \end{bmatrix}, B_{2} = \begin{bmatrix} 0 \\ 0 \\ 0 \\ 0 \end{bmatrix}, B_{3} = \begin{bmatrix} 0 \\ 0 \\ 0 \\ 0 \end{bmatrix}, B_{4} = \begin{bmatrix} 0 \\ 0 \\ \frac{V_{IN}}{L_{r}} \end{bmatrix}$$

(3.5)

Once the state matrix is obtained based on the operation of the converter, the state variable x in time domain can be solved as:

$$x(t) = e^{A_i(t-t_{i-1})} x_{t_{i-1}} + \int_{t_{i-1}}^t e^{A_i(t-\tau)} B_i d\tau$$

(3.6)

Here,  $t_{i-1}$  is the time at the end of (i-1)-th mode.  $x_{t_{i-1}}$  is the state variable at the end of the (i-1)-th mode, that is the initial state variable for the i-th mode. Using (3.6), the state variable at the end of each mode can be expressed as:

$$x_{i} = e^{A_{i}d_{i}T_{s}}x_{i-1} + \int_{t_{i-1}}^{t_{i}} e^{A_{i}(t-\tau)}B_{i}d\tau = \Phi_{i}x_{i-1} + \Gamma_{i}$$

(3.7)

where  $d_i$  is the duty ratio of *i*-th mode,  $T_s$  is the converter's switching period.  $t_i$  is the time at the end of the i-th mode,  $\Phi_i = e^{A_i d_i T_s}$  is the state-transition matrix for the i-th mode, and  $\Gamma_i$  is the term with integration and accounts for the effect of the input variable on the evolution of states. This involves lots of matrix integration and inversion, which takes tremendous amount of computation effort and time. To solve this issue, the augmented state-space modeling approach introduced in [24] is used in this thesis. The state variable and system matrix are augmented as follows:

$$\hat{x} = \begin{bmatrix} x \\ 1 \end{bmatrix}$$

(3.8)

$$\hat{A}_i = \begin{bmatrix} A_i & B_i \\ \Theta & 0 \end{bmatrix}$$

(3.9)

Here  $\Theta$  is the zero row-vector of length equal to the size of the system matrix. A new state equation can now be written for the augmented system, and the solution be obtained as:

$$\dot{\hat{x}} = \hat{A}_i \hat{x} \tag{3.10}$$

$$\hat{x}(t) = e^{\hat{A}_i(t-t_{i-1})} \hat{x}_{i-1} = \hat{\Phi}_i \hat{x}_{i-1}$$

(3.11)

Here  $\hat{\Phi}_i = e^{\hat{A}_i d_i T_s}$  is the augmented state-transition matrix for the *i*-th mode. As shown in Fig. 3.2, in one steady-state period,  $0 < t < T_s$ , the converter goes through four states, and the variable *x* value backs to its original value:

$$\hat{x}(t_0 + T_s) = \hat{\Phi}_m \hat{\Phi}_{m-1} \cdots \hat{\Phi}_1 \hat{x}(t_0) = \hat{x}(t_0)$$

(3.12)

At  $t = t_0$ , the state variable x value can be solved as:

$$x(t_0) = (I^n - \Phi_{tot})^{-1} \Gamma_{tot}$$

(3.13)

Where  $\Phi_{tot} = \Phi_m \Phi_{m-1} \cdots \Phi_1$  and  $\Gamma_{tot} = \Phi_m \Phi_{m-1} \cdots \Phi_2 \Gamma_1 + \cdots \Phi_m \Gamma_{m-1} + \Gamma_m$ . The  $\Phi_m$ and  $\Gamma_m$  represent the state-transition matrix and integration of *m*-th mode. In each mode, the state variable can be expressed as:  $x_{t_1} = \hat{\Phi}_1 x(t_0), x_{t_2} = \hat{\Phi}_2 x(t_1) \dots$  and  $x_{t_m} = \hat{\Phi}_m x(t_{m-1})$ . The state variable *x* in time domain of each mode can be solved as :  $x_{t_1}(t) = e^{\hat{A}_1 t_1 t} x_{t_0}$ ,  $x_{t_2}(t) = e^{\hat{A}_2 t_2 t} x_{t_1} \dots$  and  $x_{t_m}(t) = e^{\hat{A}_m t_m t} x_{t_{m-1}} \dots x_{t_i}$  is the state variable at the end of the (*i*-1)-th mode, that is the initial state variable for the *i*-th mode. Therefore, the state variable x(t) in the one steady-state switching period can be obtained as:

$$x(t) = [x_{t_1}(t), x_{t_2}(t) \cdots x_{t_m}(t)]$$

(3.14)

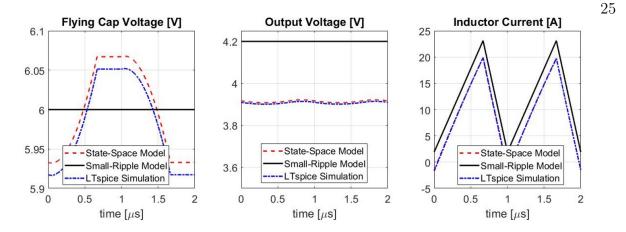

Using this approach, the periodic steady-state waveforms of the three-level buck converter can be directly predicted without need to go through the startup transients (as required in a circuit simulator like Spice), and without the need for matrix integration and inversion steps (which are required in other state-space based modeling techniques). Hence, this approach is computationally efficient. Furthermore, it predicts the converters waveforms with a high degree of accuracy, as shown Fig. 3.3, which compares example waveforms of the three-level buck converter as predicted by the augmented state-space modeling, LTspice simulations, and the conventional small-ripple approximation [25]. As can be seen, unlike waveforms predicted by small-ripple approximation, the augmented state-space predicted waveforms are in excellent agreement with the LTspice simulated waveforms, while requiring only 1/60 of the computation time. This enables comprehensive optimization of the converters design by sweeping parameters such as switching frequency and passive component values over wide ranges.

#### 3.2 Loss Models for the DC-DC Converter

The loss model plays an important role in the power converter design. An accurate loss model helps to predict the loss distribution and performance of a converter, determine the suitable topology among the various candidates, and optimize the design parameters, such as switching frequency and components selection. In this high-power-density cellphone charger application where the total volume is so limited and the components, including switches, capacitor and inductor are so compact, an accurate loss model is even more in need. This

Figure 3.3: Comparison between example waveforms of three-level buck converter as predicted by augmented state-space modeling, small-ripple approximation and LTSpice simulations at input voltage  $V_{\rm IN} = 12 V$ , output voltage  $V_{\rm OUT} = 4 V$ , and output current  $I_{\rm OUT} = 10 A$ .

section is focused on the loss model for GaN transistors switching at high frequency (MHz) and planar inductor operated at large flux density ( $B_{max} > 500 \text{ mT}$ ) scenario. By using both converter waveforms measurement and component thermal measurement, a refined loss model of GaN devices and planar inductor is presented.

# 3.2.1 Theoretical Loss Model for the DC-DC Converter

The loss model of a switch-mode power converter includes three major parts: transistor loss, inductor loss, capacitor loss and trace loss:

$$P_{total} = P_{trans} + P_{ind} + P_{cap} + P_{trace} \tag{3.15}$$